# KARPAGAM ACADEMY OF HIGHER EDUCATION

COIMBATORE-21 Faculty of Engineering Department of Electronics and Communication Engineering

#### Lecture plan

# NAME OF THE STAFF: Dr.N.Rajalakshmi

- DESIGNATION : ASSISTANT PROFESSOR

- CLASS : B.E-IV YEAR ECE

SUBJECT : EMBEDDED SYSTEMS

SUBJECT CODE : 14BEECE19

| S.No. | TOPICS TO BE COVERED                                                                    | TIME         | TEACHING AIDS    |

|-------|-----------------------------------------------------------------------------------------|--------------|------------------|

|       |                                                                                         | DURATION     |                  |

|       | UNIT-I INTRODUCTION TO E                                                                | MBEDDED SY   |                  |

| 1     | Introduction                                                                            | 1            | T1-p.no 3-7      |

| 2     | Definition and Classification                                                           | 1            | T1-p.no 52       |

| 3     | Overview of Processors and hardware units in an embedded system                         | 2            | T1-p.no 10-19    |

| 4     | Software embedded into the system                                                       | 2            | T1-p.no 19-23    |

| 5     | Exemplary Embedded Systems –<br>Embedded Systems on a Chip (SoC)                        | 1            | T1-p.no 29-30    |

| 6     | use of VLSI designed circuits                                                           | 1            | T1-p.no 30-32    |

| 7     | Tutorial                                                                                | 1            |                  |

|       | Total (Theory + Tutorial)                                                               | 9Hrs (8+1)   |                  |

|       | UNIT II DEVICES AND BUSES FO                                                            | OR DEVICES N | ETWORK           |

| 1     | I/O Devices - Device I/O Types and Examples                                             | 1            | T1-p.no 130      |

| 2     | Synchronous - Iso-synchronous and<br>Asynchronous Communications from<br>Serial Devices | 1            | T1-p.no 131-134  |

| 3     | Examples of Internal Serial-<br>Communication Devices - UART and<br>HDLC                | 1            | T1-p.no 134-142  |

| 4     | Parallel Port Devices                                                                   | 1            | T1-p.no 142-149  |

| 5     | Sophisticated interfacing features in Devices/Ports                                     | 1            | T1-p.no150-151   |

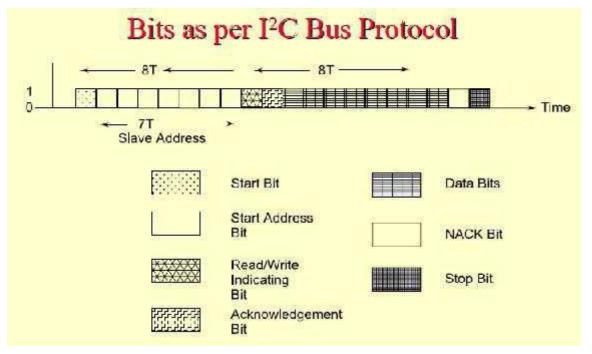

| 6     | Timer and Counting Devices - 'I2C'                                                      | 1            | T1-p.no151-156   |

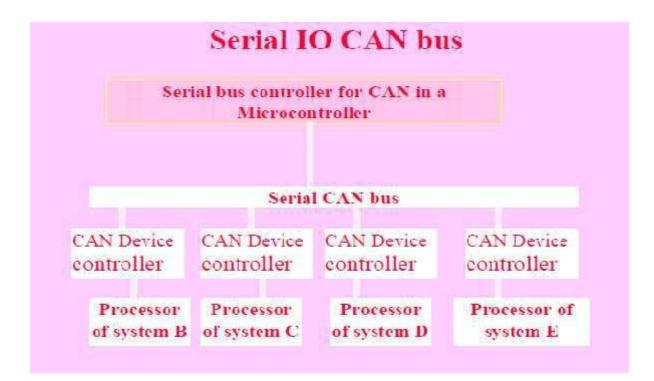

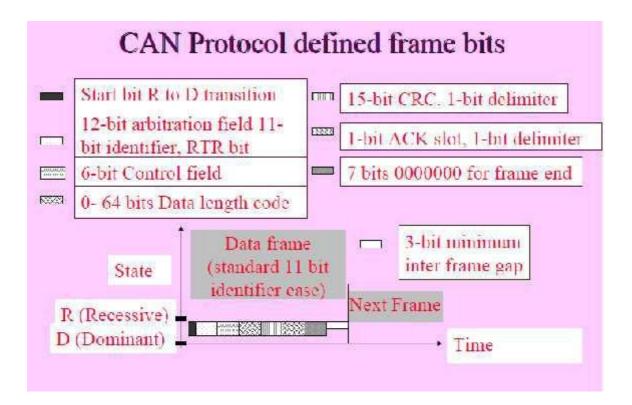

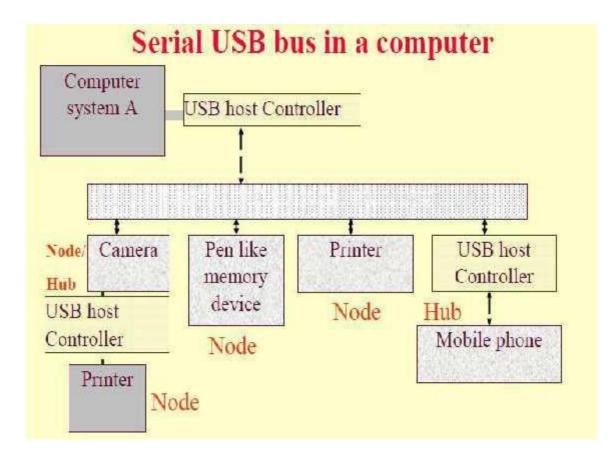

| 7     | 'USB', 'CAN'                                                                            | 1            | T1-p.no161-164   |

| 8     | advanced I/O Serial high speed buses-<br>ISA, PCI                                       | 1            | T1-p.no165-167   |

| 9     | PCI-X, cPCI and advanced buses                                                          | 1            | T1-p.no168-172   |

|       | Total                                                                                   | 9 Hrs        |                  |

| UNIT  | III PROGRAMMING CONCEPTS AND<br>C++                                                     | EMBEDDED P   | ROGRAMMING IN C, |

| 1     | Programming in assembly language<br>(ALP) vs. High Level Language                       | 1            | T1-p.no235-237   |

| 2 |                                             | 1           | TE1 007 044        |

|---|---------------------------------------------|-------------|--------------------|

| 2 | C Program Elements, Macros and              | 1           | T1-p.no237-244     |

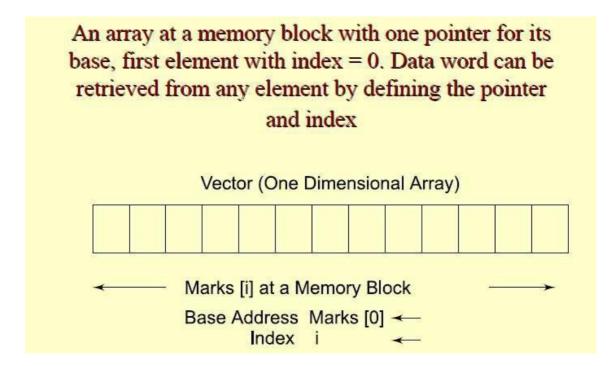

|   | functions -Use of Pointers - NULL           |             |                    |

|   | Pointers                                    |             |                    |

| 3 | Use of Function Calls – Multiple function   | 1           | T1-p.no 256-259    |

|   | calls in a Cyclic Order in the Main         |             |                    |

|   | Function Pointers                           |             |                    |

| 4 | Function Queues and Interrupt Service       | 1           | T1-p.no 259-260    |

|   | Routines Queues Pointers                    |             | 1                  |

| 5 | Concepts of EMBEDDED                        | 1           | T1-p.no260-261     |

| C | PROGRAMMING in C++                          | -           |                    |

| 6 | Objected Oriented Programming               | 1           | T1-p.no 262-264    |

| 7 | Embedded Programming in C++                 | 1           | T1-p.no265         |

| 8 | 'C' Program compilers – Cross compiler      | 1           | T1-p.no266-271     |

| 0 | Optimization of memory codes                | 1           | 11-p.110200-271    |

| 0 |                                             | 1           |                    |

| 9 | Tutorial                                    | 1           |                    |

|   | <b>Total (Theory + Tutorial)</b>            | 9Hrs (8+1)  |                    |

|   | UNIT IV REAL TIME OPERATIN                  | G SYSTEMS - | - PART - 1         |

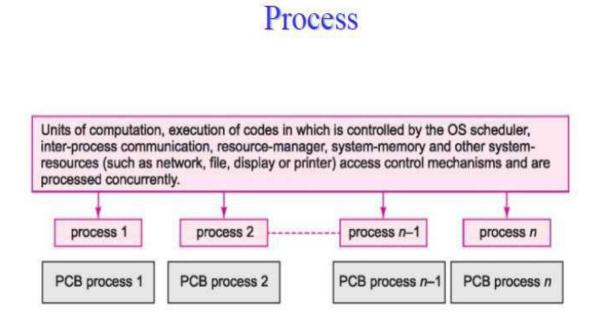

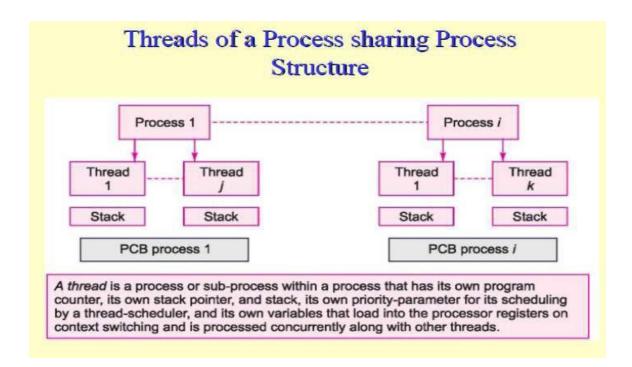

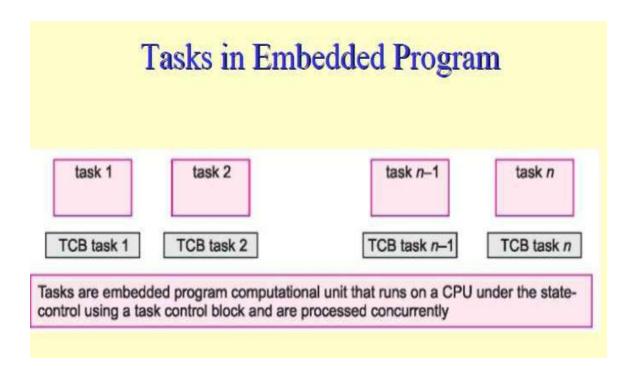

| 1 | Definitions of process, tasks and threads – | 1           | T1-p.no 351-353    |

| 1 | Clear cut distinction between functions –   | 1           |                    |

|   | ISRs and tasks by their characteristics     |             |                    |

|   | isits and tasks by their characteristics    |             |                    |

| 2 | Operating System Services- Goals -          | 1           | T1 p po 256 260    |

| 2 |                                             | 1           | T1-p.no 356-360    |

| 2 | Structures- Kernel - Process Management     | 1           | T1 = == 260 264    |

| 3 | Memory Management – Device                  | 1           | T1-p.no 360-364    |

|   | Management                                  | 1           | <b>T</b> 1 264 260 |

| 4 | File System Organization and                | 1           | T1-p.no 364-369    |

|   | Implementation – I/O Subsystems –           |             |                    |

|   | Interrupt Routines Handling in RTOS         |             |                    |

| 5 | REAL TIME OPERATING SYSTEMS :               | 1           | T1-p.no 385-388    |

|   | RTOS Task scheduling models - Handling      |             |                    |

|   | of task scheduling and latency and          |             |                    |

|   | deadlines as performance metrics            |             |                    |

| 6 | Co-operative Round Robin Scheduling –       | 1           | T1-p.no 388-391    |

|   | Cyclic Scheduling with Time Slicing         |             |                    |

|   | (Rate Monotonics Co-operative               |             |                    |

|   | Scheduling)                                 |             |                    |

| 7 | Preemptive Scheduling Model strategy by     | 1           | T1-p.no 392-394    |

|   | a Scheduler                                 |             | -                  |

| 8 | Critical Section Service by a Preemptive    | 1           | T1-p.no 394-397    |

|   | Scheduler                                   |             |                    |

| 9 | Tutorial                                    | 1           |                    |

| - | Total (Theory + Tutorial)                   |             | 1                  |

|   | UNIT V REAL TIME OPERATIN                   |             | - PART - 2         |

| 1 | INTER PROCESS COMMUNICATION                 | 1           | T1-p.no 331-334    |

|   | AND SYNCHRONISATION – Shared                |             | 1                  |

|   | data problem – Use of Semaphore(s)          |             |                    |

| 2 | Priority Inversion Problem and Deadlock     | 1           | T1-p.no 328-330    |

| - | Situations                                  | -           | p                  |

| 3 | Inter Process Communications using          | 1           | T1-p.no 460-464    |

| 5 | Signals                                     | 1           | 11-p.110 400-404   |

| 1 |                                             | 1           | T1 p po 165 166    |

| 4 | Semaphore Flag or mutex as Resource         | 1           | T1-p.no 465-466    |

|   | key – Message Queues                        |             |                    |

| 5 | Mailboxes – Pipes – Virtual (Logical)       | 1           | T1-p.no 441-449    |

|    | Sockets – Remote Procedure Calls (RPCs) |            |                     |

|----|-----------------------------------------|------------|---------------------|

| 6  | Study of Micro C/OS-II or Vx Works or   | 1          | T1-p.no 452-456     |

|    | Any other popular RTOS                  |            |                     |

| 7  | RTOS System Level Functions – Task      | 1          | T1-p.no 422-423     |

|    | Service Functions – Time Delay          |            |                     |

|    | Functions                               |            |                     |

| 8  | Memory Allocation Related Functions –   | 1          | T1-p.no 424-425     |

|    | Semaphore Related Functions             |            |                     |

| 9  | Mailbox Related Functions – Queue       | 1          | T1-p.no 437-440,445 |

|    | Related Functions                       |            |                     |

| 10 | Tutorial                                | 1          |                     |

|    | Total (Theory + Tutorial)               | 9Hrs (9+1) |                     |

# Total Lecture: 46 Hours (42+4)

#### **TEXTBOOK:**

| S.NO. | Author(s) Name | Title of the book                                           | Publisher                      | Year of<br>Publication |

|-------|----------------|-------------------------------------------------------------|--------------------------------|------------------------|

| 1.    | Rajkamal       | Embedded Systems<br>Architecture,<br>Programming and Design | TATA McGraw-<br>Hill, New York | 2003                   |

#### **REFERENCES:**

| S.NO. | Author(s) Name                   | Title of the book                                                                 | Publisher                                                                | Year of<br>Publication |

|-------|----------------------------------|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------|

| 1.    | Steve Heath                      | Embedded Systems<br>Design                                                        | Newnes                                                                   | 2003                   |

| 2.    | David E.Simon                    | An Embedded Software<br>Primer                                                    | Pearson Education<br>Asia, New York                                      | 2000                   |

| 3.    | Wayne Wolf                       | Computers as<br>Components : Principles<br>of Embedded Computing<br>System Design | Harcourt India,<br>Morgan Kaufman<br>Publishers, First<br>Indian Reprint | 2001                   |

| 4.    | Frank Vahid and<br>Tony Givargis | Embedded Systems<br>Design                                                        | A unified Hardware<br>/ Software<br>Introduction, John<br>Wiley          | 2002                   |

# FACULTY IN-CHARGE

HOD/ECE

# UNIT 1

# Introduction to Embedded Systems

### System:

A way of working, organizing or performing one or many tasks according to a fixed set of rules, program or plan.

Examples of Systems

- 1.Time display system A watch

- 2. Automatic cloth washing system A washing machine

# **Embedded System Definitions:**

- 1. "An embedded system is a system that has software embedded into computer-hardware, which makes a system dedicated for an application (s) or specific part of an application or product or part of a larger system."

- 2. "It is any device that includes a "It is any device that includes a programmable computer but is not itself intended to be a general purpose computer." *Wayne Wolf, Ref: 61*

- 3. "Embedded Systems are the electronic systems that contain a microprocessor or a microcontroller, but we do not think of them as computers– the computer is hidden or embedded in the system." *Todd D. Morton,Ref: 38*

- 4. "An embedded system is one that has a dedicated purpose software embedded in a computer hardware."

#### Three main embedded components:

- 1. Embedded Hardware

- 2. Application Software

- 3. RTOS

#### Sophisticated Embedded System Characteristics

- (1) Dedicated functions

- (2) Dedicated complex algorithms

- (3) Dedicated (GUIs) and other user interfaces for the application

- (4) Real time operations

- (5) Multi-rate operations

#### **Constraints of an Embedded System Design**

Available system-memory Available processor speed Limited power dissipation

#### System design constraints

- ✓ Performance

- ✓ power

- ✓ size

- ✓ non-recurring design cost

- ✓ manufacturing costs.

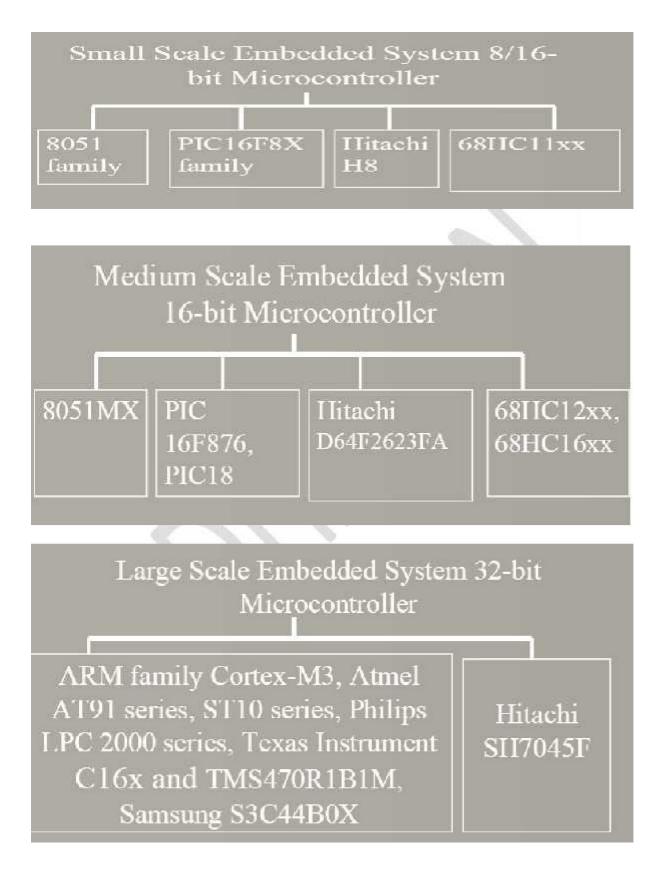

### **Classification of Embedded Systems:**

We can classify embedded systems into three types as

follows 1. Small Scale Embedded System

- 2. Medium Scale Embedded Systems

- 3. Sophisticated Embedded Systems

|                   | Small Scale Embedded<br>Systems                                                           | Medium Scale Embedded<br>Systems                                                                 | Sophisisticated Embedded<br>Systems                                                                                                                                                                                                             |

|-------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SIZE              | 8\16bit microcontroller                                                                   | Single\Few 16 or 32 bit microcontroller                                                          | Need several IP's,<br>ASIPs,Scalable\Configurable<br>Processors                                                                                                                                                                                 |

| Complexity        | Little hardware and software complexity                                                   | Both hardware and software complexity                                                            | Enormous hardware and software complexity                                                                                                                                                                                                       |

| Features          | Battery Operated,<br>Little Power<br>Dissipation,<br>C languages Used for<br>Compilation. | Software tools provides<br>solution for hardware<br>complexity.                                  | Consrained by processing<br>Speeds and performs<br>functions such as encryption,<br>Decrption Algorithms,<br>Discrete Cosine Transform<br>and inverse transformation<br>algorithms, TCP\IP protocol<br>stacking and network driver<br>Functions |

| Software<br>Tools | Editor,Assembler,<br>Cross Assembler                                                      | C\C++\Visual C++, Java,<br>RTOS, Source Code<br>Engineering Tool,<br>Simulator, Debugger,<br>IDE | Retargetable Compiler is needed.                                                                                                                                                                                                                |

#### I. Small Scale Embedded Systems

- These systems are designed with a 8 bit or 16 bit microcontroller.

- They have little hardware and software complexities and involve board-level design. They may even be battery operated.

- In small scale embedded systems an editor, assembler and cross assembler, specific to the microcontroller or processor used, are the main programming tools.

- Usually, 'C' is used for developing these systems. 'C' program compilation is done into the assembly, and executable codes are then appropriately located in the system memory. The software has to fit within the memory available.

- Examples:

- 1. Automatic chocolate vending machine

- 2. Stepper motor controller for a robotics system

- 3. Washing or cooking system

# 2. Medium Scale Embedded Systems

- These systems are usually designed with a single or few 16- or 32-bit microcontrollers or DSPs or Reduced Instruction Set Computers (RISCs).

- These have both hardware and software complexities. For Complex software design, there are the following Programming tools: RTOS, Source code engineering tool, Simulator, Debugger and Integrated Development Environment (IDE). Examples:

- 1. Computer Networking System

- 2. Entertainment systems

- 3. Embedded firewall / Router

- 4. Signal tracking system

#### 3. Sophisticated Embedded Systems

- Sophisticated embedded systems have enormous hardware and software complexities and may need scalable processors or configurable processors and programmable logic arrays.

- They are used for cutting edge applications that need Hardware and software codesign and integration in the final system; however, they are constrained by the processing speeds available in their hardware units.

- Certain software functions such as encryption and Deciphering algorithms, discrete cosine transformation and inverse transforms algorithms. TCP/IP protocol stacking and network driver functions are implemented in the hardware to obtain additional speeds by saving time. Some of the functions of the hardware resources in the Systems are also implemented by the software.

- Examples:

- 1. Embedded system s for wireless LAN & for convergent technology devices.

- 2. Security products & high speed network security, gigabit rate encryption rate products

- 3. Embedded system for real time video & speech

#### **Overview of Processors**

- -Important unit in the embedded system hardware.

- -Heart of an Embedded System.

- -Processors have two essential units

- 1.Control Unit-Includes Fetch Unit for fetching instructions from the memory.

- 2.Execution Unit-Performs data transfer Operations and data conversion from

one to another. It consists of ALU operations and execute the instructions.

#### **Classification:**

- 1. General Purpose Processor

- 1.1 Microprocessor

- 1.2 Embedded Microprocessor

- 2. Application Specific Instruction set Processor

- 2.1 Microcontroller

- 2.2 Embedded Microcontroller

- 2.3 Digital Signal Processor

- 2.4 Network processor

- 3. Single Purpose Processor

- 4. GPP or ASIP cores integrated intoeither ASIC\VLSI circuit

- 5. Application Specific System Processor

- 6. Multicore processors

#### System designer considerations

1.Clock frequency in MHz and processingspeed – Million Instructions Per Second (*MIPS*) or Million Floating Point Instructions Per

2.(*MFLOPS*) or*Dhrystone*- an alternate metric for measuring processing performance.

3. Processor Instructions in the Instruction set

4. Processor ability to solve the complex algorithms used in meeting the deadlines for their processing.

5.Maximum bits in operand (8 or 16 or 32) in a single arithmetic or logical operation. 6.Internal and External bus-widths in the data-path

#### **1.1 Microprocessor**

A Microprocessor is a single VLSI chip that has CPU and also has some other hardware units. The CPU is a unit that has centrally fetches and processes a set of general-purpose instructions. The CPU instructions set includes instructions for data transfer operations, ALU operations, Stack operation, IO operations and program control, Sequencing and Supervising operations.

- 1. A control unit fetches and control the sequential processing of a given command or instruction and communicates with the rest of the system.

- 2. An ALU undertakes arithmetic and logical operations on bytes.

For example, Intel 80x86, Sparc, or Motorola 68HCxxx.

#### 1.2Embedded general purpose processor

It contains the features

1. <u>Fast context switching</u>-use of on-chip Compilers, for example, Intel® XScale<sup>™</sup> Applications Personal Internet Client Architecture-based PDAs, cell phones and other wireless devices.

- 2. 32-bit or 64-bit Atomic ALU operations to avoid shared data problem.

- 3. 32-bit Fast RISC Processor.

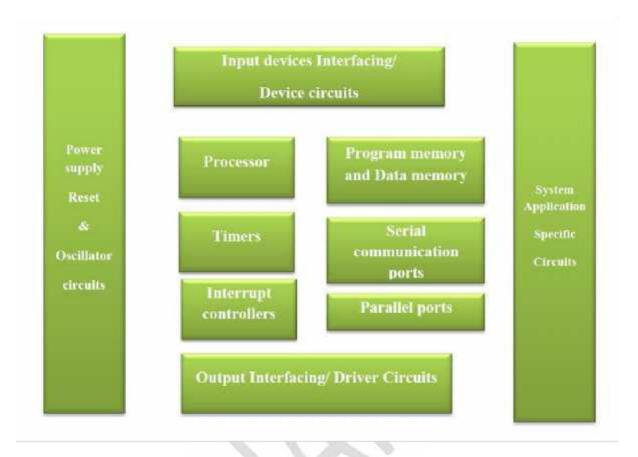

#### 2.1MICROCONTROLLER

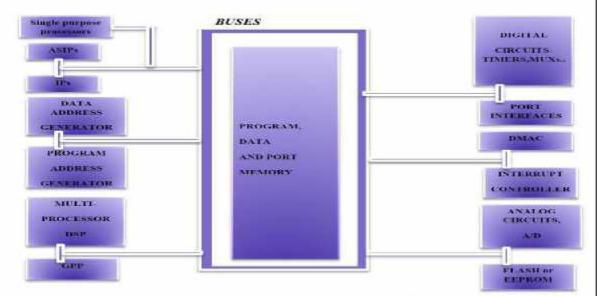

A Microcontroller is an integrated chip that has processor, memory, and several other hardware units. A Microcontroller is a Single-Chip VLSI unitwhich though have limited computational capabilities, Possesses enhanced input output capabilities and a number of on-chip functional units. Figure below shows Functional Circuits present in a Microcontroller.

Examples of Embedded Systems:

#### 2.2 Embedded Microcontroller

It contains the features

1. <u>Fast context switching</u>-use of on-chip Compilers, for example, Intel® XScale<sup>™</sup> Applications Personal Internet Client Architecture-based PDAs, cell phones and other wireless devices.

- 2. 32-bit or 64-bit Atomic ALU operations to avoid shared data problem.

- 3. 32-bit Fast RISC Processor.

#### **2.3 Digital Signal Processor**

Dsp is a Processor core or chip for the applications that process digital signals.DSP is a essential unit of embedded system in a large number of applications processing of signals. Typically a Texas Instruments- C28x Series, C54xx or C64xx or Analog Devices SHARC or TigerSHARC,Motorola 5600xx.

#### **APPLICATIONS:**

Filtering, Noise Cancellation, Echo Elimination, Compression and Encryption Algorithm.

#### **3SINGLE PURPOSE PROCESSORS**

Used for specific purpose Embedded Applications.

- Floating point Coprocessor

- CCD Pixel coprocessor and image codec in digital camera

- Graphic processor

- Speech processor

- Adaptive filtering processor

- Encryption engine

- Decryption engine

- Communication protocol stack processor

- ➢ Java accelerator

- CODEC-1.JPEG CODEC

#### 2.MPEG CODEC

#### 4 GPP or ASIP core (s)

GPP or ASIP Integrated into either an Application Specific Integrated Circuit (ASIC), or a *Very Large Scale Integrated Circuit* (VLSI) circuit or a FPGA core integrated with processor unit(s) in a VLSI (ASIC) chip. Using VLSI design Tools GPP\ASIP with instruction set required in specific application areas can be designed.

#### **5 APPLICATION SPECIFIC SYTEM PROCESSOR**

ASSP is dedicated to these specific tasks alone provides a faster solution. ASSP is configured and interfaced with embedded system. ASSP provides a solution for the problem If software alone used in some applications it takes some longer time. In some cases ASSP chip has a TCP, UDP, IP, ARP, and ETHERNET. EXAMPLES:

Typically a set top box processor or mpeg video-processor or network application processor or mobile application processor.

#### **6 MULTICORE PROCESSORS**

Several processors\Dual core Processors may be needed to execute an algorithm fast within a strict deadline. **Examples** Multiprocessor system for Real time performance in a video-conference system, Embedded firewall cum router, High-end cell phone.

#### COMPONENTS OF EMBEDDED SYSTEMS

# Figure: the components of embedded system hardware Power source

Most systems have a power supply of own. The supply has a specific operation range of voltages. Various units in an embedded system operate in one of the following four operation range:

a) 5.0V±0.25V b) 3.3V±0.3V c) 2.0V±0.2V d) 1.5V±0.2V

Generally, an inverse relationship between propagation delay in the gates and operational voltage. So, the 5V system processor is used most high performance systems.

Certain systems do not have a power source of their: They connect to external power supply or are powered by the use of charge pumps.

Ex: The Network Interface Card (NIC) and Graphic Accelerator.

Low voltage operations

Portable or handheld devices such as a cellular phone.

In a system with smaller overall geometry, low voltage system processors and IO circuits generate lesser heat and thus can be be packed into a smaller space.

#### Clock oscillator circuit and clocking units

The clock controls the time for executing an instruction. The clock controls the various clocking requirements of the CPU, of the system timers and the CPU machine cycles. The machine cycles are for

I. Fetching the codes and data from memory

II. Decoding and executing at the processor,

and III. Transferring the results to memory

For processing units, a highly stable oscillator is required and the processor clockout signal provides the clock for synchronizing all system units with the

#### processor. System timers and real time clocks

A timer circuit is suitably configured as the **system-clock**, generates system interrupts periodically; for example, 60 times in 1s.

A timer circuit is suitably configured as the real-time clock (**RTC**) that generates system interrupts periodically for the schedulers, real-time programs and periodic saving of time and date in the system.

The RTC or system timer is also used to obtain software- controlled delays and timeouts. An RTC functions as drivers for software timers.

#### Reset circuit, power-up reset and watchdog-timer reset

Reset means that the processor begins the processing of instructions from a starting address. That address is one that is set by default in the processor Program Counter on a power-up. From that address in memory, program instructions are fetched following the reset of the processor.

I. A System program executes from

beginning II. A System boot-up program

III. A System initialization program

In certain processors, there are two start-up addresses.

One is based on the power-up reset vector, other on the reset vector after the reset instruction or after a time-out (watchdog timer).

On deactivation of the reset that succeeds the processor activation, a program executes from a start-up address.

Reset can be activated by

I. An external reset circuit that activates on the power-up, on switching-on reset of the system or detection of a low voltage.

II. By a software instruction or time-out by a programmed timer known as watchdog timer.

(Watchdog timer is a timing device that resets the system after a predefined timeout.) **Memory**

In a system, there are various types of memories. They are as follows:

Internal RAM of 256 or 516 bytes in a microcontroller for registers, temporary data and stack.

Internal ROM/PROM/E2PROM for about 4kB to 64kB of

program. External RAM for the temporary data and stack or

internal caches. Internal flash.

Memory stick.

External ROM or PROM for embedding software.

RAM memory buffers at ports.

Caches (in pipelined and superscalar microprocessors).

| Memory needed                | functions                                                                                                                                                                                                                                            |  |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ROM or EPROM                 | Storing application programs from where the processor fetches<br>the instruction codes. Storing codes for system booting,<br>initializing, initial input data and strings. Codes for RTOS.<br>Pointers of various interrupt service routines (ISRs). |  |

| RAM(internal and             | Storing variables during program run and storing the                                                                                                                                                                                                 |  |

| external) and RAM for buffer | stack. Storing input and output buffers,                                                                                                                                                                                                             |  |

| Memory stick                 | A flash memory stick is inserted in mobile computing system or<br>digital camera. It stores high definition video, images, songs, or<br>speeches after a suitable compression.                                                                       |  |

| EEPROM or Flash              | Storing nonvolatile results of processing                                                                                                                                                                                                            |  |

| Cache                        | Storing copies of instructions and data in advance from<br>external memories and storing results temporarily during<br>processing.                                                                                                                   |  |

#### Input, Output and IO Ports, IO buses and IO Interfaces

The system gets inputs from physical devices through the **input ports.** Examples are as follows:

A system gets inputs from the touch screen, keypad.

A controller in a system gets input from the sensors and transducer.

A receiver of signals or a network card gets the input from a communication

system.

Port receives inputs from a network or peripheral.

The system has output ports through which it sends output bytes to the real world. Examples are as follows:

Output may be sent to an LED, LCD or touch screen display panel

A system may send the output to a printer.

Output may be sent to a communication system or network

A control system sends outputs to alarms, actuators, furnaces or boilers.

Each output ports or input ports are identified by its memory –buffer addresses (called port addresses).

There are also ports for both the input and output(IO) operations. For example. Touch screen

Ports can have a serial or parallel communication with the system address and data buses. In serial communication a one-bit data line is used and bits are sent serially in successive time slots. Ex: UART. In parallel communication, several data lines are used and bits are sent in parallel.

**Bus** A system might have to be connected to a number of other devices and systems. For networking the systems, there are different types of buses. For example, I2C, CAN, USB, ISA, EISA and PCI. For wireless networking of systems there are 802.11, IrDA, Bluetooth and Zigbee protocols.

#### **Interrupts Handler**

A system may possess a number of devices and the system processor has to control and handle the requirements of each device by running an appropriate ISR for each.

An **interrupt handling mechanism** must exist in each system to handle interrupts from various processes and for handling multiple interrupts simultaneously pending for service.

There can be a number of **interrupt sources** and groups of interrupt sources in a processor.

**1.** An interrupt may be a hardware signal that indicates the occurrence of an event.

2. An interrupt may also occur through timers.

**3.** An interrupt may occur through an interrupting instruction of the processor program or through an error during processing.

**4.** An interrupt can also arise through a software timer.

The system may prioritize sources and service them accordingly.

The processor's current program has to divert to a service routine to complete that task on the occurrence of the interrupt.

There is a programmable unit on-chip for the interrupt handling mechanism in a microcontroller.

The OS is expected to control the handling of interrupts and running of routines for the interrupts in a particular application.

#### DAC using a PWM and an ADC

**DAC** is a circuit that converts digital 8 or 10 or 12 bits to the analog output. The analog output in with respect to the reference voltage.

A pulse width modulator (PWM) with an integrator circuit is used for this DAC. A PWM unit in the microcontroller operates as follows: Pulse width is made proportional to the analog-output needed.

ADC is a circuit that converts the analog input to digital 4,8,10 or 12 bits.

The ADC in the system microcontroller can be used in many applications such as data acquisition systems, digital cameras, analog control systems and voice digitizing systems.

Important points about the ADC are as follows:

**1.** Either a single or dual analog reference voltage source is required in the ADC. It sets either the analog input's upper limit or the lower and upper limits both. For a single reference source, the lower limit is set to 0V. When the analog input equals the lower limit, the ADC generates all bits as 0s and when it equals the upper limit it generates all bits as 1s.

**2.** An ADC may be of 8, 10, 12 or 16 bits depending upon the resolution needed for conversion.

**3.** The start of conversion (STC) signal or input initiates the conversion to 8 bits.

**4.** There is an end of conversion (EOC) signal that brings the conversion process to end.

**5.** A Sample and Hold unit is used to sample the input for a fixed time and hold till conversion is over.

#### LCD, LED and Touchscreen Displays

A system may need the necessary interfacing circuit and software for the output to the LCD display controller and the LED interfacing ports or for the IOs with the touchscreen.

#### Keypad/Keyboard

For inputs, a keypad or board may interface to a system. The system provides necessary interfacing circuit and software to receive inputs directly from the keys or through a controller.

#### Pulse dialer, Modem and Transceiver

For user connectivity through the telephone line, wireless or a system provides the necessary interfacing circuit.

It also provides the software for pulse dialing through the telephone line, for modem interconnection for fax, for internet packets routing, and for transmitting and connecting a WAG (wireless gateway) or cellular system.

#### **EMBEDDED SOFTWARE IN A SYSTEM**

#### Final machine implementable software for a product

An embedded system processor executes software that is specific to a given application of that system. The instruction codes and data in the final phase are placed in ROM or flash memory for all the tasks that are executed when the system runs. The software is called ROM image.

The image consists of boot up program, stack address pointers, program counter address pointers, application program, ISRs, RTOs, input data and vector addresses.

Each code or data is available only in bits or bytes format. The system requires bytes at each ROM address, according to the tasks being executed.

A machine implementable software file is therefore like a table having in each rows the address and bytes. The bytes are saved at each address of the system memory. The table has to be readied as a ROM image.

# Figure: system ROM memory embedding the software, RTOS, data and vector addresses

#### Coding of software in machine codes

In configuring some specific physical device or subsystem, machine codes based coding is used. However, coding in machine implementable codes is done only in specific situations because it is time consuming.

For example:

TRANSCEIVER- placing certain machine code & bits can configure it to transmit at specific megabytes per second or gigabytes per second, using specific bus and networking protocols.

Configuring CONTROL REGISTER with the processor- during a specific code section processing, the register can be configured to enable or disable use of its internal cache.

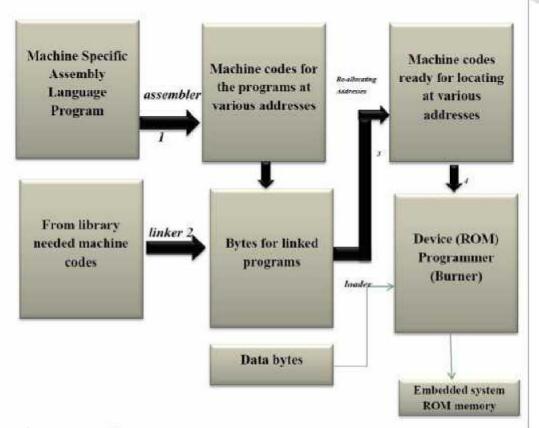

#### Software in processor specific assembly language

A program or a small specific part can be coded in assembly language using an assembler after understanding the processor and its instruction is software used for developing codes in assembly.

# Figure: The process of converting an assembly language program into the machine codes and finally obtaining the ROM image.

#### Steps

1. An assembler translates the assembly software into machine codes using a step called assembling.

2. In the next step, called linking, a linker links these codes with the other required codes. The linked file in binary for run on a computer is commonly known as executable file or simply '**.exe**' file. After linking there has to be re-allocation of the sequences of placing the codes before placement of the codes in the memory.

3. In the next step, the loader program performs the task of reallocating the codes after finding the physical RAM addresses available at a given instant. The loader is a part of the operating system and places codes into the memory after reading the '.exe' file.

4. The final step of the system design process is locating the codes as a ROM image and permanently placing them at the actually available addresses in the ROM. In embedded systems, there is no separate program to keep track of the available addresses at different times during the running, as in a computer.

5. Lastly, either (i) a laboratory system, called device programmer, tasks as input the ROM image file and finally and finally burns the image into the PROM or flash. (ii) at a foundry, a mask is created for the ROM of the embedded system from the image file.( The process of placing the codes in PROM or EPROM is also called burning.)

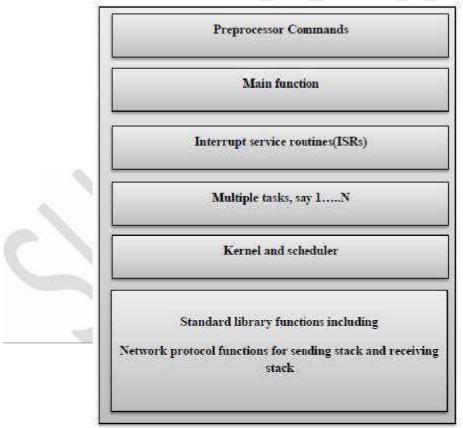

#### Software in high level language

Since the coding in assembly language is very time consuming, software is developed in a high level language, 'C' or 'C++' or 'Java' in most cases.

'C' programs have a feature that adds the assembly instructions when using certain processor specific features and coding for a specific section, for example: a port device driver. The **program layers** in embedded software in C:

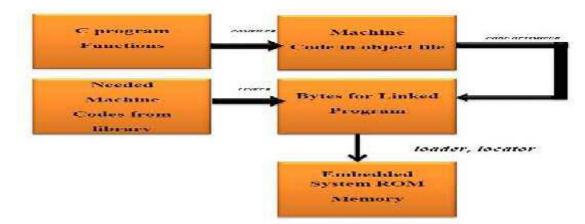

#### The process of converting a C program into the file for ROM image

A compiler generates the object codes. The compiler assembles the codes according to the processor instruction set and other specifications. The 'C' compiler for embedded system must, as a final step of compilation, use a code optimizer that optimizes the codes before linking

After compilation, the linker links the object codes with other needed codes. Codes for device management and driver also link at this stage. After linking, the other steps for creating a file for ROM image are the **loader** and **locator** as in assembly language into ROM image conversion.

Figure: The process of converting a C program into the file for ROM image

# Program Models for software designing

The program design task is simplified if a program is modeled. The different models that are employed during the design process of the embedded software as follows:

- 1. Sequential program model

- 2. Object oriented program model

- 3. Control and data flow graph or synchronous data flow graph or Multi Thread Graph model

- 4. Finite State Machine for data path.

5. Multithreaded Model for concurrent processing of processes or threads or tasks.

#### **Software for Device drivers, Device manager using an Operating System** <u>Devices</u>

o In an embedded system, there are two types of devices.

o Physical devices – keypad, LCDdisplay or touch screen, memory stick(flash memory), wireless networkingdevice, parallel port and networkcard.

o Virtual devices – pipe, file, RAM disk, socket,

A *device driver* is software for controlling (configuring), receiving and sending a byte or a stream of bytes from or to a device. A set of generic functions, such as create (),open (), connect (), listen (), accept (), read (), write (), close (), delete () for use by high level programmers. Each generic function calls a specific software (interrupt service routine), which controls a device function or device input or output

Device controls and functions by :

1. Calling an ISR (also called Interrupt Handler Routine) on hardware or software interrupt

2. Placing appropriate bits at the control register or word.

3. Setting status flag(s) in the status register for interrupting, therefore running (driving) the ISR, Resetting the status flag after interrupt service.

Device Manager for the devices and drivers

Device Management software (usually a part of the OS) provide codes for detecting the presence of devices, for initializing (configuring) these and for testing the devices that are present. Also includes software for allocating and registering port(s) or device codes and data at memory addresses for the various devices at distinctly different addresses, including codes for detecting any collision between the allocated addresses, if any. An OS also provides and execute modules for managing devices for an embedded system.

#### Software Design for Scheduling Multiple tasks and Device using an RTOS

An embedded system is designed for scheduling multiple functions while controlling multiple devices.

□ □ system (OS) and Real time operating system (RTOS), Concurrent Processes, tasks or threads

□□A System is composed of two or more concurrent proce t execute Operating System

tasks

interprocessor communication, shared memory, security, GUIs, ...

management Real Time Operating System (RTOS)

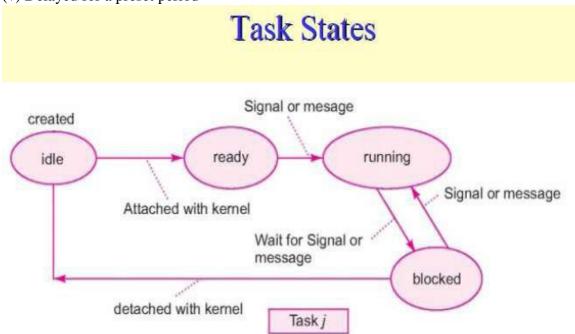

An RTOS\OS has a kernel. The kernel important function is to Schedule the transition of task from ready state to Running state. The kernel coordinates the use of processor for multiple task. RTOS are highly complex. RTOS is needed when the tasks for the system have real time constraints and deadlines for finishing the tasks.

#### Software tools for designing an embedded system

#### Editor

It is used for writing C codes or assembly mnemonics using the keyboard of the PC for entering the program.

It allows the entry, addition, deletion, insert, appending previously written lines or files, merging record and files at the specific positions. It creates a source file that stores the edited file

#### Interpreter

It is used for expression by expression (line by line) translation to the machine executable codes.

#### Compiler

It uses the complete sets of the codes. It may also include the codes, functions and expressions from the library routines. It creates a file called object file.

#### Assembler

It translates the assembly mnemonics into binary opcodes i.e into an executable file called a binary file.

It also creates a list file that can be printed. The list file has address, source code and hexadecimal object codes. The file has addresses that adjust during the actual run of the assembly language program.

#### **Cross assembler**

For converting object codes or executable codes for a processor to other codes for another processor and vice versa. The cross assembler assembles the assembly codes of the target processor as the assembly codes of the processor of the PC used in system development. Later, it provides the object codes for the target processor.

#### Simulator

To simulate all functions of an embedded system circuit including that or additional memory and peripherals. It is independent of a particular target system. It also simulates the processes that will execute when the codes of a particular processor execute.

#### Source- code engineering software

For source code comprehension, navigation and browsing, editing, debugging, configuring (disabling and enabling the C++ features) and compiling.

#### Stethoscope

For dynamically tracking the changes in any program variable or parameter. It demonstrates the sequence of multiple processes that execute and also records the entire time history.

#### **Trace scope**

To help in tracing the changes in modules and tasks with time on the X-axis. A list of actions also produces the desired time scales and the time expected to be taken for different tasks.

#### **Integrated Development Environment (IDE)**

This is a development software and hardware environment that consists of simulators with editors, compilers, assemblers, RTOs, Debuggers, stethoscope, tracer, emulators, logic analyzers and application code burners in PROM.

#### Prototyper

This simulates and does source code engineering including compiling, debugging and browsing and summarizing the complete status f the final target system during the development phase.

#### Locator

This uses cross assembler output and a memory allocation map and provides the locator program output as a hex- file. It is the final step of the software design process or an embedded system.

#### EXAMPLES OFEMBEDDED

#### SYSTEMS Application Areas

o Telecom

o Smart Cards,

- o Missiles and Satellites,

- o Computer Networking,

- o Digital Consumer Electronics, and

o Automotive

**EXAMPLES**

#### Small Scale Embedded System

o Automatic Chocolate Vending Machine

- o Stepper motor controllers for a robotics system

- o Washing or cooking system

o Multitasking Toys

o Microcontroller- based single or multi-display digital panel meter for voltage, current,

resistance and frequency

o Keyboard controller

o Serial port cards

o CD drive or Hard Disk drive controller

o Peripheral controllers,, a CRT display controller, a keyboard controller, a DRAM controller, a DMA controller, a printer controller, or a laser printer-controller, a LAN controller, a disk drive controller

o Fax or photocopy or printer or scanner Machine Remote (controller) of

TV o Telephone with memory, display and other sophisticated features

o Motor controls Systems - for examples, an accurate control of speed and position of d.c. motor, robot, and CNC machine;, the automotive applications like such as a close loop engine control, a dynamic ride control, and an anti-lock braking system monitor

o Electronic data acquisition and supervisory control system Spectrum analyzer

### Medium Scale Embedded Systems

**Computer networking systems**, - for examples, router, front-end processor in a server, switch, bridge, hub, and gateway

For Internet appliances, there are numerous application systems

(i) Intelligent operation, administration and maintenance router (IOAMR) in a distributed network, and

(ii) Mail Client card to store e-mail and personal addresses and to smartly connect to a modem

or server

Banking systems - for examples, Bank ATM and Credit card transactions

**Signal Tracking Systems** - for examples, an automatic signal tracker and a target tracker. **Communication systems**, for examples, such as for a mobile-communication a SIM card, a numeric pager, a cellular phone, a cable TV terminal, and a FAX transceiver with or without a graphic accelerator. Image Filtering, Image Processing, Pattern Recognizer, Speech Processing and Video Processing.

Entertainment systems - such as videogame, music system and Video Games

A system that connects a pocket PC to the automobile driver mobile phone and a wireless receiver. The system then connects to a remote server for Internet or e-mail orto remote computer at an ASP (application Service Provider). A personal information manager using frame buffers in hand- held devices.

Thin Client to provide the disk-less nodes with the remote boot capability.[Application of thin- clients is accesses to a data center from a number of nodes; or in an Internet Laboratory accesses to the Internet leased line through a remote Server]. Embedded Firewall / Router using ARM7/multi-processor with two Ethernet interfaces and interfaces support to for PPP, TCP/IP and UDP protocols.

#### Sophisticated Scale Embedded Systems

es and Computing systems

version 6) Internet and other products, real time video and speech or multimedia processing systems

ultra high speed (10 Gbps) and large bandwidth: Routers, LANs, switches and gateways, SANs (Storage Area Networks), WANs (Wide Area Networks), Security products and High-speed Network security, Gigabit rate encryption rate products **EMBEDDED SYSTEM ON CHIP (SOC) AND IN VLSI CIRCUIT**

Embedded systems are being designed on a single silicon chip, called System on Chip (SOC). SoC is a system on a VLSI chip that has all the necessary analog as well as digital circuits, processors, and software.

A SoC may be embedded with the following components:

- 1. Embedded processor GPP or ASIP core,

- 2. Single purpose processing cores or multiple processors,

- 3. A network bus protocol core,

- 4. An encryption function unit,

- 5. Memories

6. Multiple standard source solutions, called IP (Intellectual property) cores,

7. Programmable logic device and FPGA cores,

8. Digital and analog units.

Ex: mobile phone. Single purpose processors, ASIPs and IPs on an embedded SoC are configured to process encoding, dialing, modulating, demodulating, interfacing the keypad and multiple line LCD matrix displays and touch screen, storing data input and recalling data from memory.

# Fig: A soc embedded sytem and its common bus with two internal ASICs, two internal processors, shared memories and peripheral interfaces

#### **Application Specific IC (ASIC)**

ASICs are designed using the VLSI design tools with the processor GPP or ASIP and analog circuits embedded into the design.

The designing is done using the Electronic Design Automation (EDA)

tool. For design of an ASIC, a High-level Design Language (HDL) is used.

#### **IP** Core

On a VLSI chip, there may be integration of high-level components. These components possess gate-level sophistication in circuits above that of counter, register, multiplier, floating point operation unit and ALU.

A standard source solution for synthesizing a higher level component by configuring FPGA core or a core of VLSI chip may be available as an intellectual property, called (IP)

The Copyright for the synthesized design of a higher level component for gate-level implementation of an IP is held by the designer or designing company.

1. An IP may provide hardwired implementable design of a transform, an encryption algorithm or a deciphering algorithm.

2. An IP may provide a design for adaptive filtering of a signal.

3. An IP may provide a design for implementing Hyper Text Transfer Protocol (HTTP) or File Transfer Protocol (FTP) or Bluetooth protocol to transmit a web page or a file on the Internet.

4. An IP may be designed for a USB or PCI bus controller.

#### FPGA Core with Single or Multiple Processors

A new innovation is Field Programmable Gate Arrays (FPGA) core with a single or multiple processor units on chip.

An FPGA consists of a large number of programmable gates on a VLSI chip. There is a set of gates in each FPGA cell, called macro cell. Each cell has several inputs and outputs and they are interconnected like an array (matrix). Each interconnection is programmable through the associated RAM in an FPGA programming tool. Consider the algorithm for the following: an SIMD instruction, Fourier transform and its inverse, DFT or Laplace transform and its inverse, compression or decompression, encrypting or deciphering, pattern recognition. We can configure an algorithm into the logic gates of FPGA. It gives hardwired implementation for a processing unit.

One example is Xilinx Virtex-II Pro FPGA XC2VP 125. XC2VP125 from Xilinx has 125136 logic cells in the FPGA core with four IBM power PCs. It has been used as a data security solution with encryption engine and data rate of 1.5Gbps.

# UNIT II

# DEVICES AND BUSES FOR DEVICES NETWORK

### IO port types- Serial and parallel IO ports

A port is a device to receive the bytes from external peripheral(s) [or device(s) or processor(s) or controllers] for reading them later using instructions executed on the processor to send the bytes to external peripheral or device or processor using instructions executed on processor.

A Port connects to the processor using address decoder and system buses. The processor uses the addresses of the port-registers for programming the port functions or modes, reading port status and for writing or reading bytes.

# Example

- SI serial interface in 8051

- SPI serial peripheral interface in 68HC11

- PPI parallel peripheral interface 8255

- Ports P0, P1, P2 and P3 in 8051 or PA, PB,PC and PD in 68HC11

- COM1 and COM2 ports in an IBM PC

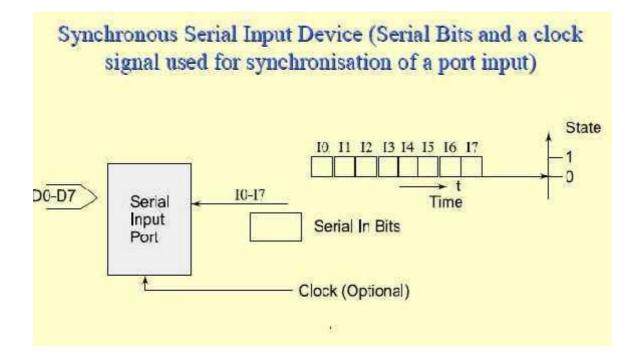

# **IO Port Types**

Types of Serial ports

- Synchronous Serial Input

- Synchronous Serial Output

- Asynchronous Serial UART input

- Asynchronous Serial UART output (both as input and as output, for example, modem.)

•

# Types of parallel ports

- Parallel port one bit Input

- Parallel one bit output

- Parallel Port multi-bit Input

- Parallel Port multi-bit Output

Synchronous Serial Input Example

Inter-processor data transfer, reading from CD or hard disk, audio input, video input, dial tone, network input, transceiver input, scanner input, remote controller input, serial I/O bus input, writing to flash memory using SDIO (Secure Data Association IO based card).

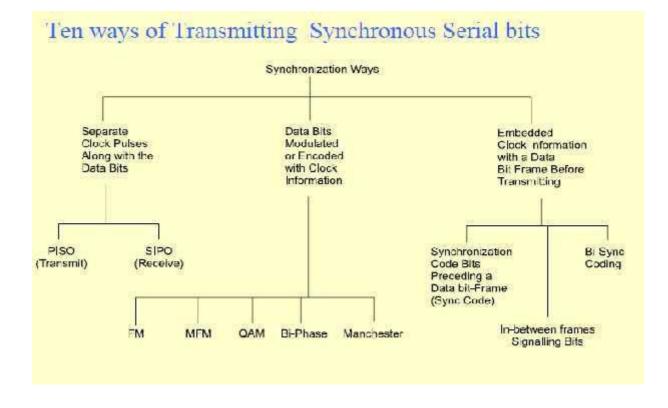

Synchronous Serial Input

- The sender along with the serial bits also sends the clock pulses SCLK (serial clock) to the receiver port pin. The port synchronizes the serial data input bits with clock bits. Each bit in each byte as well as each byte in synchronization

- Synchronization means separation by a constant interval or phase difference. If clock period = T, then each byte at the port is received at input in period = 8T.

- The bytes are received at constant rates. Each byte at input port separates by 8T and data transfer rate or the serial line bits is (1/T) bps. [1bps = 1 bit per s]

- Serial data and clock pulse-inputs

- On same input line when clock pulses either encode or modulate serial data input bits suitably. Receiver detects the clock pulses and receives data bits after decoding or demodulating.

### UNIT-2(EMBEDDED SYSTEMS)-Dr.N.rajalkshmi

• On separate input line – When a separate SCLK input is sent, the receiver detects at the middle or+ ve edge or –ve edge of the clock pulses that whether the data-input is 1 or 0 and

saves the bits in an 8-bit shift register. The processing element at the port (peripheral) saves the byte at a port register from where the microprocessor reads the byte.

# Master output slave input (MOSI) and Master input slave output (MISO)

MOSI when the SCLK is sent from the sender to the receiver and slave is forced

to synchronize sent inputs from the master as per the inputs from master clock.

- MISO when the SCLK is sent to the sender (slave) from the receiver (master) and slave is forced to synchronize for sending the inputs to master as per the master clock outputs.

- Synchronous serial input is used for interprocessor transfers, audio inputs and streaming data inputs.

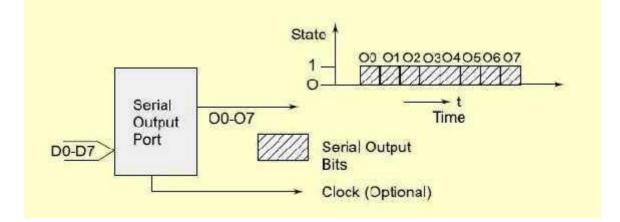

# Synchronous Serial Output Device (Device Serial Bits and synchronisation clock signal at a port output)

# Example Synchronous Serial Output

Inter-processor data transfer, multiprocessor communication, writing to CD or hard disk, audio Input/output, video Input/output, dialer output, network device output, remote TV Control, transceiver output, and serial I/O bus output or writing to flash memory using SDIO

#### **Synchronous Serial Output**

- Each bit in each byte sent in synchronization with a clock.

- Bytes sent at constant rates. If clock period= T, then data transfer rate is (1/T) bps.

- Sender either sends the clock pulses at SCLK pin or sends the serial data output and clock pulse-input through same output line with clock pulses either suitably modulate or encode the serial output bits.

#### Synchronous serial output using shift register

- The processing element at the port (peripheral) sends the byte through a shift register at the port to where the microprocessor writes the byte.

- Synchronous serial output is used for inter processor transfers, audio outputs and streaming data outputs.

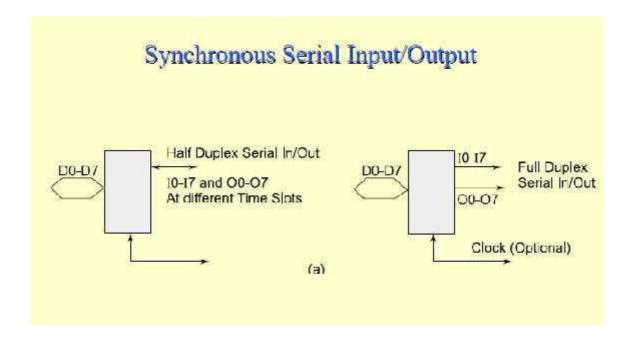

Synchronous Serial Input/output

- Each bit in each byte is in synchronization at input and each bit in each byte is in synchronization at output with the master clock output.

- The bytes are sent or received at constant rates. The I/Os can also be on same I/O line when input/output clock pulses either suitably modulate or encode the serial input/output, respectively. If clock period = T, then data transfer rate is (1/T)bps.

- The processing element at the port (peripheral)sends and receives the byte at a port register to or from where the microprocessor writes or reads the byte

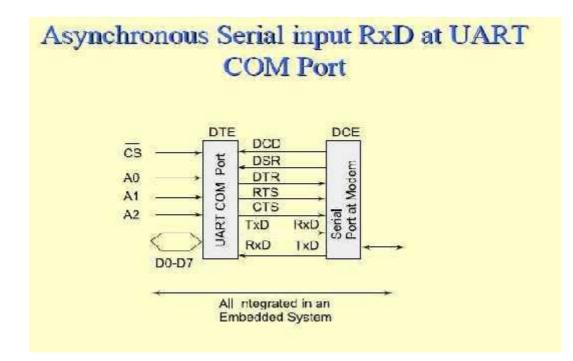

Asynchronous Serial port line RxD (receive data).

- Does not receive the clock pulses or clock information along with the bits.

- Each bit is received in each byte at fixed intervals but each received byte is not in synchronization.

- Bytes separate by the variable intervals or phase differences.

- Asynchronous serial input also called UART input if serial input is according to UART protocol

# **Example Serial Asynchronous Input**

• Asynchronous serial input is used for keypad inputs and modem inputs in computers

#### UNIT-2(EMBEDDED SYSTEMS)-Dr.N.rajalkshmi

• Keypad controller serial data-in, mice, keyboard controller, modem input, character send inputs on serial line [also called UART (universal receiver and transmitter) input when according to UART mode]

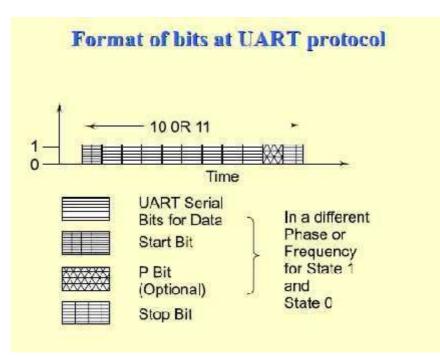

UART protocol serial line format

- Starting point of receiving the bits for each byte is indicated by a line transition from 1to 0 for a period = T. [T-1 called baud rate.]

- If sender's shift-clock period = T, then a byte at the port is received at input in period= 10.T or 11.T due to use of additional bits at start and end of each byte. Receiver detects *n* bits at the intervals of T from the middle of the start indicating bit. The *n* = 0, 1, ..., 10 or 11 and finds whether the data-input is 1 or 0 and saves the bits in an 8-bit shift register.

- Processing element at the port (peripheral)saves the byte at a port register from where the microprocessor reads the byte.

# **Asynchronous Serial Output**

- Asynchronous output serial port line TxD(transmit data).

- Each bit in each byte transmit at fixed intervals but each output byte is not in synchronization (separates by a variable interval or phase difference). Minimum separation is 1 stop bit interval TxD.

- Does not send the clock pulses along with the bits.

#### UNIT-2(EMBEDDED SYSTEMS)-Dr.N.rajalkshmi

• Sender transmits the bytes at the minimum intervals of *n*.T. Bits receiving starts from the middle of the start indicating bit,

• n = 0, 1, ..., 10 or 11 and sender sends the bits through a 10 or 11 -bit shift register. The processing element at the port(peripheral) sends the byte at a port register to where the microprocessor is to write the byte.

• Synchronous serial output is also called UART output if serial output is according to UART protocol

# **Example Serial Asynchronous Output**

\_ Output from modem, output for printer, the output on a serial line [also called UART output when according to UART]

#### Half Duplex

- Half duplex means as follows: at an instant communication can only be one way (input or output) on a bi-directional line.

- An example of half-duplex mode— telephone communication. On one telephone line, the talk can only in the half duplex way mode.

### **Full Duplex**

• Full duplex means that at an instant, the communication can be both ways.

An example of the full duplex synchronous mode of communication is the communication between themodem and the computer though TxDand RxD lines or communication using SI in modes 1, 2 and 3 in 8051

#### **Parallel Port single bit input**

- Completion of a revolution of a wheel,

- Achievingpreset pressure in a boiler,

- Exceeding the upper limit of permittedweight over the pan of an electronic balance,

- Presence of a magnetic piece in the vicinity of or within reach of a robot arm to its endpoint and Filling of a liquid up to a fixed level.

# Parallel Port Output- single bit

- PWM output for a DAC, which controlsliquid level, or temperature, or pressure, orspeed or angular position of a rotating shaftor a linear displacement of an object or ad.c. motor control

- Pulses to an external circuit

- Control signal to an external circuit

# **Parallel Port Input- multi-bit**

#### UNIT-2(EMBEDDED SYSTEMS)-Dr.N.rajalkshmi

- ADC input from liquid level measuringsensor or temperature sensor or pressuresensor or speed sensor or d.c. motor rpmsensor

- Encoder inputs for bits for angular position of a rotating shaft or a linear displacement of an object.

# Parallel Port Output- multi-bit

- LCD controller for Multilane LCD displaymatrix unit in a cellular phone to display onthe screen the phone number, time, messages, character outputs or pictogrambitimages for display screen or e-mail orweb page

- Print controller output

- Stepper-motor coil driving bits

# **Parallel Port Input-Output**

- PPI 8255

- Touch screen in mobile phone

# Ports or DevicesCommunication and communicationprotocols

Two Modes of communication between the devices and computer system

**Full Duplex** – Both devices or device and computer system simultaneously communicate each other.

Half Duplex - Only one device can communicate with another at an instance

Three ways of communication between the ports or devices

- 1. Synchronous

- 2. Iso-synchronous

- 3. Asynchronous

1. Synchronous and Iso-synchronous Communication in Serial Ports or Devices Synchronous

#### Communication.

When a byte (character) or a frame (acollection of bytes) in of the data isreceived or transmitted at the constant ime intervals with uniform phased differences, the communication iscalled as *synchronous*. Bits of a fullframe are sent in a prefixed maximum interval. Iso-synchronous

Synchronous communication special case—when bits of a full frame are sent in themaximum time interval, which can bevariable.

#### **Synchronous Communication**

Clock information is transmitted explicitly or implicitly insynchronous communication. Thereceiver clock continuously maintainsconstant phase difference with the transmitter clock. Bits of a data framemaintain uniform phase difference and are sent within a fixed maximum time interval.

#### Example of synchronous serial communication

- Frames sent over a LAN. Frames of data communicate with the constant time intervals between each frame remaining constant.

- Another example is the inter-processor communication in a multiprocessor system Optional Synchronous Code bits

- Optional Sync Code bits or bi-sync code bits orframe start and end signaling bits— Duringcommunication few bits (each separated byinterval ΔT) sent as Sync code to enable the framesynchronization or frame start signaling.

- Code bits precede the data bits.

- May be inversion of code bits after each frame incertain protocols.

- Flag bits at start and end are also used in certainprotocols. Always present Synchronous device portdata bits

- Reciprocal of T is the bit per second(bps).

- Data bits— *m* frame bits or 8 bitstransmit such that each bit is at the linefor time ΔT or, each frame is at the linefor time (*m*. T)*m* may be 8 or a large number. Itdepends on the protocolSynchronous device clock bits

- Clock bits Either on a separate clockline or on data line such that the clockinformation is also embedded with thedata bits by an appropriate encoding ormodulation

- Generally not optional

#### First characteristics of synchronouscommunication

1. Bytes (or frames) maintain a constant phasedifference, which means they are synchronous, i.e. in synchronization. No permission of sending either the bytes or the frames at therandom time intervals, this mode therefore does not provide for handshaking *during* the communication interval — *This facilitates fastdata communication at pre-fixed bps*. Second characteristics of synchronous communication

2. A clock ticking at a certain rate has always tobe there for transmitting serially the bits of allthe bytes (or frames) *serially. Mostly, theclock is not always implicit* to thesynchronous data receiver. The transmitter*generally* transmits the clock rate information

#### Asynchronous Communication from SerialPorts or Devices

Asynchronous CommunicationClocks of the receiver and transmitterindependent, unsynchronized, but ofsame frequency and variable phasedifferences between bytes or bits of twodata frames, which may not be sentwithin any prefixed time interval.

#### Example of asynchronous communication

- UART Serial, Telephone or modemcommunication.

- RS232C communication between the UART devices

- Each successive byte can have variable time-gap but have a minimum in-

betweeninterval and no maximum limit for fullframe of many bytes

#### Two characteristics of asynchronouscommunication

1. Bytes (or frames) need not maintain a constantphase difference and are asynchronous, i.e., notin synchronization. There is permission to sendeither bytes or frames at variable timeintervals— This*facilitates in-betweenhandshaking* between the serial transmitter portand serial receiver port

2. Though the *clock* must ticking at a certain ratealways has to be there to transmit the bits of asingle byte (or frame) serially, it is *alwaysimplicit* to the asynchronous data receiver and isindependent of the transmitter

#### **Clock Features**

\_ The transmitter *does not transmit* (neitherseparately nor by encoding using modulation)along with the serial stream of bits any *clockrate information* in the asynchronouscommunication and *receiver clock thus is notable to maintain identical frequency andconstant phase difference* with transmitter clock

Example: IBM personal computer has two COMports (communication ports)

- \_ COM1 and COM2 at IO addresses 0x2F8-0xFFand 0xx38-0x3FF

- \_ Handshaking signals— RI, DCD, DSR, DTR, RTS, CTS, DTR

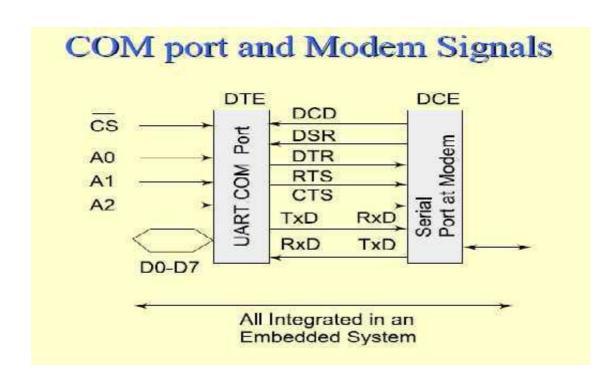

- \_ Data Bits- RxD and TxDExample: COM port and Modem Handshakingsignals

- \_ When a modem connects, modem sends*data carrier detect* DCD signal at aninstance t0.

- \_ Communicates *data set ready* (DSR)signal at an instance t1 when it receives thebytes on the line.

- \_ Receiving computer (terminal) responds at an instance t2 by data terminal ready(DTR) signal.

After DTR, request to send (RTS) signal is sent at aninstance t3

- \_ Receiving end responds by *clear to send* (CTS) signalat an instance t4. After the response CTS, the data bitsare transmitted by modem from an instance t5 to thereceiver terminal.

- \_ Between two sets of bytes sent in asynchronous mode, the handshaking signals RTS and CTS can again beexchanged. This explains why the bytes do not remainsynchronized during asynchronous transmission.

3. Communication Protocols

#### 1. Protocol

A protocol is a standard adopted, which tells the way in which the bits of a frame must be sent from a device (or controller or port or processor) to another device or system [Even in personal communication we follow a protocol – we say Hello! Then talk and then say good bye!]

A protocol defines how are the framebits:

- 1) sent- synchronously or Isosynchronously and at what rate(s)?

- 2) preceded by the header bits?How the receiving device addresscommunicated so that only destined device activates and receives the bits?

[Needed when several devices addressed though a common line(bus)]

- 3) How can the transmitting deviceaddress defined so that receivingdevice comes to know the sourcewhen receiving data from several sources?

- 4) How the frame-length defined so that receiving device know the frame-size in advance?

- 5) Frame-content specifications –Arethe sent frame bits specify the controlor device configuring or commend ordata?

6) Are there succeeding to frame thetrailing bits so that receiving devicecan check the errors, if any inreception before it detects end of theframe ?

A protocol may also define:

## UNIT-2(EMBEDDED SYSTEMS)-Dr.N.rajalkshmi

7) Frame bits minimum and maximumlength permitted per frame

8) Line supply and impedances and line-Connectors specifications

Specified protocol at an embedded systemport or communication deviceIO port bits sent after first formattedaccording to a specified protocol, which is to be followed when communicating with another device through an IO portor channel

Protocols

- \_ HDLC, Frame Relay, for synchronouscommunication

- \_ For asynchronous transmission from a deviceport- RS232C, UART, X.25, ATM, DSL and

#### ADSL

• \_ For networking the physical devices intelecommunication and computer networks – Ethernet and token ring protocols used in LANNetworks

Protocols in embedded network devices

- $\circ$  \_ For Bridges and routers

- \_ Internet appliances application protocols and Web protocols —HTTP (hyper texttransfer protocol), HTTPS (hyper texttransfer protocol Secure Socket Layer),SMTP (Simple Mail Transfer Protocol),POP3 (Post office Protocol version 3),ESMTP (Extended SMTP),

#### File transfer, Boot Protocols in embedded devicesnetwork

- $\circ$  \_ TELNET (Tele network),

- \_ FTP (file transfer protocol),

- \_ DNS (domain network server),

- o \_ IMAP 4 (Internet Message ExchangeApplication Protocol) and

- $\circ$  \_ Bootp (Bootstrap protocol).Wireless Protocols in embedded devices network  $\circ$

- \_ Embedded wireless appliances useswireless protocols— WLAN 802.11,802.16, Bluetooth, ZigBee, WiFi, WiMax,

#### TIMING ANDCOUNTING DEVICES

#### Timer

• Timer is a device, which counts the input at regular interval ( $\delta T$ ) using clock pulses at its input.

- The counts increment on each pulseand store in a register, called countregister

- Output bits (in a count register or at theoutput pins) for the present counts.

#### **Evaluation of Time**

- The counts multiplied by the intervaloT give the time.

- The (present counts –initial counts)  $\times \delta T$  interval gives the time intervalbetween

- two instances when presentcount bits are read and initial countswere read or set.

#### Timer

- \_ Has an input pin (or a control bit incontrol register) for resetting it for allcount bits = 0s.

- \_ Has an output pin (or a status bit instatus register) for output when allcount bits = 0s after reaching themaximum value, which also meansafter timeout or overflow.

#### Counter

- A device, which counts the input due to the events at irregular or regularintervals.

- The counts gives the number of inputevents or pulses since it was last read.

- Has a register to enable read of presentcounts

- Functions as timer when countingregular interval clock pulses

- \_ Has an input pin (or a control bit incontrol register) for resetting it for allcount bits = 0s.

- \_ Has an output pin (or a status bit instatus register) for output when allcount bits = 0s after reaching themaximum value, which also meansafter timeout or overflow.

#### **Timer or Counter Interrupt**

\_ When a timer or counter becomes 0x00or 0x0000 after 0xFF or 0xFFFF(maximum value), it can generate an\_interrupt', or an output \_Time-Out' orset a status bit \_TOV'

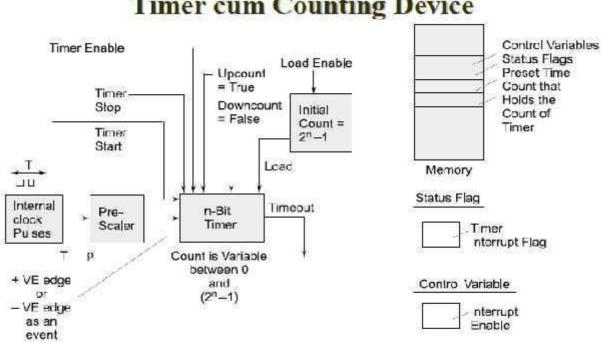

# **Timer cum Counting Device**

A Hardware Timer is a Counter that gets Clock Period nputs at Regular Intervals

#### Free running Counter (Blind runningCounter)

• A counting device may be a free running(blind counting) device giving overflowinterrupts

at fixed intervals

• A pre-scalar for the clock input pulses to fix the intervals

Free Running Counter

It is useful for action or initiating chain of actions, processor interrupts at the

preset instances noting the instances of occurrences of theevents

\_ processor interrupts for requesting the processor to use the capturing of counts at the

input instance

\_ comparing of counts on the events for futureActions

# Free running Timer cum Blind Counting Device

A Hardware Timer is a Counter that gets Inputs at Regular Intervals

Free running (blind counting) device ManyApplications Based on

\_ comparing the count (instance) with the one preloaded in a compare register[an additional register for defining an instance for an action]

\_ capturing counts (instance) in anadditional register on an input event.

[An addition input pin for sensing anevent and saving the counts at theinstance of event and taking action.]

# Free running (Blind Counts) input OCenablepin (or a control bit in controlregister)

• For enabling an output when all count bits atfree running count = preloaded counts in the compare register.

• At that instance a status bit or output pin alsosets in and an interrupt \_OCINT'

ofprocessor can occur for event of comparisonequality.

• Generates alarm or processor interrupts atthe preset times or after **preset**

#### interval fromanother event

# Free running (Blind Counts) input capture -enable pin (or a control bit in controlregister)

for Instance of Event Capture

• A register for capturing the counts on an instance of an input (0 to 1 or 1 to 0 or toggling) transition

\_ A status bit can also sets in andprocessor interrupt can occur for thecapture event

#### Free running (Blind Counts) Pre-scaling

• Prescalar can be programmed as p = 1, 2, 4, 8, 16, 32, ... by programming a

prescalerregister. •Prescalar divides the input pulses as perthe programmed value of *p*.

- Count interval =  $p \times \delta T$  interval

- $\delta T$  = clock pulses period, clockfrequency =  $\delta T 1$

# Free running (Blind Counts) Overflow

- It has an output pin (or a status bit instatus register) for output when allcount bits =

- Os after reaching themaximum value, which also meansafter timeout or overflow

- Free running n-bit counter overflowsafter  $p \times 2n \times \delta T$  interval

- Uses of a timer device

• \_ Real Time Clock Ticks (System HeartBeats). [Real time clock is a clock, which, once the system starts, does notstop and can't be reset and its *countvalue* can't be reloaded. *Real timeendlessly flows and never returnsback*!] Real Time Clock is set for ticksusing prescaling bits (or rate set bits) inappropriate control registers.

- Initiating an event after a preset delaytime. Delay is as per *count value*loaded.

- Initiating an event (or a pair of events r a chain of events) after acomparison(s) with between the pre-settime(s) with counted value(s). [It is is milar to a preset alarm(s).].

- Apreset time is loaded in a CompareRegister. [It is similar to presetting analarm].

- Capturing the *count value* at the timeron an event. The information of *time*(instance of the event) is thus stored at the *capture register*.

- Finding the time interval between twoevents. *Counts* are captured at eachevent in capture register(s) and read. The intervals are thus found out.

- Wait for a message from a queue ormailbox or semaphore for a preset timewhen using RTOS. There is aApredefined waiting period is donebefore RTOS lets a task run.

#### Watchdog timer.

It resets the systemafter a defined time.

- \_ Baud or Bit Rate Control for serialcommunication on a line or network.Timer timeout interrupts define thetime of each baud

- \_ Input pulse counting when using atimer, which is ticked by giving nonperiodicinputs instead of the clockinputs. The timer acts as a counter if, inplace of clock inputs, the inputs aregiven to the timer for each instance tobe counted.

- \_ Scheduling of various tasks. A chain ofsoftware-timers interrupt and RTOSuses these interrupts to schedule thetasks.

- \_ Time slicing of various tasks. Amultitasking or multi-programmedoperating system presents the illusion thatmultiple tasks or programs are runningsimultaneously by switching betweenprograms very rapidly, for example, afterevery 16.6 ms.

• \_ Process known as a *context switch*.[RTOSswitches after preset time-delay from onerunning task to the next. task. Each task cantherefore run in predefined slots of time]

#### Time division multiplexing (TDM)