### 17BEBME6E04 BIOSIGNAL CONDITIONING CIRCUITS

### COURSE OBJECTIVE

- To gain in depth knowledge of fundamentals of operational amplifier circuits

- To study the various applications using operational amplifiers.

### UNIT 1

### INTRODUCTION TO OPAMP

Introduction, Signal conditioning, 741 General purpose OPAMP: ideal characteristics, offset voltages and currents. Open & Closed Loop Configuration. Inverting, Non-Inverting, Summing, Voltage Follower, Integrator, differentiators, Log & Anti-Log Amplifiers, Differential Amplifiers, CMRR.

### UNIT 2

### APPLICATION OF OPAMPS

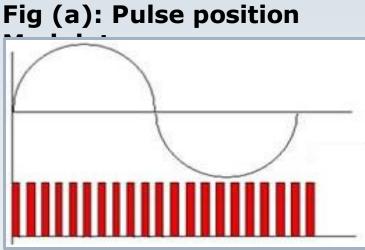

Comparator- Zero crossing detector, Inverting and non inverting comparator, Schmitt Trigger, Precision rectifiers- Half wave and Full wave rectifiers, Peak detectors, Monostable, Astable multivibrators, Sawtooth generator, Triangular waveform generator, Sine Wave Generators-RC Phase Shift Oscillator, Wein Bridge oscillator.

FILTERS

## UNIT 3

9

Introduction- Analog Filters, Active Filters and Passive Filters, First order and Second order Low Pass Filters, High Pass Filters, Band Pass Filters- Narrow Band Pass, Wide band Pass Filters, Band Reject Filters- Notch Filter, All Pass filters and higher Order filters- Design and applications.

### UNIT 4

## A/D AND D/A CONVERTERS

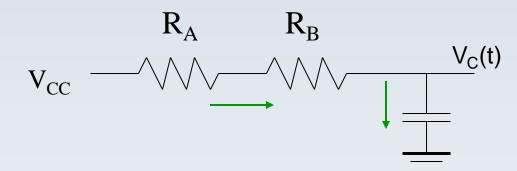

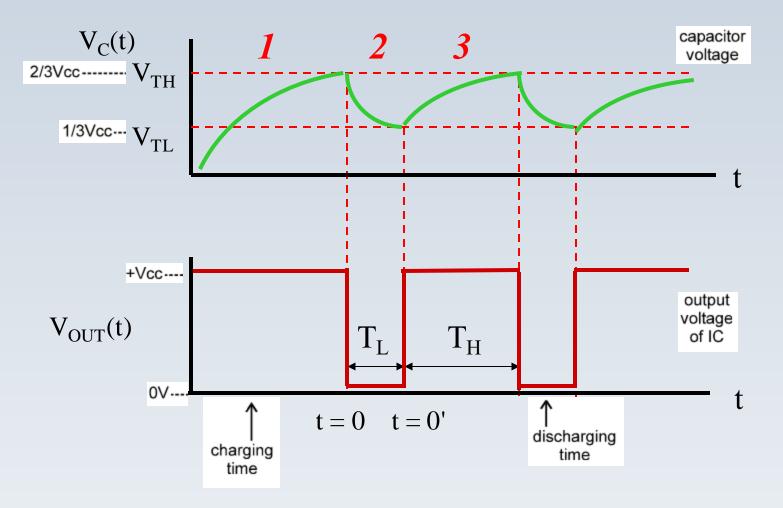

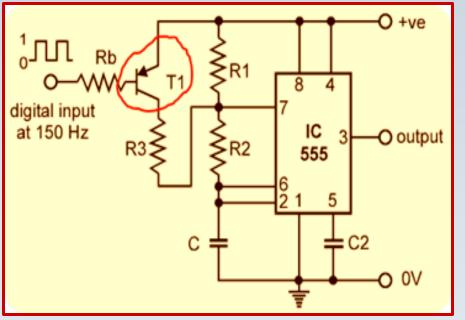

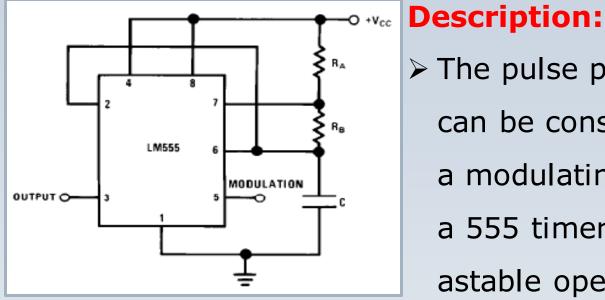

Sample and Hold circuit - D/A converters: Resistive divider and R-2R ladder networks, A/D converters: Counting type, Successive approximation, parallel comparator, Voltage to Current Converter, 555 Timer and its applications- Astable multivibrators and Monostable Multivibrator.

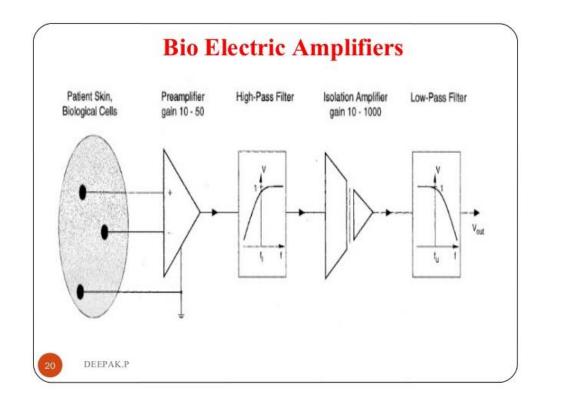

## UNIT 5 AMPLIFIERS

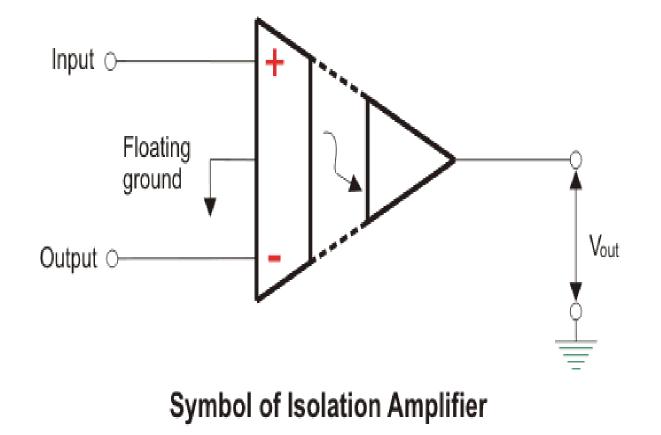

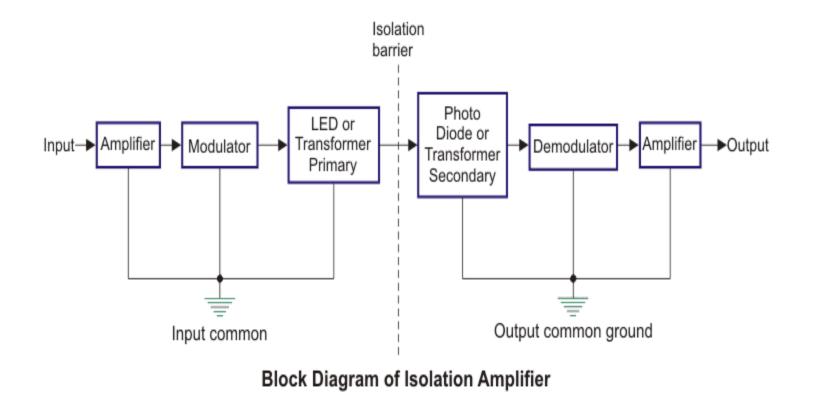

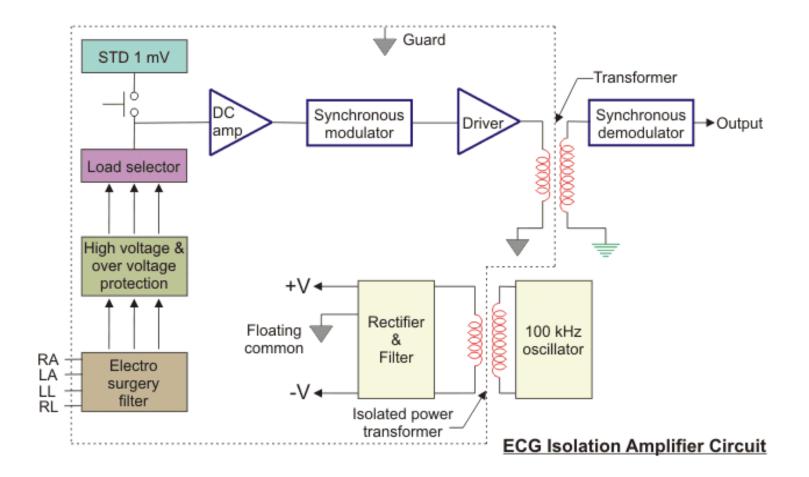

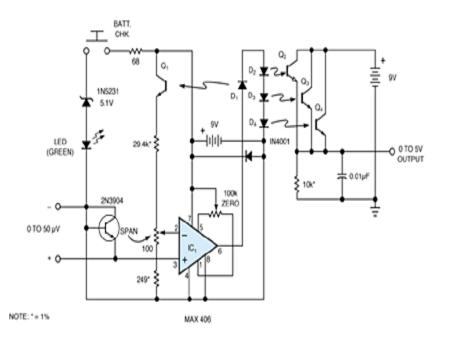

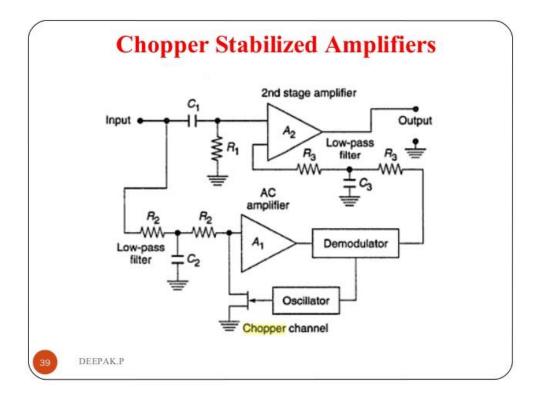

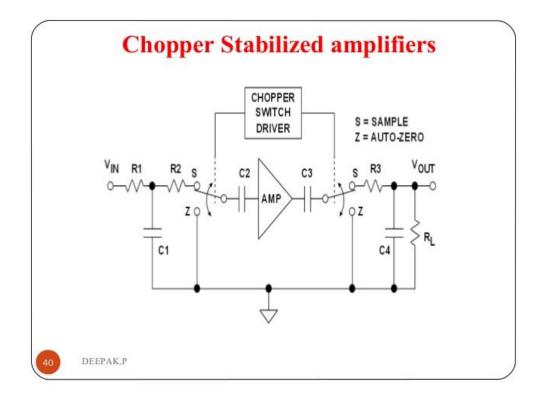

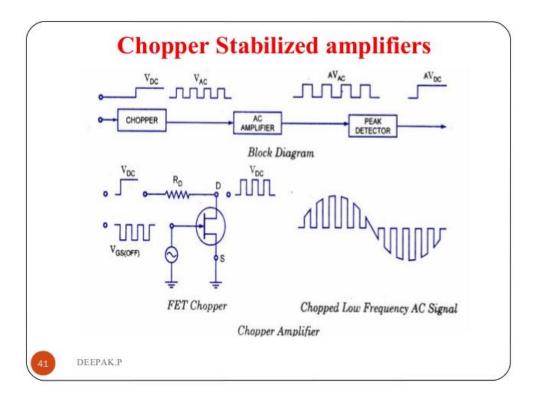

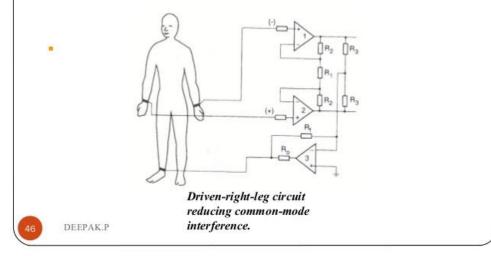

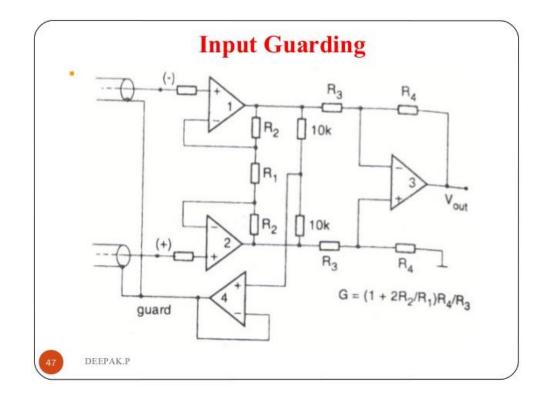

Instrumentation amplifiers, Bridge Amplifiers, Bioelectric Amplifiers: - Properties desired, Isolation Amplifiers:- Battery Powered, Carrier, Optically Coupled, Current Loading, Chopper Stabilized amplifier, Input Guarding.

Total:45

| S.NO. | Author(s) Name                    | Title of the book                                      | Publisher                                                 | Year of publication |

|-------|-----------------------------------|--------------------------------------------------------|-----------------------------------------------------------|---------------------|

| 1     | Ramakant A Gayakwad               | Operational Amplifiers &<br>Linear Integrated Circuits | Prentice Hall                                             | 2000                |

| 2     | Joseph J. Carr & John M.<br>Brown | Introduction to Biomedical<br>Equipment Technology     | Pearson Education Pvt.<br>Ltd, 4 <sup>th</sup> edition    | 2001                |

| 3     | Roy Choudhary                     | Linear Integrated Circuits                             | Linear Integrated Circuits New Age International (P) Ltd, |                     |

| 4     | John P.Bentley                    | Principles of Measurement System                       | Longman Science &<br>Technology                           | 1995                |

## TEXT / REFERENCE BOOKS

## 3003 100

9

9

9

| 5 | Jacob Mill man                 | Micro Electronics                                      | McGraw-Hill   | 1987 |  |

|---|--------------------------------|--------------------------------------------------------|---------------|------|--|

| 6 | Robert Coughlin and<br>Fredrer | Operational Amplifiers & Linear<br>Integrated Circuits | Prentice Hall | 2001 |  |

## **KARPAGAM ACADEMY OF HIGHER EDUCATION**

(Established Under Section 3 of UGC Act 1956) FACULTY OF ENGINEERING

## **`DEPARTMENT OF BIOMEDICAL ENGINEERING** 17BEBME6E04 – BIOSIGNAL CONDITIONING CIRCUITS LECTURE PLAN

- NAME OF THE STAFF : Ms.S.JAYACHITRA

- DESIGNATION : ASSISTANT PROFESSOR

CLASS : B.E-III YEAR BME

SUBJECT NAME

: BIOSIGNAL CONDITIONING CIRCUITS

SUBJECT CODE : 17BEBME6E04

| S.No  | <b>TOPICS TO BE COVERED</b>             | TIME     | SUPPOTING          |  |  |  |

|-------|-----------------------------------------|----------|--------------------|--|--|--|

| •     |                                         | DURATION | MATERIALS          |  |  |  |

|       |                                         |          |                    |  |  |  |

| UNIT  | UNIT I INTRODUCTION TO OPAMP            |          |                    |  |  |  |

| 1     | Introduction, Signal conditioning,      | 01       | T3- Page.no 2-12   |  |  |  |

|       |                                         |          | T1 Page.no 23-42   |  |  |  |

| 2     | 741 General purpose OPAMP: ideal        | 01       | T3 Page.no 53-54   |  |  |  |

|       | characteristics                         |          |                    |  |  |  |

| 3     | offset voltages and currents.           | 01       | T3- Page.no.42-43  |  |  |  |

|       |                                         |          |                    |  |  |  |

| 4     | Open & Closed Loop Configuration        | 01       | T3 Page.no 104-110 |  |  |  |

| 5     | Basic op-amp circuits: Inverting & Non- | 01       | T3 Page.no43-48    |  |  |  |

|       | Inverting Amplifier                     |          |                    |  |  |  |

| 6     | Voltage follower - Summing, scaling     | 01       | T3 Page.no 49      |  |  |  |

|       | amplifiers                              |          |                    |  |  |  |

| 7     | Integrator, differentiators             | 01       | T3 Page.no 164-169 |  |  |  |

| 8     | Log & Anti-Log Amplifiers               | 01       | T3 Page.no 155-158 |  |  |  |

| 9     | Differential Amplifiers, CMRR           | 01       | T3 Page.no 53-60   |  |  |  |

| Total | Lecture Hours                           | 09       | 1                  |  |  |  |

| Total | Hours                                   | 09       |                    |  |  |  |

| UNIT | UNIT II APPLICATIONS OF OPAMPS           |    |                     |  |  |

|------|------------------------------------------|----|---------------------|--|--|

| 10   | Comparator- Zero crossing detector,      | 01 | T3 Page.no 207-210  |  |  |

|      | Inverting and non inverting comparator,  |    |                     |  |  |

| 11   | Schmitt Trigger , -                      | 01 | T3 Page.no 324,212- |  |  |

|      |                                          |    | 215                 |  |  |

| 12   | Precision rectifiers- Half wave and Full | 02 | T3 Page.no 148-150  |  |  |

|      | wave rectifiers, Peak detectors,         |    |                     |  |  |

| 13   | Monostable, Astable multivibrators,      | 01 | T3 Page.no 216-219  |  |  |

| 14   | Sawtooth generator, Triangular waveform  | 01 | T3 Page.no 220      |  |  |

|      | generator                                |    |                     |  |  |

| 15   | Sine Wave Generators                     | 01 | T3 Page.no 222-228  |  |  |

| 16                  | RC Phase Shift Oscillator, | 01 |  |

|---------------------|----------------------------|----|--|

| 17                  | Wein Bridge oscillator.    | 01 |  |

|                     |                            |    |  |

| Total Lecture Hours |                            | 09 |  |

| Total Hours         |                            | 09 |  |

| UNIT I  | UNIT III FILTERS                                 |    |                    |  |  |

|---------|--------------------------------------------------|----|--------------------|--|--|

| 18      | Introduction- Analog Filters, Active Filters and | 02 | T3 Page.no 262-264 |  |  |

|         | Passive Filters                                  |    |                    |  |  |

| 19      | First order and Second order Low Pass Filters    | 01 | T3 Page.no 264-272 |  |  |

| 20      | First order and Second order high Pass Filters   | 01 | T3 Page.no 264-272 |  |  |

| 21      | Band Pass Filters- Narrow Band Pass, Wide        | 01 | T3 Page.no 272-277 |  |  |

|         | band Pass Filters,                               |    |                    |  |  |

| 22      | Band Reject Filters- Notch Filter ,All Pass      | 02 | T3 Page.no 272-277 |  |  |

|         | filters.                                         |    |                    |  |  |

|         |                                                  |    |                    |  |  |

| 23      | Higher Order filters- Design and applications    | 02 | T3 Page.no 264-277 |  |  |

| Total L | ecture Hours                                     | 09 |                    |  |  |

| Total H | lours                                            | 09 |                    |  |  |

| UNIT    | IV A/D AND D/A CONVERTERS                    |    |                                                                                                                       |

|---------|----------------------------------------------|----|-----------------------------------------------------------------------------------------------------------------------|

| 24      | Sample and Hold circuit                      | 01 |                                                                                                                       |

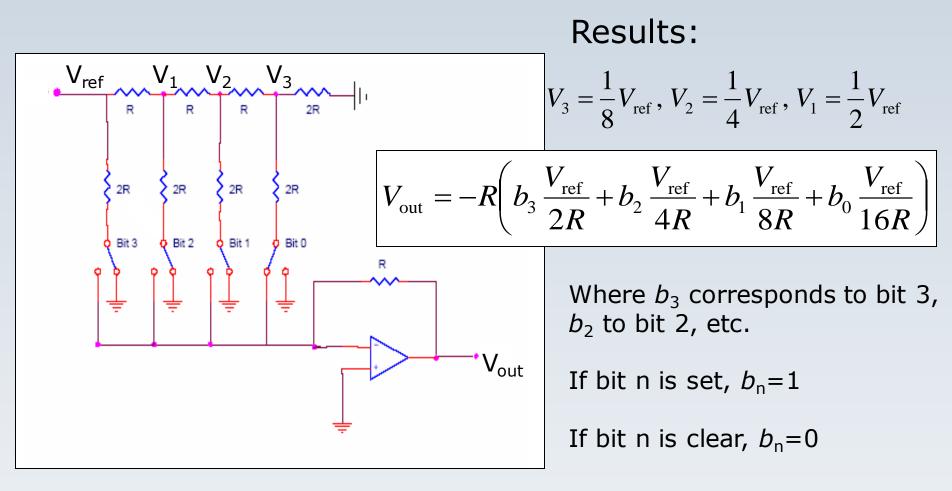

| 25      | D/A converters: Resistive divider            | 01 | T3 Page.no 349-353                                                                                                    |

| 26      | R-2R ladder networks,                        | 01 | T3 Page.no 353-355                                                                                                    |

| 27      | A/D converters: Counting type                | 01 | T3 Page.no 357-366                                                                                                    |

| 28      | Successive approximation type A/D converters | 01 | T3 Page.no 361-362                                                                                                    |

| 29      | Parallel comparator,                         | 01 | T3 Page.no356-357                                                                                                     |

| 30      | Voltage to Current Converter                 | 01 |                                                                                                                       |

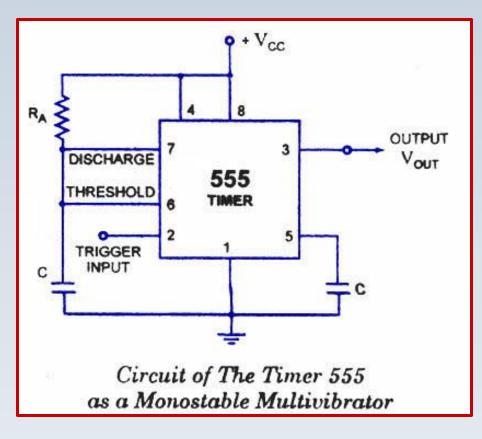

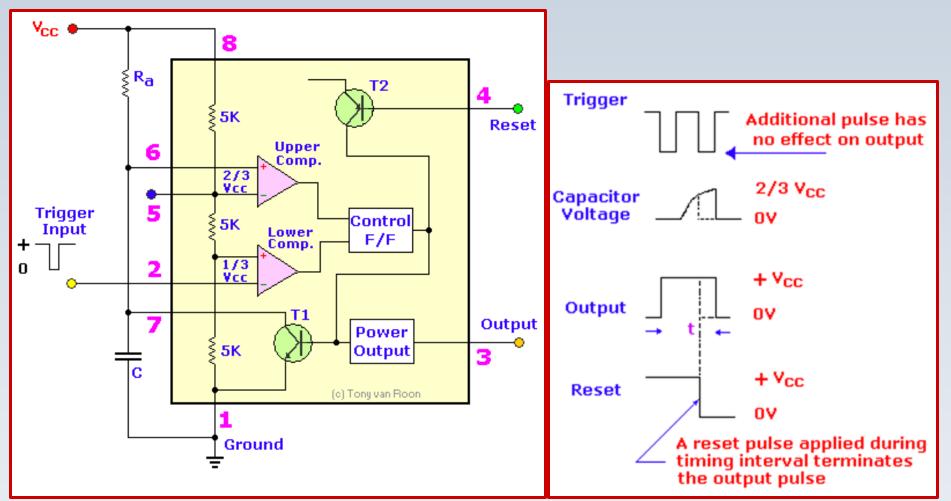

| 31      | 555 Timer and its applications : Monostable  | 01 | T3 Page.no 311-312                                                                                                    |

|         | operation and its applications               |    |                                                                                                                       |

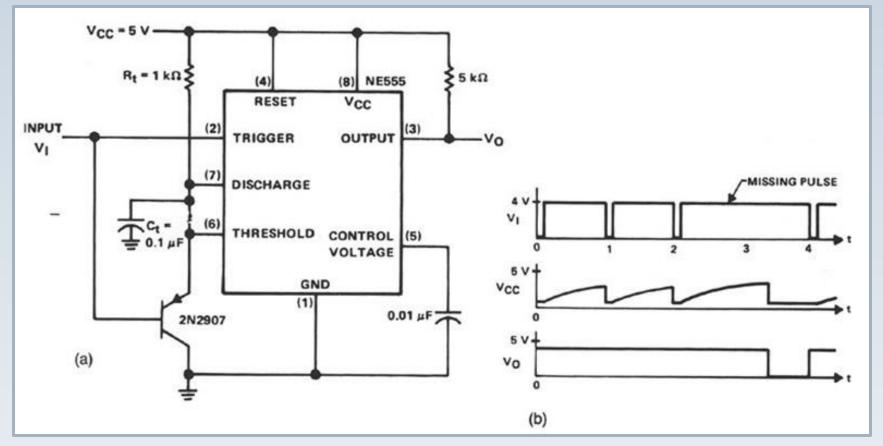

| 32      | IC 555 Timer: Astable operation and its      | 01 | T3 Page.no 318-324                                                                                                    |

|         | applications                                 |    |                                                                                                                       |

| Total ] | Lecture Hours                                | 09 |                                                                                                                       |

| Total ] | Hours                                        | 09 |                                                                                                                       |

| UNIT    | V AMPLIFIERS                                 |    |                                                                                                                       |

| 33      | Instrumentation amplifiers                   | 01 | T3 Page.no 141-144                                                                                                    |

| 34      | Bridge Amplifiers                            | 01 | https://www.allaboutci<br>rcuits.com/technical-<br>articles/bridge-<br>amplifiers-for-single-<br>supply-applications/ |

| 35      | Bioelectric Amplifiers- Properties desired   | 01 | http://www.electronics<br>andcommunications.c                                                                         |

|              |                                          |    | om/2017/07/bioelectri<br>c-amplifiers.html                                           |

|--------------|------------------------------------------|----|--------------------------------------------------------------------------------------|

| 36           | Isolation Amplifiers                     | 01 | http://www.learningab<br>outelectronics.com/Art<br>icles/Isolation-<br>amplifier     |

| 37           | Battery Powered amplifiers               | 01 | https://engineering.pur<br>due.edu/ece40020/Lec<br>tureNotes/PowerAmp<br>Class.pdf   |

| 38           | Optically Coupled amplifiers             | 01 | https://www.alliedelec<br>.com/m/d/70ef6270eca<br>b8061fff13fbcd46938<br>69.pdf      |

| 39           | Current Loading                          | 01 | https://mgh-<br>courses.ece.gatech.edu<br>/ece4430/ECE4430/U<br>nit2/BJTDiffAmps.pdf |

| 40           | Carrier and Chopper Stabilized amplifier | 01 | http://cas.ee.ic.ac.uk/p                                                             |

| 41           | Input Guarding                           | 01 | eople/dario/files/E302/<br>4-amplifiers.pdf                                          |

| <b>Total</b> | Lecture Hours                            | 09 |                                                                                      |

| Total        | Hours                                    | 09 |                                                                                      |

Total No of Lecture Hours Planned: 45 Hours

## **TEXT / REFERENCE BOOKS**

| S.NO. | Author(s) Name                    | Title of the book                                      | Publisher                                              | Year of publication |

|-------|-----------------------------------|--------------------------------------------------------|--------------------------------------------------------|---------------------|

| 1     | Ramakant A<br>Gayakwad            | Operational Amplifiers &<br>Linear Integrated Circuits | Prentice Hall                                          | 2000                |

| 2     | Joseph J. Carr & John<br>M. Brown | Introduction to Biomedical<br>Equipment Technology     | Pearson Education<br>Pvt. Ltd, 4 <sup>th</sup> edition | 2001                |

| 3     | Roy Choudhary                     | Linear Integrated Circuits                             | New Age<br>International (P) Ltd,                      | 2004                |

| 4     | John P.Bentley                    | Principles of Measurement<br>System                    | Longman Science &<br>Technology                        | 1995                |

| 5     | Jacob Mill man                    | Micro Electronics                                      | McGraw-Hill                                            | 1987                |

| 6     | Robert Coughlin and Fredrer       | Operational Amplifiers &<br>Linear Integrated Circuits | Prentice Hall                                          | 2001                |

# UNIT-1 INTRODUCTION TO OPAMP

1

Prepared by S.JAYACHITRA,AP/ECE

# **OPERATIONAL AMPLIFIER**

- An operational amplifier is a direct coupled high gain

- Amplifier usually consisting of one or more differential amplifier and usually followed by a level translator and an output stage.

- An operational amplifier is available as a single

- integrated circuit package.

- The operational amplifier is versatile device that can be used to amplify DC as well as AC input signals and was originally designed for computing such mathematical functions as addition, subtraction, multiplication and integration.

# **OP AMPS APPLICATIONS**

- Audio amplifiers

- Speakers and microphone circuits in cell phones, computers, mpg players, boom boxes, etc.

- Instrumentation amplifiers

- Biomedical systems including heart monitors and oxygen sensors.

- Power amplifiers

- Analog computers

- Combination of integrators, differentiators, summing amplifiers, and multipliers

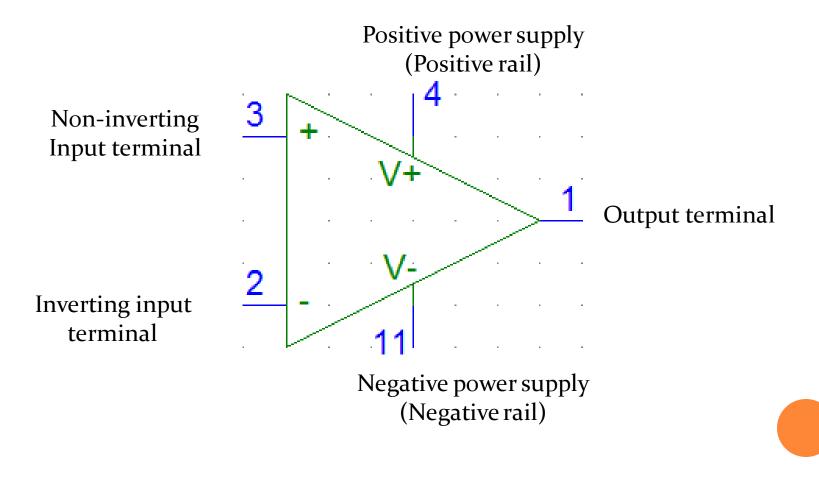

# OP AMP SYMBOL

Karpagam Academy of Higher Education

# **IDEAL CHARACTERISTICS OF OP-AMP**

- An IDEAL op-amp would exhibit the following

- electrical characteristics.

- o Infinite voltage gain, A

- o Infinite input resistance Ri

- o Zero output resistance Ro

- – Zero output voltage when input voltage is zero.

- – Infinite bandwidth any signal can be amplified

- without attenuation

- o Infinite common mode rejection ratio

- – Infinite slew rate so that output voltage changes occur simultaneously with input voltage changes.

# **OFFSET VOLTAGE**

- Input offset voltage: Input offset voltage Vio is

- the differential input voltage that exists

- between two input terminals of an op-amp

- with out any external inputs applied.

- o Output Offset Voltage:

- – The output voltage caused by mismatching

- between two input terminals is called the output

- offset voltage Voo.

- – The output offset voltage Voo is a DC voltage, it

- may be +ve or –ve in polarity depending on

- whether the potential differences between the

- two input terminals is +ve or –ve.

# **OFFSET CURRENT**

## • Input offset Current:

- - The input offset current lio is defined as the

- algebraic difference between two input bias

- currents Ib1 and Ib2. In equation form it is

- Iio = |Ib1 Ib2|

- o Input Bias Current:

- An input bias current Ib is defined as the average of

- the two input bias currents, Ib1 and Ib2 as shown in

- the following figure.

- Ib = (Ib1 + Ib2)/2 [Ib DC current]

- Where Ib1=DC bias current flowing into the noninverting

- o input

- Ib2 = DC bias current flowing into the inverting

- o input

- The value of input bias current Ib is very small, in the

- range of a few to few hundred nano amp.

# DIFFERENCES B/W IDEAL AND PRACTICAL OP-AMP

| Characteristics                           | Ideal Op-amp | Practical Op-amp |

|-------------------------------------------|--------------|------------------|

| Voltage gain                              | Infinite     | High             |

| Input resistance                          | Infinite     | High             |

| Output resistance                         | Zero         | Low              |

| Output voltage when input voltage is zero | Zero         | Low              |

| Band width                                | Infinite     | High             |

| CMRR                                      | Infinite     | High             |

| Slew Rate                                 | Infinite     | High             |

# WHY OP-AMP IS GENERALLY NOT USED IN OPEN LOOP MODE?

- As open loop gain of op-amp is very large, very small input voltage drives the op-amp voltage to the saturation level.

- Thus in open loop configuration, the output is at its positive saturation voltage (+Vsat ) or negative saturation voltage (-Vsat ) depending on which input V1 or V2 is more than the other.

- For a.c. input voltages, output may switch between positive and negative saturation voltages.

- This indicates the inability of op-amp to work as a linear small signal amplifier in the open loop mode. Hence the op-amp in open loop configuration is not used for the linear applications

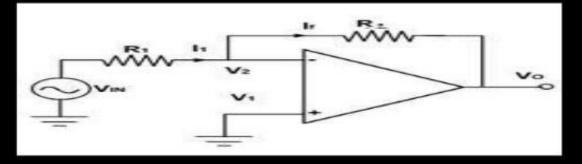

## **INVERTING OP-AMP CONFIGURATION**

## > This is a diagram of an **INVERTING OP-AMP**.

This circuit makes use of an OP-AMP, a single resistor(R1) connected to input and a feedback resistor (R2) connected to R1.

The Inverting Amplifier produces a 180° phase shift in voltage from input to output.

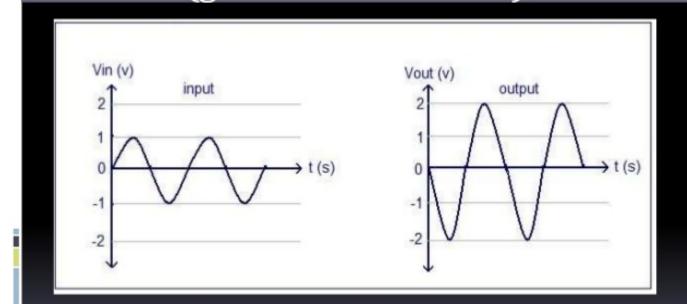

## INPUT AND OUTPUT WAVEFORMS OF AN INVERTING OP-AMP (gain assumed to be 2)

The input and output signals of the inverting amplifier are not in-phase with each other.

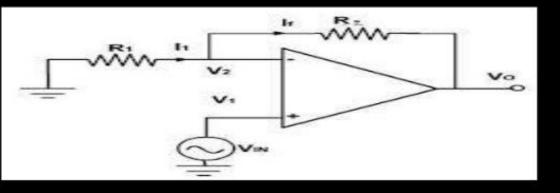

## NON INVERTING OP-AMP CONFIGURATION

## > This is a diagram of **NON-INVERTING OP-AMP**.

- This circuit consists of an OP-AMP, a single resistor (R1) connected to ground and feedback resistor (R2) connected to R1.

- Input Voltage is directly applied through the noninverting terminal.

## NON INVERTING OP-AMP CONFIGURATION

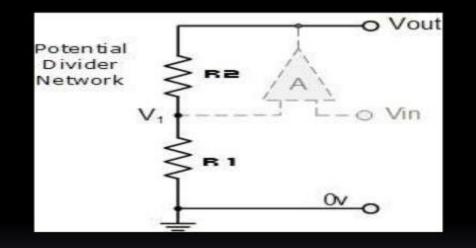

R1 and R2 form a simple potential divider network across the non-inverting amplifier with the voltage gain of the circuit being determined by the ratios of R2 and R1

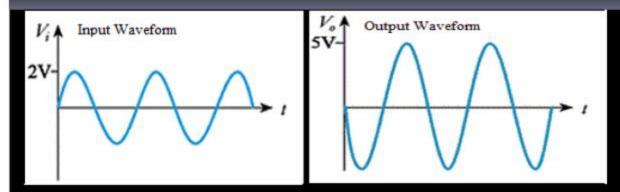

## INPUT AND OUTPUT WAVEFORMS OF AN NON INVERTING OP-AMPINVERTING OP-AMP

The input voltage signal, (Vin) is applied directly to the non-inverting (+) input terminal which means that the output gain of the amplifier becomes "Positive".

The result of this is that the output signal is "in-phase" with the input signal.

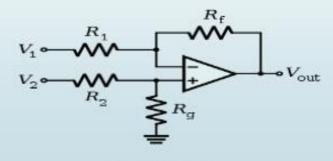

## SUMMING AMPLIFIER

Besides amplification, the op amp can perform addition and subtraction.

"A summing amplifier is an op amp circuit that combines several inputs and produces an output that is the weighted sum of the inputs"

• The summing amplifier, shown in Fig.A , is a variation of the inverting amplifier. It takes advantage of the fact that the inverting configuration can handle many inputs at the same time.

the current entering each op amp input is zero. Applying KCL at node *A* gives

$O l = l_1 + l_2 + l$

But

$$i_{1} = (v_{1} - v_{a}) \frac{1}{R_{1}}, \quad i_{2} = (v_{2} - v_{a}) \frac{1}{R_{2}} \dots (a)$$

$$i_{3} = (v_{3} - v_{a}) \frac{1}{R_{3}}, \quad i_{4} = (v_{4} - v_{a}) \frac{1}{R_{4}} \dots (b)$$

$\begin{array}{c} R_1 & 1 \\ v_1 & 0 \\ R_2 & i_2 \\ v_2 & 0 \\ \hline \\ v_3 & 0 \\ \hline \\ v_3 & 0 \\ \hline \\ \end{array} \begin{array}{c} R_3 & i_3 \\ v_3 & 0 \\ \hline \\ \end{array} \begin{array}{c} i_1 \\ i_2 \\ i_3 \\ \hline \\ v_3 \\ \hline \\ \end{array} \begin{array}{c} R_3 & i_3 \\ i_4 \\ \hline \\ v_1 \\ \hline \\ \\ v_2 \\ \hline \\ \\ v_3 \\ \hline \\ \end{array} \begin{array}{c} R_3 & i_3 \\ \hline \\ \\ v_1 \\ \hline \\ \\ v_2 \\ \hline \\ \\ v_3 \\ \hline \\ \end{array} \begin{array}{c} R_3 & i_3 \\ \hline \\ \\ v_1 \\ \hline \\ \\ v_2 \\ \hline \\ \\ v_3 \\ \hline \\ \hline \\ \\ \end{array} \right)$

We note that  $v_a = 0$  and substitute Eq. (a) / into Eq. (b). We get

$$v_0 = -(\frac{R_f}{R_1}v_1 + \frac{R_f}{R_2}v_2 + \frac{R_f}{R_3}v_3) - --(C$$

# Voltage Follower

August 27, 2009

Mukesh N. Tekwani

41

# Voltage Follower

R

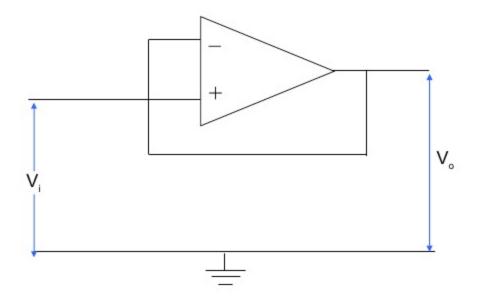

- This is a special case of the non-inverting amplifier.

- In case of non-inverting amplifier, gain A = 1 + R<sub>f</sub>

If we set  $R_f = 0$ , A = 1 (unity gain)

- This is called voltage follower because the o/p voltage is locked to the i/p voltage (both are same)

- Advantage: op amp has very high i/p impedance so it can measure V<sub>i</sub> without drawing any current.

August 27, 2009

Mukesh N. Tekwani

42

**Characteristics of Voltage Follower**

- This is a special case of the non-inverting amplifier.

- Gain A = 1

- The o/p voltage "follows" the i/p voltage

- Op amp has very high i/p impedance and very low i/p impedance

# Voltage Follower used for measuring charge

August 27, 2009

Mukesh N. Tekwani

44

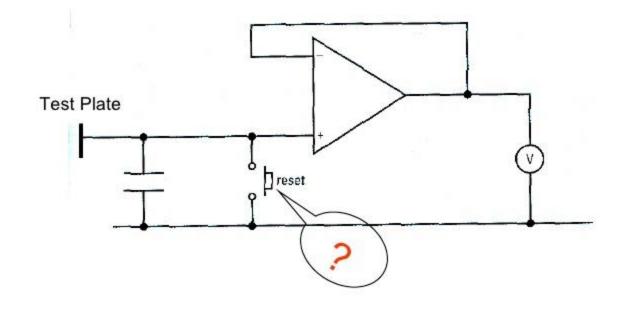

# Voltage Follower used for measuring charge

- This circuit uses a capacitor to make a chargemeasuring device.

- If a charged object touches the test plate, it will transfer charge to the capacitor.

- The p.d. between the plates of the capacitor rises

- If the capacitor is connected directly to a voltmeter, this charge will drain away through the meter and incorrect reading would be obtained.

- Op-amp has very high i/p impedance and so practically no charge is removed from the capacitor and yet measured by the voltmeter

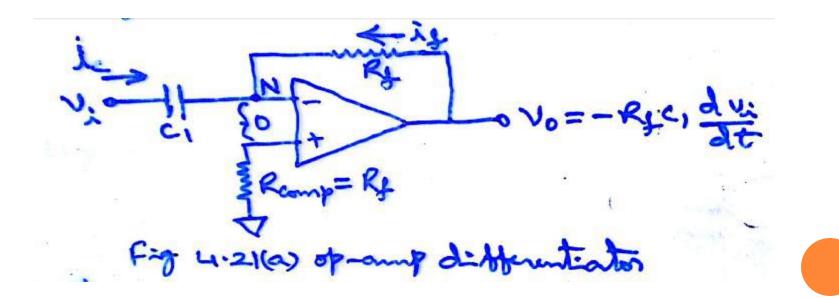

## DIFFERENTIATOR

- A differentiator is a circuit in which the output

- waveform is the derivative of input waveform.

- A differentiator circuit is shown in the figure 4.21(a).

## Analysis:

• The node N is at virtual ground potential ie Vn=0. The current ic through the capacitor is ic= C1 d(Vi-Vn)/dt = C1

dVi/dt

- The current If(not the English word if) through the feedback resistor = Vo/Rf and there is no current into the op-amp

- Therefore nodal equation at node N is C1 dVi/dt + Vo/Rf = 0 ==> Vo= -Rf C1 dVi/dt ----- eq(1)

- The minus sign indicates a 180° phase shift of the output waveform Vo with respect to the input signal.

- The phasor equivalent of equation (1). is Vo(s) = -Rf C1 S Vi(s) where Vo & Vi are the phasor representation of vo & vi.

- In steady state put s=jw. Now the magnitude of gain A of the differentiator is

- |A| = |Vo/Vi| = |-jw Rf C1| = w Rf C1 ---- eq(2)

Eq (2) may be written as

- |A| = f/fa where  $fa = 1/2\pi Rf C1$

- At f = fa, |A| = 1 ie = 0 dB, and the gain increases at a rate of +20dB/decade.

- Thus at high frequency, a differentiator may become unstable and break into oscillations .

- There is one more problem in the

- Differentiator of figure 4.21(a).

- The input impedance (ie 1/wC1) decreases

- with increase in frequency there by making

- the circuit sensitive to high frequency noise.

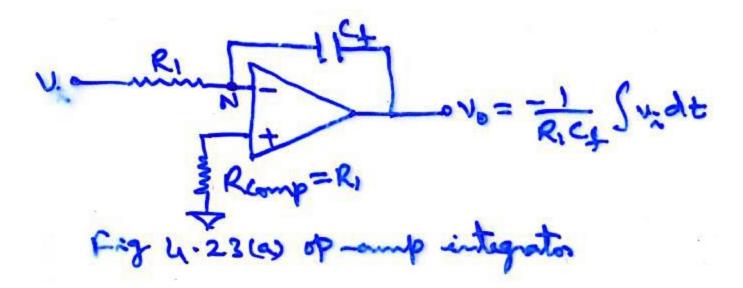

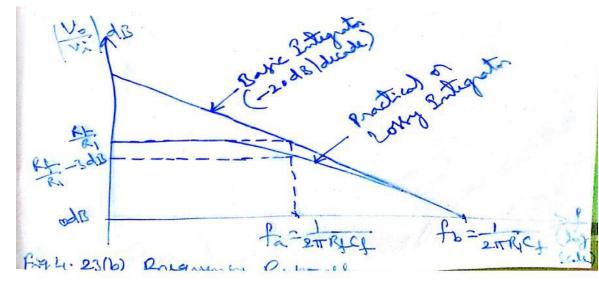

## INTEGRATOR

• By interchanging the resistor and capacitor of the Differentiator, we get the circuit of an integrator which is shown in the figure 4.23(a).

- The nodal equation at node N is (Vi/R1) + Cf dVo/dt = 0

- $\circ$  dVo/dt = -(1/R1 Cf) Vi

- $\circ$  0ft dVo = (-1/R1Cf) 0ft Vidt

- Vo(t)= (-1/R1Cf) 0/t Vi(t)dt + Vo(0) ----- eq(1) where Vo(0) is the initial o/p voltage.

- Here R1Cf is the time constant of the integrator

- Here –ve sign is present, hence it is called inverting integrator.

- Rcomp is the resistor to minimize the effect of input bias current.

- The operation of the integrator can also be studied in the frequency domain. In phasor notation the equation (1) can be written as

• Vo(s) = -(1/sR1Cf) Vi(s)

In steady state, put s=jw and we get

• Vo(jw) = -(1/jwR1Cf) Vi(jw)

# • So the magnitude of the gain is

## • |A| = |Vo(jw)/Vi(jw)| = |-1/jwR1Cf| = 1/wR1Cf = 1/(f/fb)

## Where $fb = 1/2\Pi R1Cf$

• The frequency response is shown in the figure 4.23b

- The Bode plot of basic integrator is a straight line of slope -20 dB/decade.

- The frequency fb is the frequency at which the gain of the integrator is 0 dB and is given by fb = 1/2Π R1Cf

- As the gain of the integrator decreases with increasing frequency, the integrator circuit does not have any frequency problem as faced in the differentiator.

- However, at low frequencies such as DC (w=0), the gain becomes infinite (ie saturates). The solution to this problem is a practical integrator circuit.

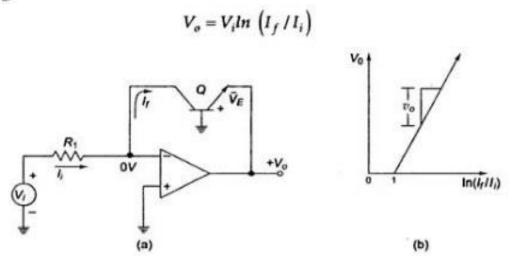

# LOG AND ANTILOG AMPLIFIER: LOG AMPLIFIER:

Log Amplifier:

Fig 2.28 Fundamental log-amp Circuit and its characteristics

There are several applications of log and antilog amplifiers. Antilog computation may require functions such as ln x, log x or sin hx.

- Uses: Direct dB display on a digital Voltmeter and Spectrum analyzer. Log-amp can also be used to compress the dynamic range of a signal.

- A grounded base transistor is placed in the feedback path. Since the collector is placed in the feedback path. Since the collector is held at virtual ground and the base is also grounded, the transistor's voltage-current relationship becomes that of a diode and is given by, = [-1] and since Ic =IE for a grounded base transistor IC = Is e kT Is-emitter saturation current ≈10-13A k=Boltzmann's constant T=absolute temperature (in o K) where Vref=R1Is

- The output voltage is thus proportional to the logarithm of input voltage. Although the circuit gives natural log (ln), one can find log10, by proper scaling Log10X=0.4343 ln X The circuit has one problem.

- The emitter saturation current Is varies from transistor to transistor and with temperature. Thus a stable reference voltage V ref cannot be obtained. This is eliminated by the circuit given below

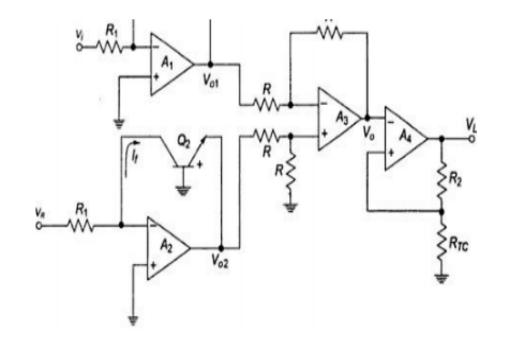

#### Fig. 2.29 Logarithmic amplifier with compensation of emitter saturation current

The input is applied to one log-amp, while a reference voltage is applied to one log-amp, while a reference voltage is applied to another log-amp. The two transistors are integrated close together in the same silicon wafer. This provides a close match of saturation currents and ensures good thermal tracking.

#### Assume IS1=IS2=IS

Thus the reference level is now set with a single external voltage source. Its dependence on device

and temperature has been removed. The voltage  $V_o$  is still dependent upon temperature and is directly proportional to T. This is compensated by the last op-amp stage A4 which provides a non-inverting gain of (1+R2/RTC). Temperature compensated output voltage  $V_L$

Fig.2.30 Logarithmic amplifier using two op amps

Where RTC is a temperature-sensitive resistance with a positive coefficient of temperature (sensor) so that the slope of the equation becomes constant as the temperature changes.

### ANTILOG AMPLIFIER

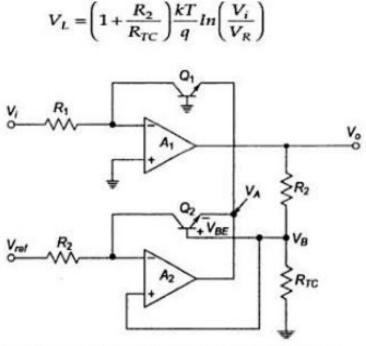

#### 2.12 Antilog Amplifier

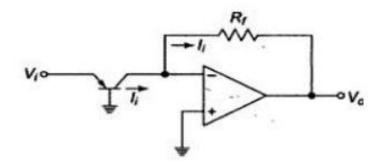

A circuit to convert logarithmically encoded signal to real signals. Transistor in inverting input converts input voltage into logarithmically varying currents

Fig. 2.31 Antilog amplifier

$$I_i = I_c = I_s(e^{\frac{\eta V_{BE}}{kT}})$$

and  $V_0 = R_f I_s(e^{\frac{\eta V_{BE}}{kT}})$

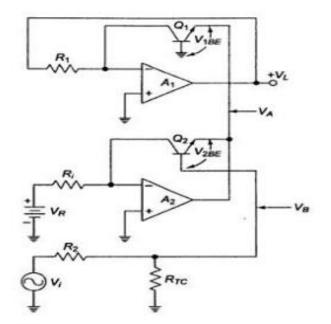

The circuit is shown in figure below. The input  $V_i$  for the antilog-amp is fed into the temperature compensating voltage divider  $R_2$  and  $R_{TC}$  and then to the base of Q2. The output of A2 is fed back to R1 at the inverting input of op amp A1. The non-inverting inputs are grounded

#### Fig 2.32 Antilog amplifier

$V_{1BE} = \frac{kT}{q} \ln[\frac{V_L}{R_1 l_s}]$  and  $V_{2BE} = \frac{kT}{q} \ln[\frac{V_B}{R_1 l_s}]$  and  $V_A = -V_{1BE}$  and  $V_B = R_{TC}/(R_2 + R_{TC}) V_i$  $V_{Q2E} = V_B + V_{2BE} = R_{TC} / (R_2 + R_{TC}) V_i - \frac{kT}{q} ln[\frac{V_B}{R_1 l_s}]$  $V_{Q2E} = V_A$ Therefor

re,

$$-\frac{kT}{q}ln\left(\frac{V_L}{R_1I_S}\right) = \frac{R_{TC}}{R_2 + R_{TC}}V_i + \frac{kT}{q}ln\left(\frac{V_R}{R_1I_S}\right)$$

Rearranging, we get

$$\begin{split} \frac{R_{TC}}{R_2 + R_{TC}} V_i &= -\frac{kT}{q} ln \left( \frac{V_L}{R_1 I_S} \right) - \frac{kT}{q} ln \left( \frac{V_R}{R_1 I_S} \right) \\ &= -\frac{kT}{q} ln \left( \frac{V_L}{V_R} \right) \end{split}$$

We know that  $\log_{10} x = 0.4343 \ln x$ .

Therefore,

$$-0.4343 \left(\frac{q}{kT}\right) \left(\frac{R_{TC}}{R_2 + R_{TC}}\right) V_i = 0.4343 \ln \left(\frac{V_L}{V_R}\right)$$

$-0.4343 \left(\frac{q}{kT}\right) \left(\frac{R_{TC}}{R_2 + R_{TC}}\right) V_i = \log_{10} \left(\frac{V_L}{V_R}\right)$

$-KV_i = \log \left(\frac{V_L}{V_R}\right)$

$K = 0.4343 \left(\frac{q}{kT}\right) \left(\frac{R_{TC}}{R_2 + R_{TC}}\right)$

$V_L = V_R 10^{-KV_i}$

• The output Vo of the antilog- amp is fed back to the inverting input of A1 through the resistor R1. Hence an increase of input by one volt causes the output to decrease by a decade.

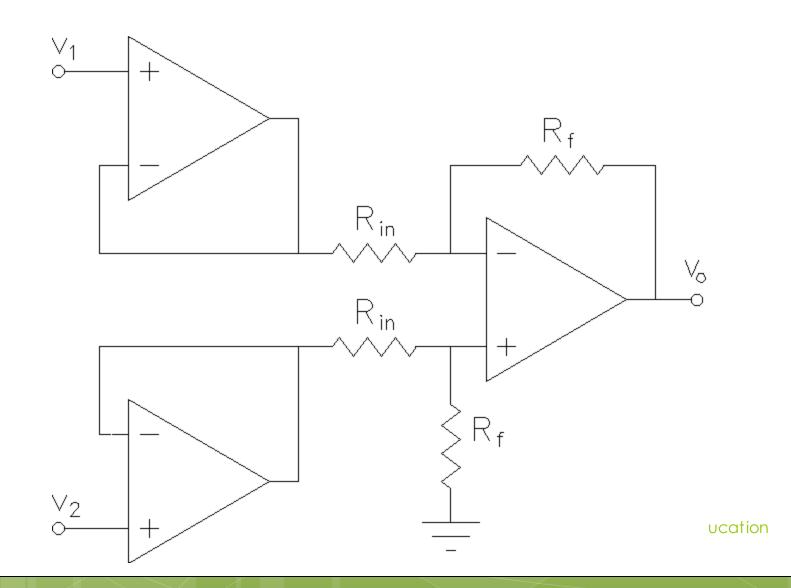

#### DIFFERENTIAL AMPLIFIER

### What is differential amplifier?

A differential amplifier is a type of electronic amplifier that amplifies the difference between two input voltages. It is an analog circuit with two inputs and one output in which the output is ideally proportional to the difference between the two voltages.

(A differential amplifier)

## Modes of operation of Differential Amplifier (DA)

- There are two modes of operations of DA

- Differential mode

- -Common mode

- <u>Differential mode:</u>

- Two input signals are of same magnitude but opposite polarity are used (180<sup>o</sup> out of phase)

- <u>Common mode</u>

- Two input signals are of equal in magnitude and same phase are used

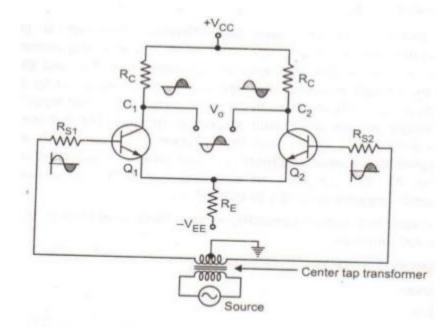

#### **Differential mode**

• Assume sine wave on base of Q1 is +ve going signal while on the base of Q2 –ve going signal

- An amplified –ve going signal will appear at collector of Q1

- An amplified +ve going signal will appear at collector of Q2

- Due to +ve going signal of base of Q1, current increases in R<sub>E</sub> & hence a +ve going wave is developed across R<sub>E</sub>

- Due to -ve going signal of base of Q2, -ve going wave is developed across R<sub>E</sub> because of emitter follower action of Q2

- So, signal voltages across R<sub>E</sub>, due to effect of Q1 &Q2 are equal in magnitude &180<sup>o</sup> out of phasedue to matched transistors

- Hence the two signals cancel each other & there is no signal across  $\mathrm{R}_\mathrm{E}$

- No AC signal flows thro it

- V<sub>o</sub>= +10-(-10)= 20

- V<sub>o</sub> is difference voltage in two signals

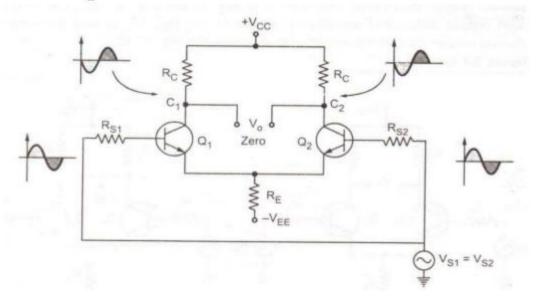

#### **Common Mode Operation**

- Two input signals are of equal in magnitude and same phase are used

- In phase signal develops in phase signal voltages across R<sub>E</sub>

- Hence R<sub>E</sub> carries a signal current & provides -ve feedback

- This –ve f/b decreases AC

- In signal voltages of equal magnitude will appear across two collectors of Q1 &Q2

- Vo= 10-10=0 Negligibly small

- Ideally it should be zero

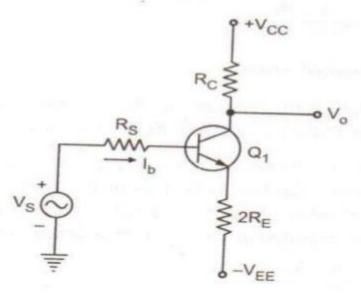

#### Analysis of evaluating 'A<sub>c</sub>'

- To evaluate A<sub>c</sub> we set V<sub>s1</sub>=V<sub>s2</sub>=Vs

- On bisecting the Diff. amp. Ckt., we get the equivalent ckt. As shown in Fig. below

- It is nothing but CE amplifier with un bypassed emitter resistor 2R<sub>E</sub>

- For calculation of A<sub>c</sub> we assume that, 2R<sub>E</sub> connected in parallel

ie  $2R_E 2R_E / 2R_E + 2R_E = R_E$

- Hybrid parameters equations are taken directly for CE amplifier with un bypassed emitter resistor but value of emitter resistor can taken as "2R<sub>E</sub>"

- $A_1 = (h_{oe} R_E h_{fe}) / (1 + h_{oe} (R_C + R_E))$ =  $(h_{oe} (2R_E) - h_{fe}) / (1 + h_{oe} (R_C + 2R_E))$

• Ri=  $(1 - A_I)R_E + hie + hre A_IR_L$

=

$$(1 - A_1) 2R_E + hie + hre A_1 R_L$$

Where  $R_L = R_C + (A_I - 1/A_I)R_E$

$$R_{L} = R_{C} + (A_{I} - 1/A_{I}) 2R_{E}$$

- $A_c = A_l Rc/Ri+Rs$  (Since  $A_v = (A_l Rc)/Ri$ )

- In Ri expression neglecting the term hre A<sub>I</sub> R<sub>L</sub> and substitute A<sub>I</sub> and Ri we get,

A<sub>c</sub> =((2hoe R<sub>E</sub> - hfe)Rc)/(2 R<sub>E</sub>(1+ hfe)+(Rs+hie)(2hoe R<sub>E</sub> +1)) Provided that hoe Rc<<1

- If we use approximate model we get simpler expression

- A<sub>c</sub> = hfe Rc/Rs+hie+ (1+hfe)2R<sub>E</sub>

## Evaluating 'A<sub>d</sub>'

- We set V<sub>s1</sub>= -V<sub>s2</sub>= Vs/2

- ie magnitude of AC I/P voltages is set as above

- I<sub>e1</sub>= -I<sub>e2</sub>, I<sub>o</sub>= 0 (They cancel each other to get resultant ac current thro R<sub>E</sub> as I<sub>0</sub>=0)

- Hence for ac analysis emitter terminal can be grounded

- Bisecting the ckt with R<sub>E</sub> = 0

- We get equi. Ckt which is conventional CE amplifier

- Ac small signal Diff.Amp.

ckt with grounded emitter

is shown here

- As two trs. are matched ac equi. Ckt of the other Ckt is identical

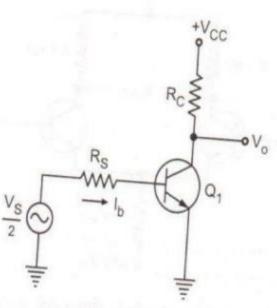

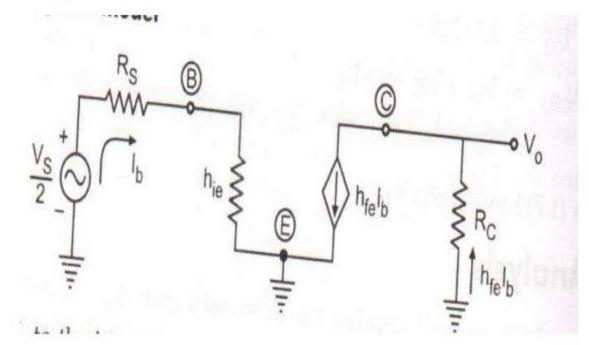

Approximate hybrid model for the above ckt is shown here

Applying KVL to the input loop,

$$-I_b R_S - I_b h_{ie} + \frac{V_S}{2} = 0 \quad (1)$$

$$\therefore -I_b (R_S + h_{ie}) = -\frac{V_S}{2}$$

$$\therefore I_b = \frac{V_S}{2(R_S + h_{ie})} \quad (2)$$

Applying KVL to the output loop,

$$V_o = -h_{fe} I_b R_C$$

(3)

Substituting (2) in (3),

$$V_o = -h_{fe} R_C \frac{V_S}{2(R_S + h_{ie})}$$

- -ve sign indicates phase difference between I/P &O/P  $\frac{V_o}{V_S} = \frac{-h_{fe} R_C}{2(R_S + h_{ie})}$

- Here Vs difference I/P

• Mod of Ad is

$$A_d = \frac{V_o}{V_S} = \frac{h_{fe} R_C}{2(R_S + h_{ie})}$$

• CMRR is =  $\left|\frac{Ad}{Ac}\right|$

## Method of improving CMRR

Effect of R<sub>E</sub>:

- To improve CMRR, 'Ac' must be reduced

- "Ac" approaches zero as R<sub>E</sub> tends to infinite

- Because R<sub>E</sub> introduces <u>–ve feedback</u> which reduces 'Ac'

- Higher value of R<sub>E</sub>, lesser the Ac, higher the value of CMRR

- 'Ad' is independent of R<sub>E</sub>

- But practically R<sub>E</sub> cannot be selected very high due to some limitations

- –Large R<sub>E</sub> needs higher biasing voltage to set

Q-pt

( Under Dc cond Ic= $\beta I_B$  but  $I_E = I_C$   $I_B = I_E / \beta$

$-I_E$  depends on  $\beta$

- –To make Q-pt stable  $I_E$  should be constant irrespective of  $\beta$

- –For constant  $I_E$  emitter R should be very large this increases CMRR, )

- Increases overall chip area

- So various methods are used which provide increased effect of R<sub>E</sub> without any limitations

- 1. Constant current bias method

- 2. Use of current mirror method

- Another method to improve "Ad" to increase CMRR is Active load

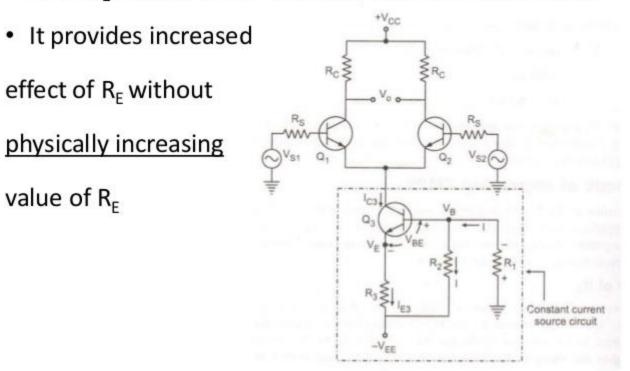

#### **Differential Amplifier with constant current circuit**

Here R<sub>E</sub> is replaced by constant current source circuit

- R1, R2, R3 are selected to give the same operating point for Q1&Q2

- Let current thro R3 is I<sub>E3</sub> and Current R1 is "I"

- Neglect base current(Because of large β)

- Assume current thro R2 is also "I"

Applying Kirchhoff's law,

$$- IR_1 - IR_2 + V_{EE} = 0$$

$$\therefore I = \frac{V_{EE}}{R_1 + R_2}$$

Now

$V_B = -IR_1$

Negative sign according to the direction of current .

$$\therefore V_{\rm B} = -\frac{V_{\rm EE} R_{\rm I}}{R_{\rm I} + R_{\rm 2}} \qquad ...(2)$$

Now

$$V_E = V_B - V_{BE}$$

and

$$I_{E3} = \frac{V_E - (-V_{EE})}{R_3}$$

Substituting expressions for  $V_{B}$  and  $V_{E}\,\text{,}$

$$\therefore I_{E3} = \frac{\frac{-V_{EE} R_1}{R_1 + R_2} - V_{BE} + V_{EE}}{R_3}$$

$$\therefore I_{E3} = \frac{V_{EE} \left[\frac{R_2}{R_1 + R_2}\right] - V_{BE}}{R_3}$$

Neglecting  $I_{B3}$  we can write

$I_{C3} = I_{E3}$

...(1)

...(3)

...(4)

- Thus as V<sub>EE</sub>, R1, R2, R3 & V<sub>BE</sub> are constant, Current <u>I<sub>C3</sub> is almost equal to I<sub>E3</sub></u> and also constant.

- Thus ckt with Tr Q3 acts as a constant current source.

- Internal Resistance of a cont. current source is very high, ideally infinite

- Hence this ckt makes <u>the value of R<sub>E</sub> ideally</u> infinite which reduces Ac ideally to zero

## COMMON MODE REJECTION RATIO (CMRR):

- It can be defined as the ratio of the differential

- gain AD to the common mode gain Acm, that is

- $\circ$  CMRR = Ad/Acm

- – It is a measure of the degree of matching between two input terminals, that is, the larger the value of CMRR, the better is the matching between the two input terminals and the smaller is the output common mode voltage Vocm.

# THANK YOU

Karpagam Academy of Higher Education

UNIT-2 APPLICATIONS OF OPAMPS

> Prepared by S.JAYACHITRA,AP/ECE

1

## Comparator

- A comparator is a circuit which compares a

- signal voltage applied at one input of an

- op-amp with a known reference voltage at the

- other input.

- There are basically two types of comparators.

- I. Non-inverting comparator

- 2. Inverting comparator

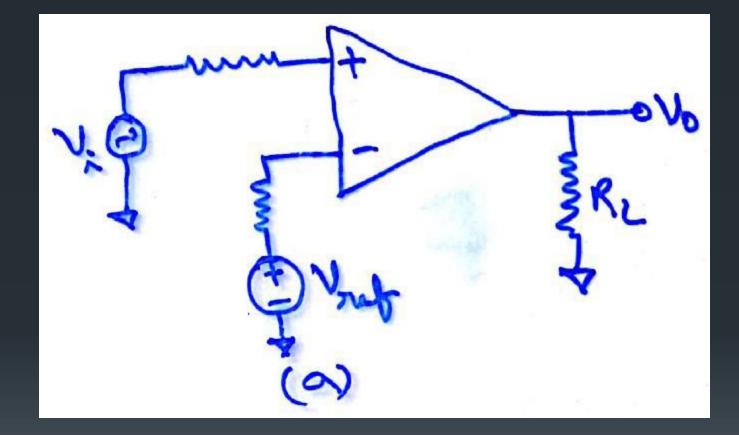

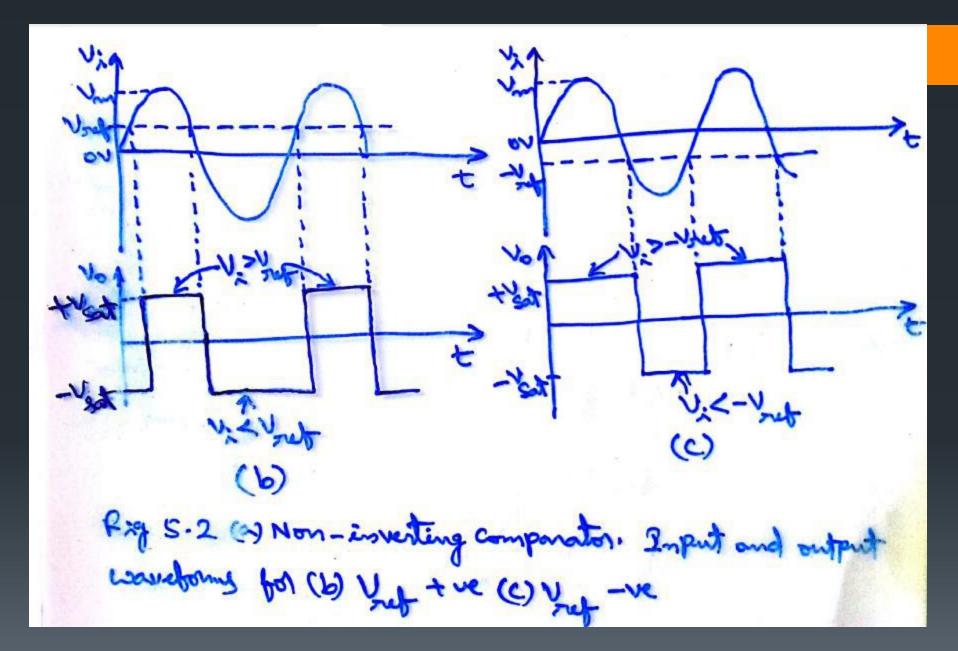

# **Non-Inverting Comparator:**

- The circuit of figure 5.2a is called a non-inverting

- comparator.

- A fixed reference voltage Vref is applied to

- Input and a time varying signal Vi is applied to

- +input.

- There are 3 conditions for a comparator. They are

- Vi < Vref □ Vo = -Vsat</p>

- Vi > Vref  $\Box$  Vo = +Vsat

- Vi = Vref  $\Box$  changes the state of op-amp

- The output waveform for a sinusoidal input

- signal applied to the +ve input is shown in

- figure 5.2 (b) and (c) for +ve and -ve Vref

- respectively.

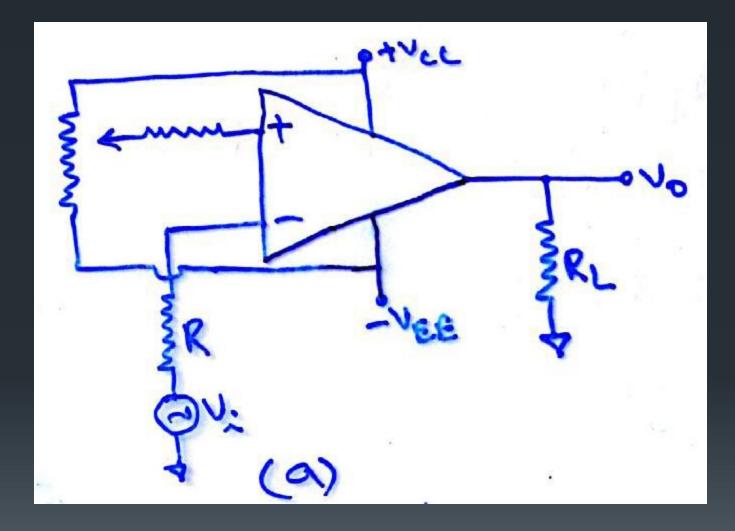

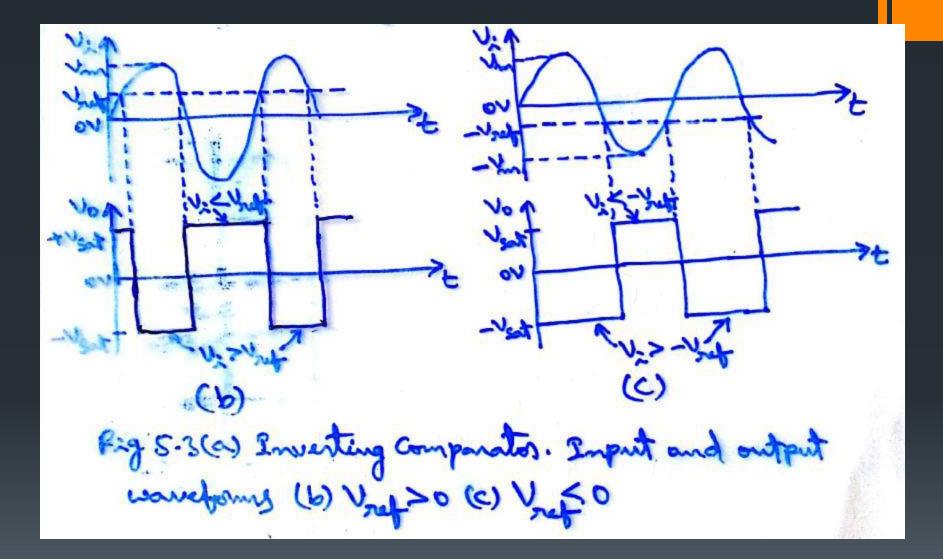

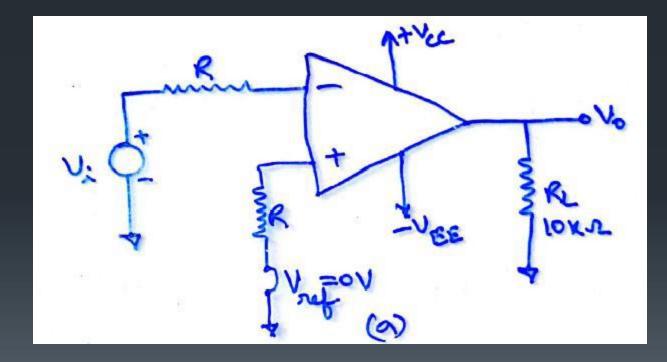

# **Inverting Comparator:**

- Figure 5.3(a) shows a practical inverting

- comparator in which the reference voltage

- Vref is applied to the +input and Vi is applied

- to the –ve input.

- For a sinusoidal input signal, the output

- waveform is shown in in figure 5.3(b) and

- 5.3(c) for Vref +ve and –ve respectively.

#### **Applications of Comparator**

- Some important applications of comparator are

- Zero crossing detector

- Window detector

- Time marker generator

- Phase meter.

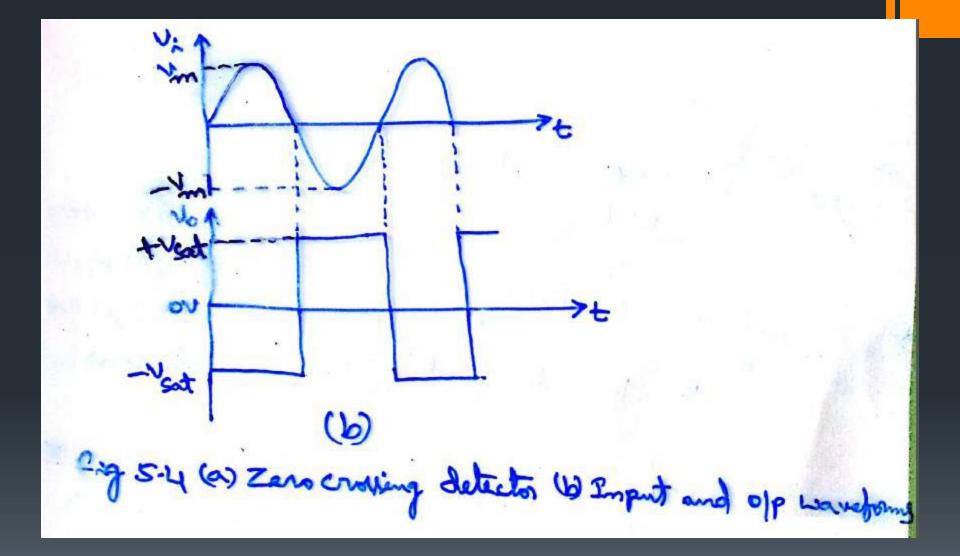

#### **Zero crossing detector**

- The basic comparators either non-inverting or

- inverting can be used as a zero crossing

- detector provided that Vref is set to zero. An

- inverting zero-crossing detector is shown in

- figure 5.4 (a).

- The input and output waveforms are shown in

- Figure 5.4 (b).

- The circuit is also called as a sine to square wave generator.

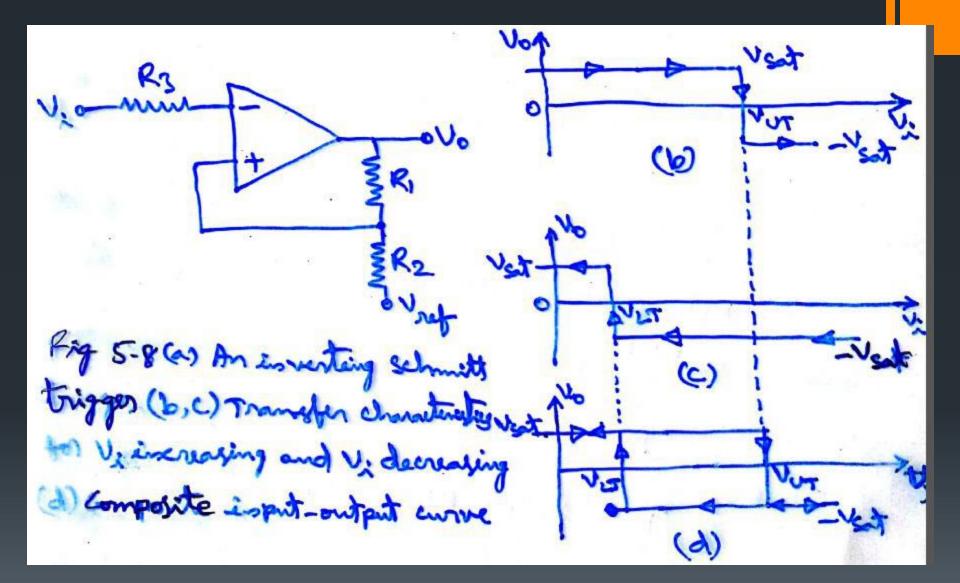

# Regenerative comparator (Schmitt trigger)

- If positive feedback is added to the

- comparator circuit, gain can be increased

- greatly.

- Figure 5.8 (a) shows a regenerative

- comparator. The circuit is also known as

- Schmitt trigger

- The input voltage Vi triggers the output Vo every

- time it crosses certain voltage levels. These

- voltage levels are called Upper threshold voltage

- (Vut) and Lower threshold voltage (Vlt).

- The hysteresis width is the difference between

- these two threshold voltages ie Vut Vlt. These

- threshold voltages are calculated as follows.

- Suppose that the output voltage Vo is +Vsat. The

- voltage at +ve input terminal will be

- Vref + (R2/(R1+R2)) (Vsat Vref) = Vut

- This voltage is called as Upper threshold voltage Vut

- As long as Vi is less than Vut, the output Vo remains

- constant at +Vsat. When Vi is just greater than Vut, the

- output regeneratively switches to Vsat and remains

- at this level as long as Vi > Vut as shown in Figure 5.8

(b).

- For Vo = -Vsat, the voltage at +ve input terminal is

- Vref + (R2/R1+R2) (-Vsat Vref) = Vlt

- Vref (R2/R1+R2) (Vsat + Vref) = VIt

- this voltage is referred to as lower threshold voltage VIt

- The input voltage Vi must become lesser than VIt

- in order to cause Vo to switch from –Vsat to

- +Vsat. A regenerative transition takes place as

- shown in Figure 5.8(c) and the output Vo returns

- from –Vsat to +Vsat almost instantaneously.

- The complete transfer characteristics are shown

- in Figure 5.8 (d).

- Note that VIt < Vut and the difference between</li>

- these two voltages is the hysteresis width Vh and

- can be written as

- Vh = Vut Vlt = 2R2 Vsat/(R1+R2)

- The resistor R3 in figure 5.8(a) is chosen equal

- to R1||R2 to compensate for the input bias

- current.

- A non-inverting Schmitt trigger is obtained if

- Vi and Vref are interchanged in figure 5.8(a).

## **Wave form Generators**

- There are different types of wave form

- generators which are given below.

- I Square wave generator

- 2 Triangular wave generator

- 3 Saw tooth wave generator

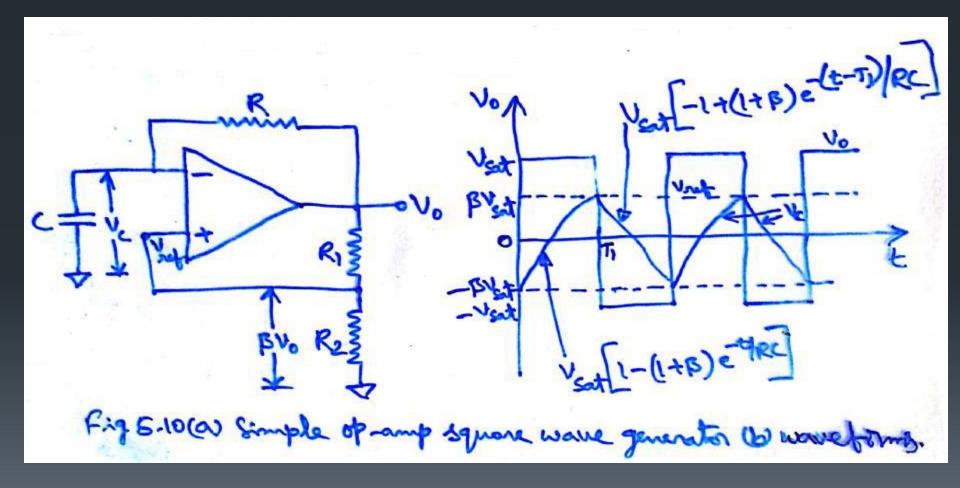

- Square wave Generator (Astable Multivibrator)

- A simple op-amp square wave generator is

- shown in Figure 5.10a.

#### Square wave generator

- It is also called a Free running oscillator.

- The principle of generation of square wave

- output is to force an op-amp to operate in

- saturation region.

- In Figure 5.10(a), fraction  $\beta = R2/(R1+R2)$  of

- the output is fed back to the +ve input

- terminal. Thus the reference voltage Vref is

- $\beta$ Vo and may take values as + $\beta$ Vsat or  $\beta$ Vsat.

- The output is also fed back to the –ve input

- terminal after integrating by means of a low

- pass RC combination.

- Whenever input at the -ve input terminal just

- exceeds Vref, switching takes place resulting in

- a square wave output.

- In Astable multivibrator, both the states are

- quasi stable.

#### Frequency Derivation

- The frequency is determined by the time it takes the capacitor

- to charge from  $-\beta$ Vsat to +  $\beta$ Vsat and vice versa.

- The voltage across the capacitor as a function of time is given

- by

- $Vc(t) = Vf + (Vi Vf) e^{t/RC}$

- where, the final value, Vf = +Vsat

- and the initial value,  $Vi = -\beta Vsat$

- Therefore Vc(t) = +Vsat + (-βVsat Vsat) e^-t/RC

- $Vc(t) = Vsat Vsat(1+\beta) e^{-t/RC}$

- At t = T1, voltage across the capacitor reaches  $\beta$ Vsat and

- switching takes place.

- Therefore

- $Vc(T1) = \beta Vsat = Vsat Vsat(1 + \beta) e^{T1/RC}$

- After algebraic manipulation, we get

- T1 = RC ln  $(1 + \beta)/(1 \beta)$

- This gives only one half of the period.

- Therefore the total time period, T

- =  $2^{T1} = 2RC \ln (1 + \beta)/(1 \beta)$  and the output waveform

- is symmetrical.

- If R1 = R2, then  $\beta$  = 0.5 and T = 2RC In 3 and

- for R1=1.16 R2, it can be seen that

- T = 2RC or fo = 1/2RC

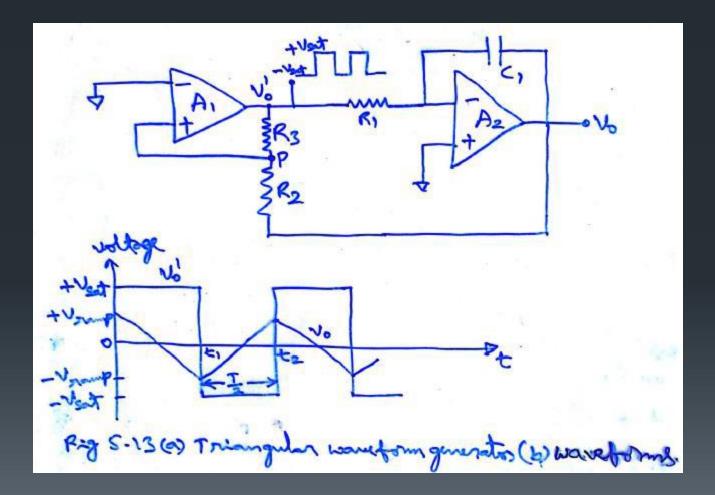

### **Triangular Wave Generator**

- It basically consists of a two level comparator

- followed by an integrator.

- The output of the comparator A1 is a square

- wave of amplitude + or Vsat and is applied

- to the –ve input terminal of the integrator A2

- producing a triangular wave. This triangular

- wave is fed back as input to the comparator

- A1 through a voltage divider R2R3.

- Initially, let us consider that the output of the

- comparator A1 is at +Vsat. The output of the

- integrator A2 will be a –ve going ramp as shown

- in figure 5.13b. This one end of the voltage

- divider R2R3 is at a voltage +Vsat and the other at

- the –ve going ramp of A2.

- At a time t=t1, when the -ve going ramp attains a

- value of –Vramp, the effective voltage at point p

- becomes slightly less than 0 volts. This switches

- the output of A1, from positive saturation level to

- negative saturation level Vsat.

- During the time when the output of A1 is at -Vsat,

- the output of A2 increases in the positive direction.

- And at the instant t=t2, the voltage at point p becomes

- just above 0 volts, thereby switching the output of A1

- from –Vsat to +Vsat. The cycle repeats and generates a

- triangular waveform.

- It can be seen that the frequency of the square wave

- and triangular wave will be the same.

- However, the amplitude of the triangular wave

- depends upon the RC value of the integrator A2 and

- output voltage level of A1.

#### Derivation of Frequency of Triangular Waveform

- The effective voltage at point p during the time

- when output of A1 is at +Vsat level is given by

- -Vramp+(R2/(R2+R3)) [+Vsat (-Vramp)] -- Eq(1)

- At t=t1, the voltage at point p becomes

- approximately equal to zero. Therefore from

- Eq(1), we get -Vramp = (-R2/R3) (+Vsat)

- Similarly at t=t2, when the output of A1 switches

- from –Vsat to +Vsat

- Vramp = (-R2/R3) (-Vsat) = (R2/R3) Vsat

- Therefore peak to peak amplitude of the triangular wave is

- Vo (pp) = +Vramp (-Vramp)

- Vo (pp) = 2 Vramp = 2 (R2/R3) Vsat ---- Eq(2)

- The output switches from –Vramp to +Vramp in half the time

period T/2.

- Putting the values in the basic integrator equation Vo = -

- (1/RC) ∫Vi dt, we get

- Vo(pp)=-(1/R1C1) 0∫T/2 (-Vsat)dt =(Vsat/R1C1) (T/2)

- Therefore T=2 R1C1 Vo(pp)/Vsat

- Putting the value of Vo(pp) from Eq(2), we get

- T = 4R1 C1 R2/R3

- Hence the frequency of oscillation fo is

- fo = 1/T = R3/4 R1 C1 R2

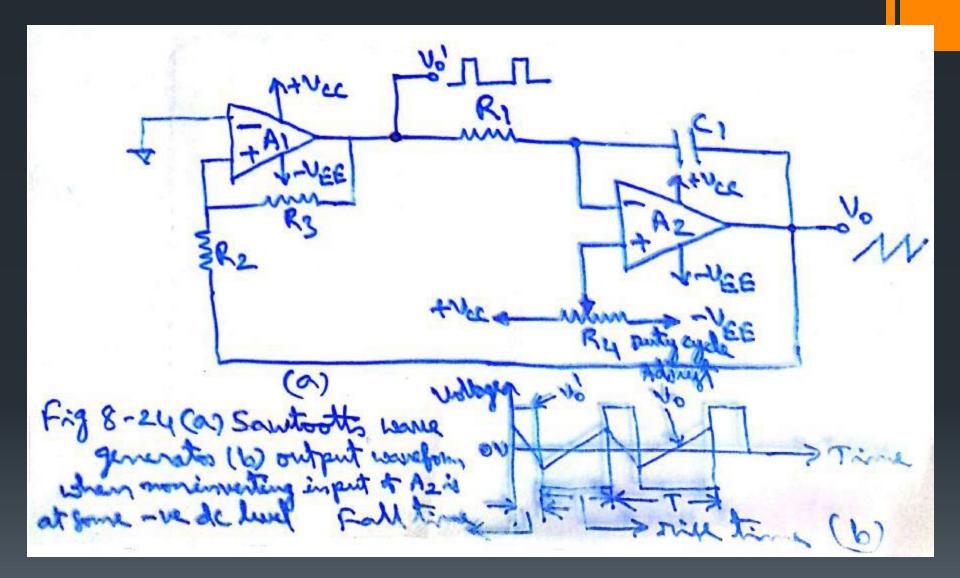

## **Sawtooth Wave Generator**

- The difference between the triangular and

- sawtooth waveforms is that

- rise time and fall time are equal Triangular

- rise time and fall time are unequal Sawtooth

- The triangular wave generator can be converted

- into a sawtooth wave generator by injecting a

- variable DC voltage into the non-inverting

- terminal of the integrator A2.

- This can be accomplished by using the

- potentiometer and connecting it to the +Vcc and

- -Vee as shown in Figure 8-24(a)

- Depending on the R4 setting, a certain DC level is

- inserted in the output of A2.

- Now suppose that the output of A1 is a square wave

- and the potentiometer R4 is adjusted for a certain DC

- level.

- This means that the output of A2 will be a triangular

- wave, riding on some DC level that is a function of the

- R4 setting.

- The duty cycle of the square wave will be determined

- by the polarity and amplitude of this DC level.

- A duty cycle less than 50% will then cause the output

- of A2 to be a sawtooth.

- With the wiper at the center of R4, the output

- of A2 is a triangular wave. For any other

- position of R4 wiper, the output is a sawtooth

- waveform.

- R4 wiper is towards –Vee, the rise time is more

- R4 wiper is towards +Vcc, the fall time is more

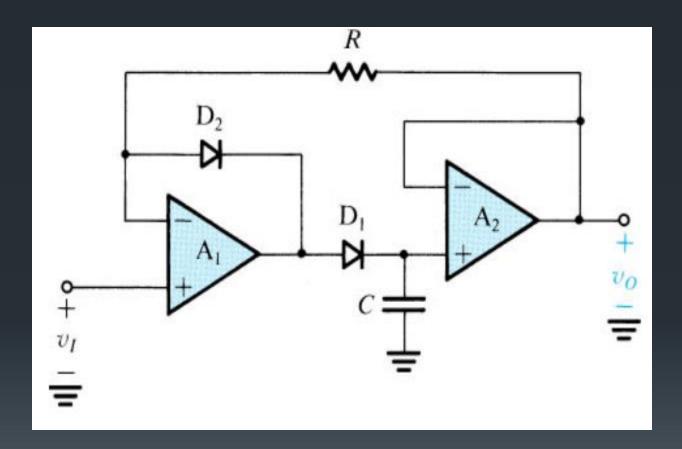

#### **Precision Peak Detector**

- When the peak detector required to hold the value of the peak for a long time, the capacitor should be buffered. An op amp A 2, which should have high input impedance and low input bias current, is connected as a voltage follower.

- The rest of the circuit is similar to the half-wave rectifier. A Precision Clamping Circuit By replacing the diode in the usual clamping circuit with

#### Linear Oscillators

- 1. Wien Bridge Oscillators

- 2. RC Phase-Shift Oscillators

- 3. LC Oscillators

- 4. Stability

Ref:06103104HKN

EE3110 Oscillator

4

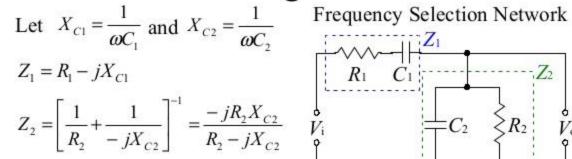

#### Wien Bridge Oscillator

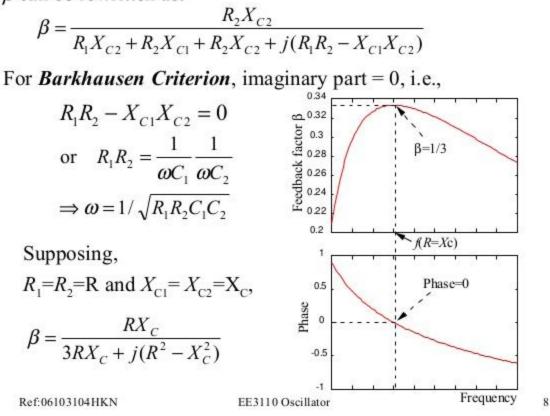

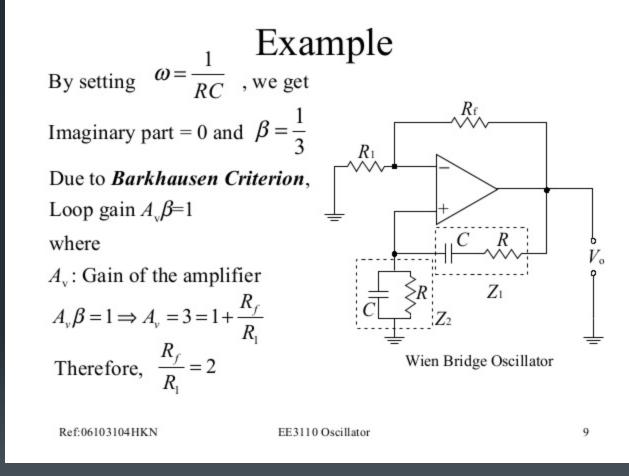

Therefore, the feedback factor,

$$\beta = \frac{V_o}{V_i} = \frac{Z_2}{Z_1 + Z_2} = \frac{(-jR_2X_{C2}/R_2 - jX_{C2})}{(R_1 - jX_{C1}) + (-jR_2X_{C2}/R_2 - jX_{C2})}$$

$$\beta = \frac{-jR_2X_{C2}}{(R_1 - jX_{C1})(R_2 - jX_{C2}) - jR_2X_{C2}}$$

Ref:06103104HKN EE3110 Oscillator

7

$\beta$  can be rewritten as:

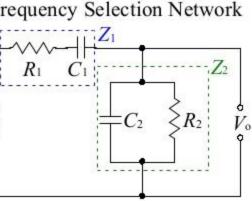

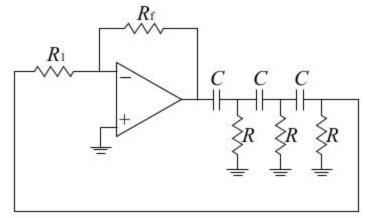

## **RC Phase-Shift Oscillator**

- Using an inverting amplifier

- The additional 180° phase shift is provided by an RC phase-shift network

Ref:06103104HKN

EE3110 Oscillator

10

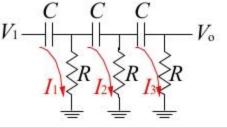

Applying KVL to the phase-shift network, we have

$$V_{1} = I_{1}(R - jX_{C}) - I_{2}R$$

$$0 = -I_{1}R + I_{2}(2R - jX_{C}) - I_{3}R$$

$$0 = -I_{2}R + I_{3}(2R - jX_{C})$$

Solve for  $I_3$ , we get

$$I_{3} = \begin{vmatrix} R - jX_{C} & -R & V_{1} \\ -R & 2R - jX_{C} & 0 \\ 0 & -R & 0 \end{vmatrix} \begin{vmatrix} R - jX_{C} & -R & 0 \\ -R & 2R - jX_{C} & -R \\ 0 & -R & 2R - jX_{C} \end{vmatrix}$$

Or

$$I_3 = \frac{V_1 R^2}{(R - jX_C)[(2R - jX_C)^2 - R^2] - R^2(2R - jX_C)}$$

Ref:06103104HKN

EE3110 Oscillator

11

The output voltage,

$$V_o = I_3 R = \frac{V_1 R^3}{(R - jX_C)[(2R - jX_C)^2 - R^2] - R^2(2R - jX_C)}$$

Hence the transfer function of the phase-shift network is given by,

$$\beta = \frac{V_o}{V_1} = \frac{R^3}{(R^3 - 5RX_C^2) + j(X_C^3 - 6R^2X_C)}$$

For  $180^{\circ}$  phase shift, the imaginary part = 0, i.e.,

$$X_{C}^{3} - 6R^{2}X_{C} = 0 \text{ or } X_{C} = 0 \text{ (Rejected)}$$

$$\Rightarrow X_{C}^{2} = 6R^{2}$$

$$\omega = \frac{1}{\sqrt{6RC}}$$

$$\beta = -\frac{1}{2}$$

Note: The -ve sign mean the phase inversion from the voltage

and,

$$\beta = -\frac{1}{29}$$

Ref:06103104HKN

EE3110 Oscillator

12

THANK YOU

# UNIT-III FILTERS

# Prepared by S.JAYACHITRA,AP/ECE

Karpagam Academy of Higher Education

#### **DEFINATION**

A Filter is an electrical circuit that is designed to pass a specified band of frequencies while attenuating all the signals outside that band.

It is a frequency selective circuit.

The filters are basically classified as active filters & passive filters.

They are used in circuits which require the separation of signals according to their frequencies.

They are widely use in communication & signal Processing.

### <u>GENERAL</u>

- A Filter is an electrical circuit that is designed to pass a specified band of frequencies while attenuating all the signals outside that band.

- It is a frequency selective circuit.

- The filters are basically classified as active filters & passive filters.

- They are used in circuits which require the separation of signals according to their frequencies.

- They are widely use in communication & signal processing.

## ADVANTAGES OF ACTIVE FILTERS OVER PASSIVE FILTERS

- All the elements alongwith op-amp can be used in the integrated form. Hence there is reduction in size & weight.

- The op-amp gain can be easily controlled in the closed loop fashion hence active filter I/P signals is not attenuated.

- The op-amp has high I/P impedance & low O/P impedance, hence the active filters using op-amp do not cause loading of the source or load.

#### **LIMITATIONS OF ACTIVE FILTERS**

- The finite bandwidth of the active devices places a limit on the highest frequency of operation.

- A reasonably good filter performance can be achieved approximately upto 500 kHz, as against this passive filters can be used upto 500 MHz.

- The active elements are more sensitive to the temperature & environmental changes than the passive elements.

- The requirement of d.c power supply is another disadvantage of the active filters.

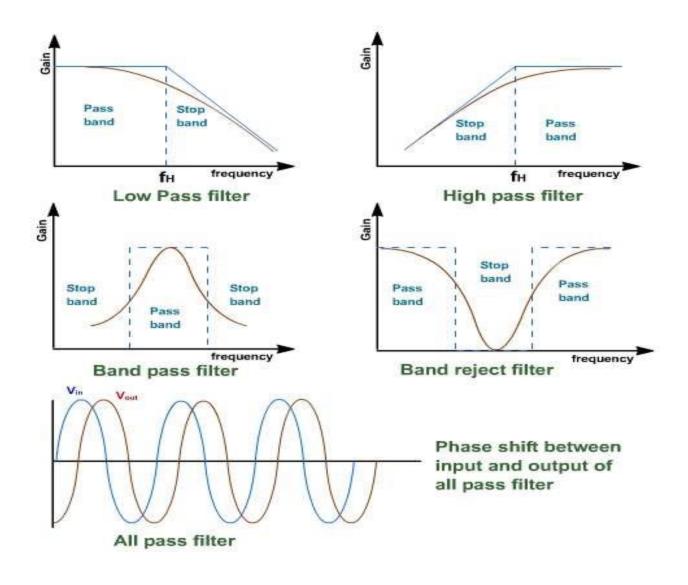

## **COMMONLY USED FILTERS**

- The most commonly used filters are :-

- Low Pass Filter

- High Pass Filter

- Band Pass Filter

- Band Reject Filter

- All Pass Filter &

- Universal Filters.

## **1- LOW PASS FITER**

- A low-pass (LP) filter is a filter that passes lowfrequency signals but attenuates (reduces the amplitude of) signals with frequencies higher than the cutoff frequency.

- A low-pass (LP) filter is the opposite of a highpass (HP) filter.

#### FREQUENCY RESPONSE OF LOW PASS FILTER IDEAL & PRACTICAL RESPONSE

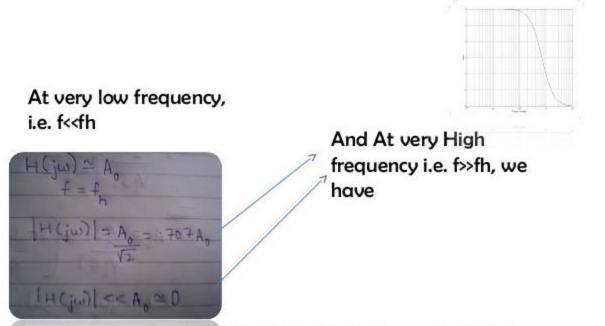

- A Low Pass Filter has a constant gain from 0 Hz to a high cutoff frequency, f<sub>h</sub>.

- Practically, the gain decreases as the frequency increases & at f= f<sub>b</sub>, the gain is down by 3 db & after f<sub>b</sub>; it decreases at a higher rate.

- After the end of a transition band,

- the gain becomes zero.

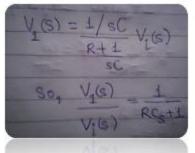

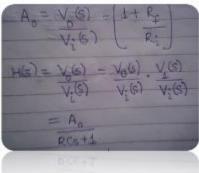

#### First Order LP Filter

- A first order filter consists of a single RC n/w connected to I / p terminal of a non-inverting op-amp.

- Resistors R, & R, determine the gain of the filter in the pass band.

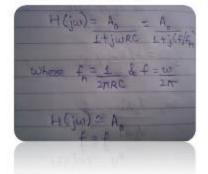

Active filters are typically specified b voltage Toansker Story state conditions (i.e. s -samitude response is given in do as 20 Log [H ( Ju)] (0)

#### The voltage across the capacitor in the s-domain is:-

The closed loop gain of the op-amp is:-

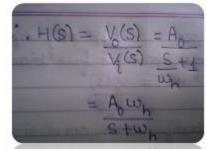

#### Let wh= 1/RC

To determine the frequency response, put s=jw in above eq.

It has the max. gain at f=0 Hz. At fh the gain falls to . 707 time the max. gain. Hence gain rolls off at the rate of 20 dB/decade.

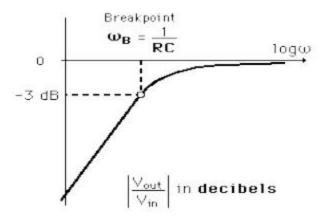

#### 2- A HIGH PASS FILTER

A high-pass (HP) filter offers easy passage to high-frequency signal and attenuates the lowfrequency signal.

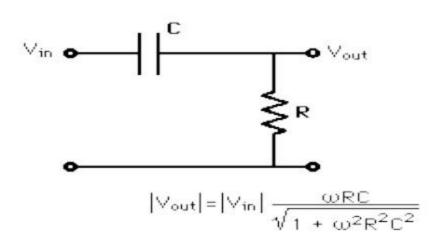

#### A PASSIVE HIGH PASS FILTER:

#### Frequency response of 1st order HP Filter

The cutoff frequency for a high-pass filter is that frequency at which the output voltage equals 70.7% of the input voltage. Above the cutoff frequency, the output voltage is greater than 70.7% of the input, and vice versa.

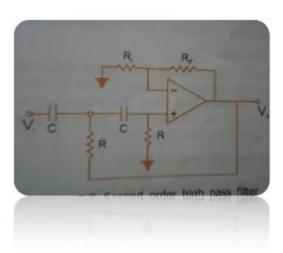

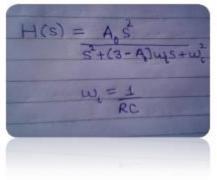

#### 2<sup>ND</sup> ORDER HP FILTER

High pass filter is the complement of the low pass filter & can be obtained simply by interchanging R & C in the low pass configuration as shown in the fig.

This is the transfer function:

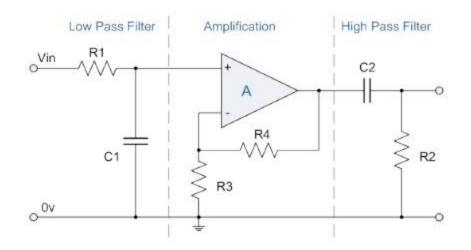

#### **3- BAND PASS FILTER**

The Band-Pass (BP) filter passes a selected range or band of frequencies that can be either narrow or wide while attenuating all those outside of this range.

## Band pass filter

- A band-pass filter is a device that passes frequencies within a certain range and rejects (attenuates) frequencies outside that range.

- These filters can also be created by combining a low-pass filter with a high-pass filter.

- The <u>bandwidth</u> of the filter is simply the difference between the upper and lower cutoff frequencies.

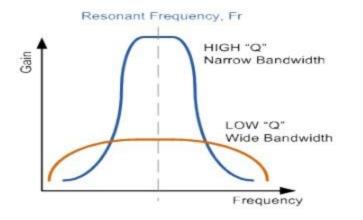

- Q factor:-

- A band-pass filter can be characterised by its Q factor. The Q-factor is the inverse of the fractional bandwidth. A high-Q filter will have a narrow passband and a low-Q filter will have a wide passband. These are respectively referred to as narrow-band and wide-band filters.

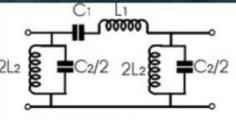

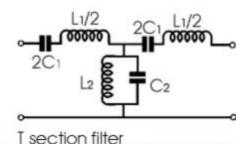

## Band pass with LC components

Like the high pass filters and the low pass filters, there are two topologies that are used for 2L2 these filters, namely the Pi and the T configurations. Rather than having a single element in each leg of the filter as in the case of the low pass and high pass filters, the band pass filter has a resonant circuit in each leg. These resonant circuits are either series or parallel tuned LC circuits.

#### **TYPES OF BP FILTER**

- Broad-band Band-Pass filter

- Narrow-band Band-Pass filter

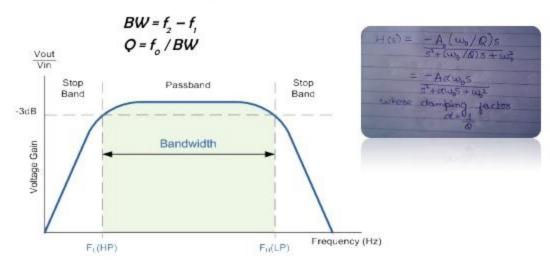

#### <u>Frequency Response of a 2<sup>nd</sup> order Band-Pass</u> (BP) FILTER:

- The term "bandwidth" refers to the difference between the lower cut-off frequency (fc<sub>unen</sub>) and the upper cut-off frequency (fc<sub>unen</sub>) points.

- A band-pass (BP) filter arrangement commonly consists of a combination of a Low-pass (LP) and a High-pass (HP) filter.

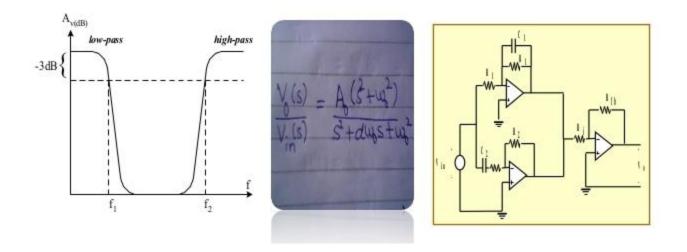

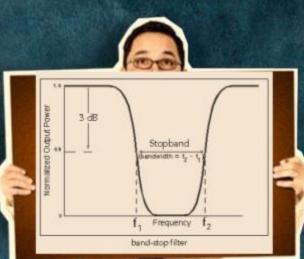

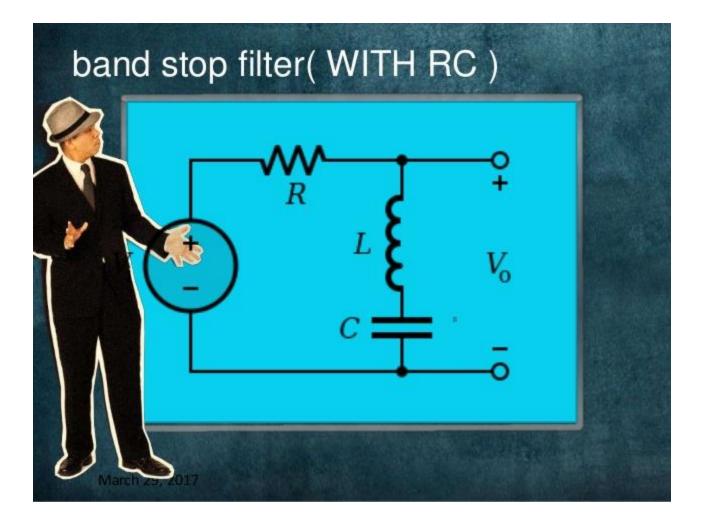

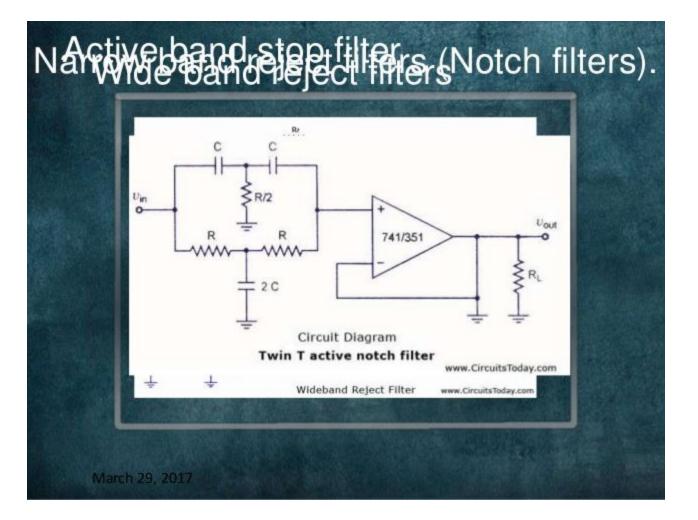

#### **4- BAND REJECT FILTER**

This can also be either as a Narrow or wide band reject filter. The narrow band reject filter is commonly called a notch filter & is useful for the rejection of a single frequency, such as 50 Hz power line frequency hum.

## Band stop or band rejection filter

- In signal processing, a band-stop filter or bandrejection filter is a filter that passes most frequencies unaltered, but attenuates those in a specific range to very low levels.

- It is the opposite of a band-pass filter. A notch filter is a band-stop filter with a narrow stop band\_ March (high Q factor).

#### **ALL PASS FILTER**

- An all-pass filter passes all frequency components of the i/p signal without any attenuation & provides desired phase shifts at different frequencies of the I/P signal.

- When signals are transmitted over transmission lines, such as telephone wires, they undergo change in phase. These phase changes can be compensated by all-pass filters.

- Thus, they are also called as delay equalizers or phase correctors

# HIGH PASS FILTER DESIGN:

- The design steps of the second order filter are identical to those of the first order filter as given

- bellow:

- 1. Choose a value of high cutoff frequency fH.

- 2. To simplify the design calculations, set R2 = R3 = R and C2 = C3 = C. Then

- choose a value of c less than 1µf

- 3. Calculate the value of R using

- 4. Finally, because of the equal resistor (R2 = R3) and capacitor (C2 = C3) values,

- the pass band voltage gain AF has to be equal to 1.586. This gain is necessary to guarantee

- Butterworth response. Therefore, RF = 0.586 R1. Hence choose a value of R1= 100 k $\Omega$  and

- calculate the value of RF.

# THANK YOU

# UNIT-IV A/D and D/A Converters

# Prepared by S.JAYACHITRA,AP/ECE

Karpagam Academy of Higher Education

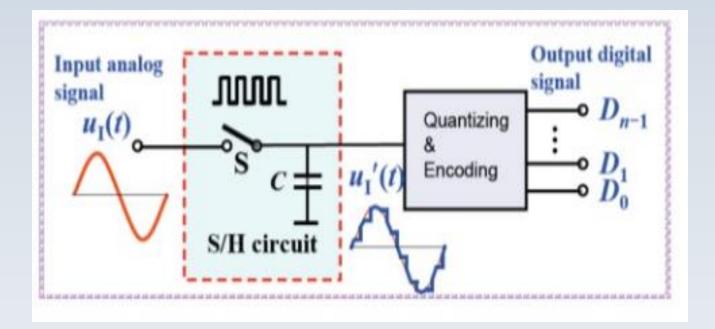

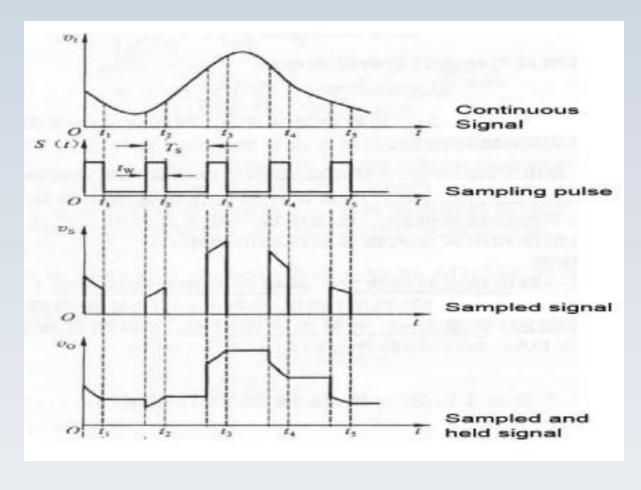

# Sample and Hold Circuit

- Reduction of a continuous signal to a discrete signal

- Achieved through sampling and holding circuit

- Switch ON sampling of signal (time to charge capacitor w/ Vin)

- Switch OFF voltage stored in capacitor (hold operation)

- Must hold sampled value constant for digital conversion demv of Hiaher Education

# Block Diagram of Sample and Hold Circuit

# **Sampling and Holding**

• The behavior of S/H is analogous to that of camera. its main function is "to capture picture" of the analog signal and hold its value until the adc can process the information.

Holding signal benefits the accuracy of the A/D Conversion

Minimum sampling rate should be at least twice the highest data frequency of the analog signal.

#### Waveforms of Sample and Hold Circuit

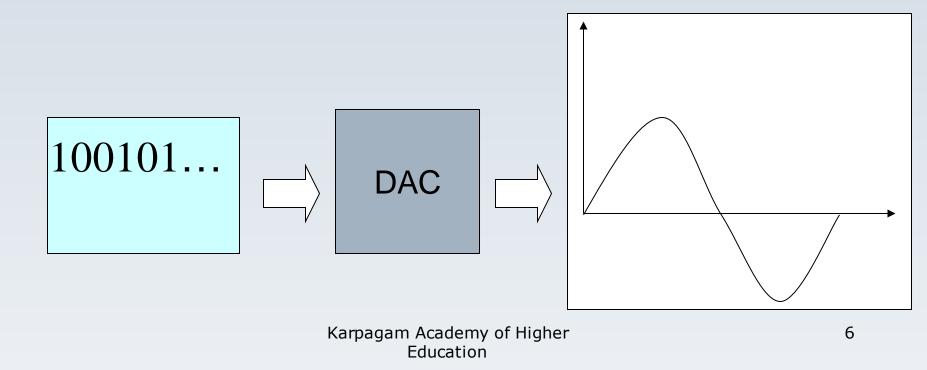

#### What is a DAC?

A digital to analog converter (DAC) converts a digital signal to an analog voltage or current output.

#### What is a DAC?

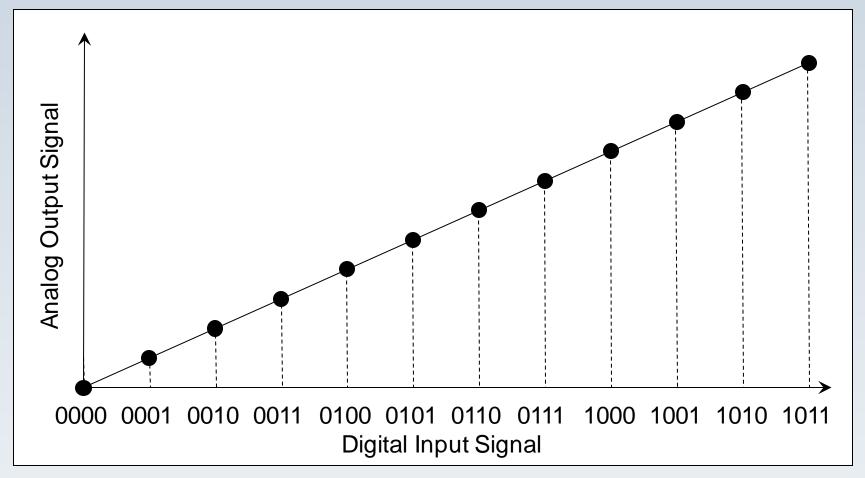

# **Types of DACs**

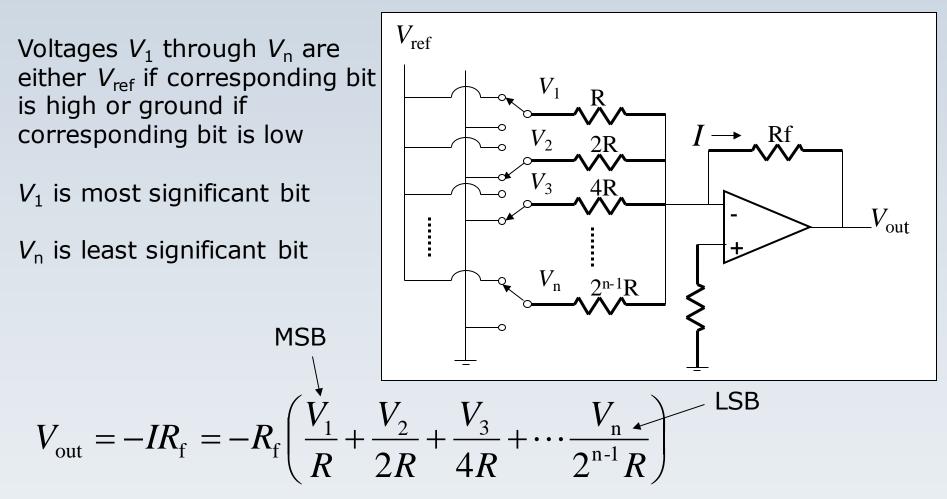

- Many types of DACs available.

- Usually switches, resistors, and opamps used to implement conversion

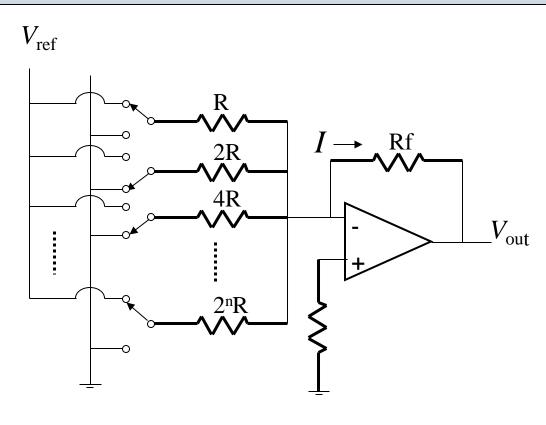

#### Two Types:

- Binary Weighted Resistor/Resistive Divider

- R-2R Ladder

- Utilizes a summing op-amp circuit

- Weighted resistors are used to distinguish each bit from the most significant to the least significant

- Transistors are used to switch between V<sub>ref</sub> and ground (bit high or low)

- Assume Ideal Op-amp

- No current into op-amp

- Virtual ground at inverting input

$$\Box V_{\rm out} = -IR_{\rm f}$$

Karpagam Academy of Higher Education

If

$$R_{\rm f} = R/2$$

$V_{\rm out} = -IR_{\rm f} = -\left(\frac{V_1}{2} + \frac{V_2}{4} + \frac{V_3}{8} + \dots + \frac{V_n}{2^n}\right)$

For example, a 4-Bit converter yields

$$V_{\text{out}} = -V_{\text{ref}} \left( b_3 \frac{1}{2} + b_2 \frac{1}{4} + b_1 \frac{1}{8} + b_0 \frac{1}{16} \right)$$

Where  $b_3$  corresponds to Bit-3,  $b_2$  to Bit-2, etc.

Karpagam Academy of Higher Education

- Advantages

- Simple Construction/Analysis

- Fast Conversion

- Disadvantages

- Requires large range of resistors (2000:1 for 12-bit DAC) with necessary high precision for low resistors

- Requires low switch resistances in transistors

- Can be expensive. Therefore, usually limited to 8-bit resolution.

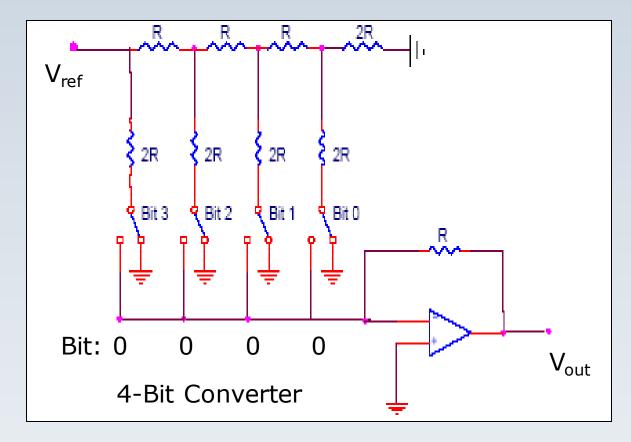

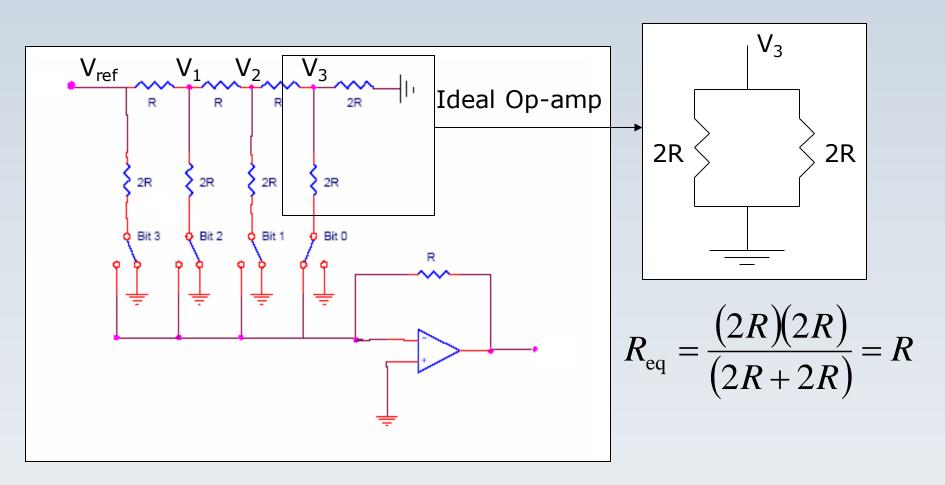

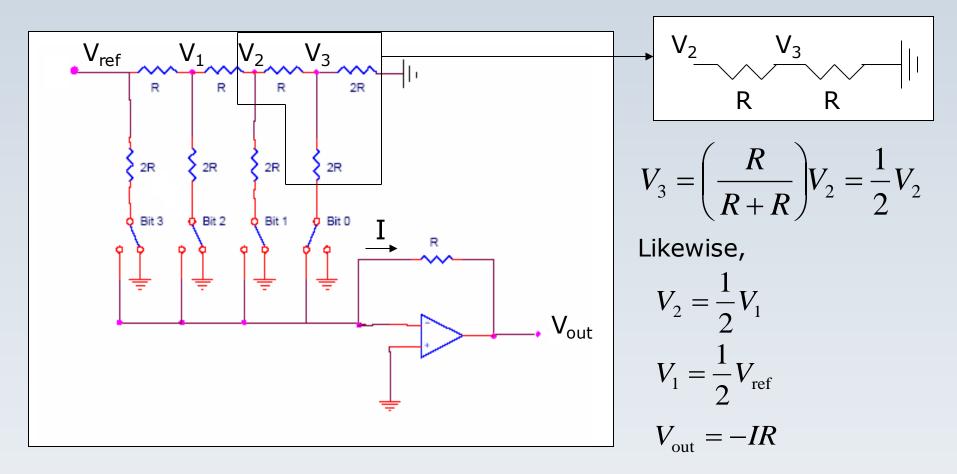

Each bit corresponds to a switch:

If the bit is high, the corresponding switch is connected to the inverting input of the op-amp.

If the bit is low, the corresponding switch is connected to ground.

For a 4-Bit R-2R Ladder

$$V_{\text{out}} = -V_{\text{ref}} \left( b_3 \frac{1}{2} + b_2 \frac{1}{4} + b_1 \frac{1}{8} + b_0 \frac{1}{16} \right)$$

For general n-Bit R-2R Ladder or Binary Weighted Resister DAC

$$V_{\text{out}} = -V_{\text{ref}} \sum_{i=1}^{n} b_{n-i} \frac{1}{2^{i}}$$

#### Advantages

- Only two resistor values (R and 2R)

- Does not require high precision resistors

#### Disadvantage

Lower conversion speed than binary weighted DAC

# Specifications of DACs

- Resolution

- Speed

- Linearity

- Settling Time

- Reference Voltages

- Errors

#### Resolution

Smallest analog increment corresponding to 1 LSB change

- An N-bit resolution can resolve 2<sup>N</sup> distinct analog levels

- Common DAC has a 8-16 bit resolution

Resolution =

$$V_{LSB} = \frac{V_{ref}}{2^N}$$

where N = number of bits

Karpagam Academy of Higher Education

## Speed

- Rate of conversion of a single digital input to its analog equivalent

- Conversion rate depends on

- clock speed of input signal

- settling time of converter

- □ When the input changes rapidly, the DAC conversion speed must be high.

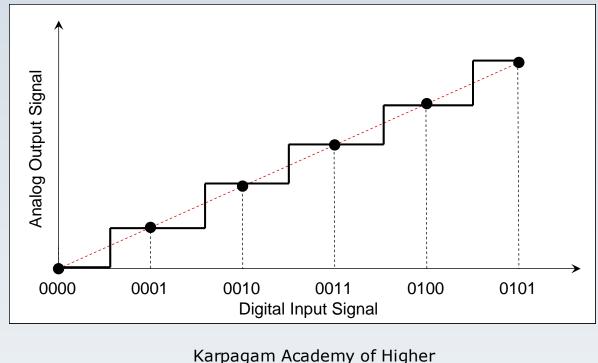

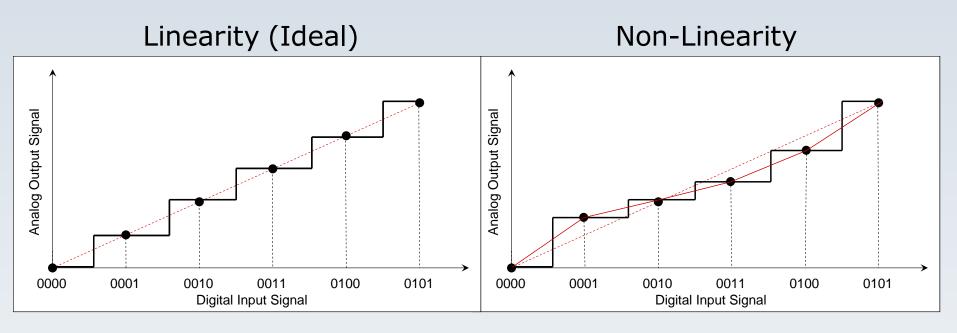

## Linearity

The difference between the desired analog output and the actual output over the full range of expected values

Education

## Linearity

Ideally, a DAC should produce a linear relationship between the digital input and analog output

Karpagam Academy of Higher Education

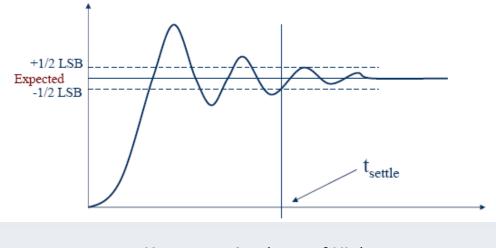

# Settling Time

- Time required for the output signal to settle within +/- ½ LSB of its final value after a given change in input scale

- □ Limited by slew rate of output amplifier

- Ideally, an instantaneous change in analog voltage would occur when a new binary word enters into DAC

# Reference Voltages

- Used to determine how each digital input will be assigned to each voltage division

- □ Types:

- Non-multiplier DAC: Vref is fixed

- Multiplier DAC: Vref provided by external source

# Types of Errors Associated with DACs

- 🛛 Gain

- Offset

- Full Scale

- Resolution

- Non-Linearity

- Non-Monotonic

- Settling Time and Overshoot

# Applications

- Digital Motor Control

- Computer Printers

- Sound Equipment (e.g. CD/MP3 Players, etc.)

- Electronic Cruise Control

- Digital Thermostat

# **Types of A/D Converters**

- Ramp or stair case or counter type A/D converter

- Successive Approximation A/D Converter

- Flash A/D Converter/Parallel Comparator

- Dual Slope or integrating type A/D Converter

# **Counter type**

The basic idea is to connect the output of a free-running binary counter to the input of a DAC, then compare the analog output of the DAC with the analog input signal to be digitized and use the comparator's output to tell the counter when to stop counting and reset.

# Features of counter type

- Use a clock to index the counter

- Use DAC to generate analog signal to compare against input

- Comparator is used to compare VIN and VDAC where VIN is the signal to be digitized

- The input to the DAC is from the counter

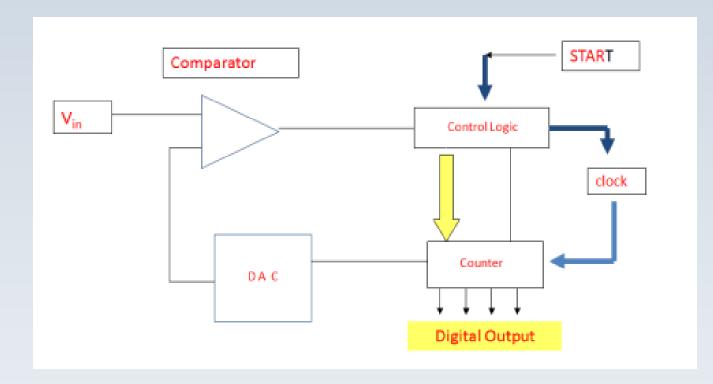

# **Block Diagram of Counter Type ADC**

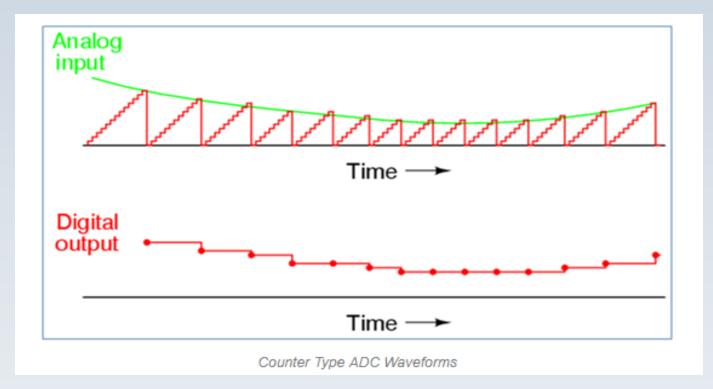

#### Counter Type ADC Waveforms

# Operation

- The analog output equivalent to the digital i/p from DAC is contrasted with the i/p analog voltage with the help of an op-amp comparator.

- This Integrated Circuit evaluates the two voltages and if the produced DAC voltage is low, it gives a high pulse to the N-bit counter as a CLK pulse to raise the counter.

- The similar procedure will be continued until the output of the DAC equals to the i/p analog voltage then it produces a low CLK pulse and also gives a clear signal to the counter as well as a load signal to the storage resistor.

- Here storage resistor is used to store the corresponding digital bits. These digital values are strongly matched with the analog input values with a small error.

- For each sampling interval, the output of DAC tracks a ramp way so that it is named as a Digital ramp kind ADC. And this ramp seems like staircases for each sampling moment, so that it is also named as a staircase approximation kind ADC.

- The conversion time on the counter type is NOT fixed but depends on the actual value of the analogue input expressed as a fraction of the full scale. This can be expressed as-

Conversion time =  $\frac{Vin}{Vrof} 2^{N} T$

Where N is the number of bits and T is the time period of the clock puise y of Higher 35

#### **Counter type ADC Advantages**

- Counter type ADC is very simple to understand and also to operate.

- Counter type ADC design is less complex, so the cost is also less

#### **Counter type ADC Disadvantages**

- Speed is less, since each time the counter has to begin from ZERO.

- There may be conflicts if the next i/p is sampled before completion of one process.

Karpagam Academy of Higher Education

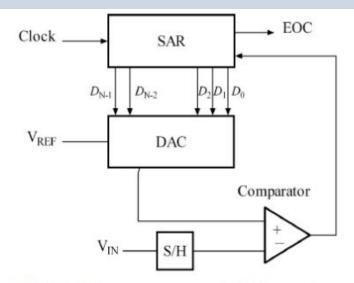

# Successive Approximation Type ADC

Uses a n-bit DAC to compare DAC and original analog results.

Uses Successive Approximation Register (SAR) supplies an approximate digital code to DAC of Vin.

•Comparison changes digital output to bring it closer to the input value.

Uses Closed-Loop Feedback Conversion

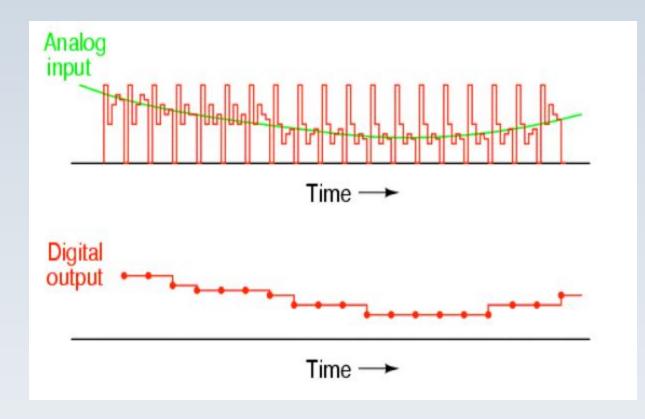

#### Waveforms

#### One method of addressing the digital ramp ADC's shortcomings is the so-called successive approximation ADC.

- The only change in this design is a very special counter circuit known as a successive-approximation register.

- Instead of counting up in binary sequence, this register counts by trying all values of bits starting with the most-significant bit and finishing at the least-significant bit.

- Throughout the count process, the register monitors the comparator's output to see if the binary count is less than or greater than the analog signal input, adjusting the bit values accordingly.

- The way the register counts is identical to the "trial-andfit" method of decimal-to-binary conversion, whereby different values of bits are tried from MSB to LSB to get a binary number that equals the original decimal Number. Karpagam Academy of Higher 39 Education 39

#### Process

- MSB initialized as 1

- Convert digital value to analog using DAC

- Compares guess to analog input

- Is Vin>VDAC

- Set bit 1

- If no, bit is 0 and test next bit format.

## Advantage

- Capable of high speed and reliable

- Medium accuracy compared to other ADC

- Good tradeoff between speed and cost

- Capable of outputting the binary number in serial (one bit at a time)

### Disadvantages

- Higher resolution

- slower

- Speed limited to ~5Msps

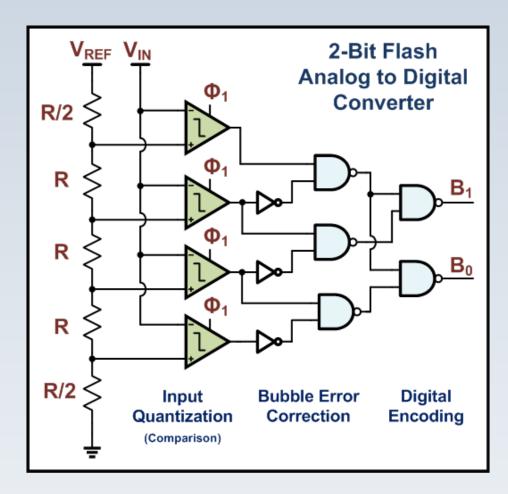

#### Flash Type ADC /Parallel Comparator

- Flash Type ADC is based on the principle of comparing analog input voltage with a set of reference voltages.

- To convert the analog input voltage into a digital signal of n-bit output, (2<sup>n</sup> – 1) comparators are required.

- The three op-amps are used as comparators. The non-inverting inputs of all the three comparators are connected to the analog input voltage.

- The inverting terminals are connected to a set of reference voltages

- The output of the comparator is in positive saturation(i.e. logic 1), when voltage at non-inverting terminal is greater than voltage at inverting terminal and is in negative saturation otherwise

#### comparator outputs for different ranges of analog input voltages and their corresponding digital outputs.

| Analog Input                                                                                           | <b>Comparator Outputs</b> |                | Digital output |       |    |

|--------------------------------------------------------------------------------------------------------|---------------------------|----------------|----------------|-------|----|

| Conditions                                                                                             | C1                        | C <sub>2</sub> | C <sub>3</sub> | $B_1$ | B₀ |

| $0 \hspace{0.1in} \leqslant \hspace{0.1in} V_{in} \hspace{0.1in} \leqslant \hspace{0.1in} \frac{V}{4}$ | 0                         | 0              | 0              | 0     | 0  |

| $\frac{V}{4} ~\leqslant~ V_{in} ~\leqslant~ \frac{2V}{4}$                                              | 1                         | 0              | 0              | 0     | 1  |

| $\frac{2V}{4} ~\leqslant~ V_{in} ~\leqslant~ \frac{3V}{4}$                                             | 1                         | 1              | 0              | 1     | 0  |

| $\frac{3V}{4} \leqslant V_{in} \leqslant V$                                                            | 1                         | 1              | 1              | 1     | 1  |

## **Advantages:**

- It is the fastest type of ADC because the conversion is performed simultaneously through a set of comparators, hence referred as flash type ADC. Typical conversion time is 100ns or less.

- The construction is simple and easier to design.

### Disadvantages

- It is not suitable for higher number of bits.

- To convert the analog input voltage into a digital signal of n-bit output, (2<sup>n</sup> - 1) comparators are required. The number of comparators required doubles for each added bit.

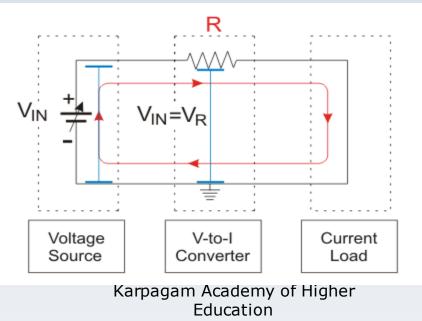

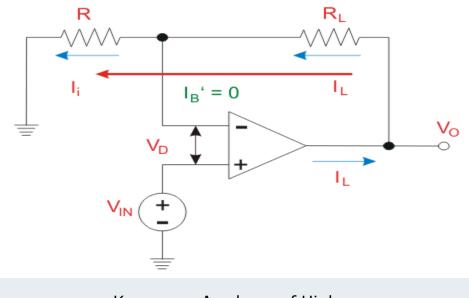

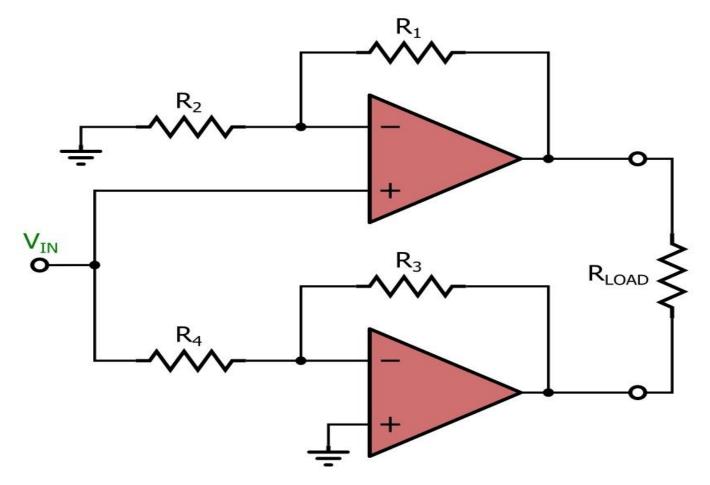

#### **Voltage to current Converter**

The resistor decides the current flow in a voltage source circuit or it performs as a simple voltage to current converter for a linear circuit.

- Op-amp is implemented to simply convert the voltage signal to corresponding current signal. The Opamp used for this purpose is IC LM741.

- This Op-amp is designed to hold the precise amount of current by applying the voltage which is essential to sustain that current through out the circuit. 50

# Current Converter

- The load resistor is floating in this converter circuit. That is, the resistor R<sub>L</sub> is not linked to ground.

- The voltage, V<sub>IN</sub> which is the input voltage is given to the non-inverting input terminal.

- The inverting input terminal is driven by the feedback voltage which is across the R<sub>L</sub> resistor.

This feedback voltage is determined by the load current and it is in series with the V<sub>D</sub>, which is the input difference voltage. So this circuit is also known as current series negative feedback amplifier.

For the input loop, the voltage equation is

$$V_{IN} = V_D + V_F$$

Since A is very large,  $V_D = 0$

So,

$$V_{IN} = V_F$$

Since, the input to the Op-amp,  $I_B^\prime=0$

$$V_{IN} = I_L imes R$$

$\therefore I_I = I_L = rac{V_{IN}}{R}$

- It is clear that the load current depends on the input voltage and the input resistance. That is, the load current, , which is the input voltage.

- The load current is controlled by the resistor, R. Here, the proportionality constant is 1/R.

- So, this converter circuit is also known as Trans-Conductance Amplifier. Other name of this circuit is Voltage Controlled Current Source. The type of load may be resistive, capacitive or nor determined for the set of t

## **Application of V-I Converter**

- Zener diode tester

- Low AC and DC Voltmeters

- Testing LED

- Testing Diodes

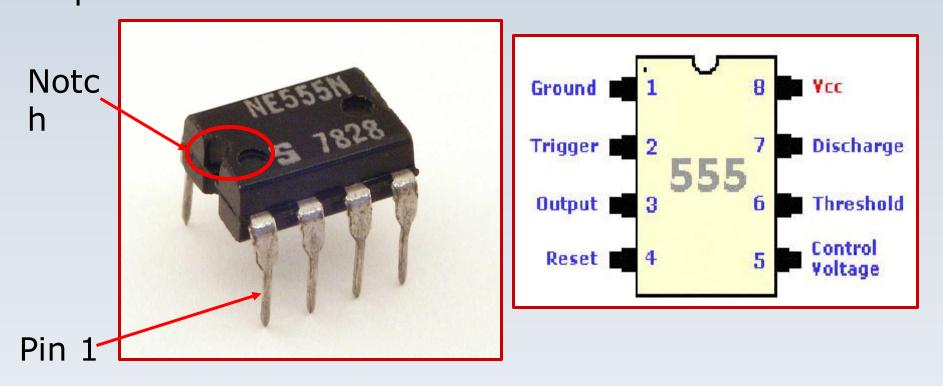

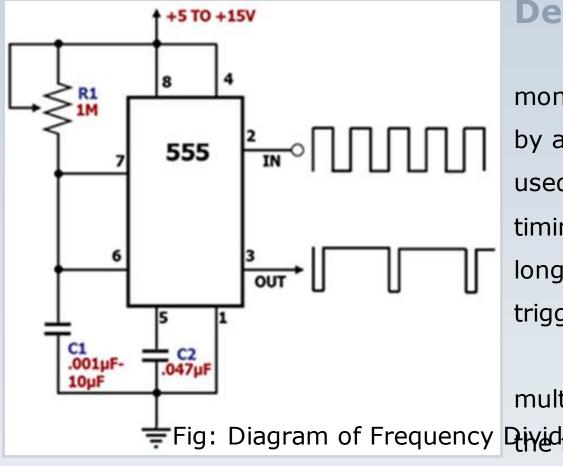

#### **555 Timer Introduction:**

- Signetics" Corporation first introduced this device as the SE/NE 555 in early 1970.

- It is a combination of digital and analog circuits.

- It is known as the "time machine" as it performs a wide variety of timing tasks.

- Applications for the 555 Timer include:

- Ramp and Square wave generator

- Frequency dividers

- Voltage-controlled oscillators

- Pulse generators and LED flashers

### 555 timer- Pin Diagram

#### The 555 timer is an 8-Pin D.I.L. Integrated Circuit or 'chip'

### **555 timer- Pin Description**

| Pi<br>n | Nam<br>e  | Purpose                                                                                                                                                                               |

|---------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | GND       | Ground, low level (0 V)                                                                                                                                                               |

| 2       | TRIG      | OUT rises, and interval starts, when this input falls below $1/3 V_{CC}$ .                                                                                                            |

| 3       | OUT       | This output is driven to approximately 1.7V below $\pm V_{CC}$ or GND.                                                                                                                |

| 4       | RESE<br>T | A timing interval may be reset by driving this input to GND, but the timing does not begin again until RESET rises above approximately 0.7 volts. Overrides TRIG which overrides THR. |

| 5       | CTRL      | "Control" access to the internal voltage divider (by default, $2/3 V_{CC}$ ).                                                                                                         |

| 6       | THR       | The interval ends when the voltage at THR is greater than at CTRL.                                                                                                                    |

| 7       | DIS       | Open collector output; may discharge a capacitor                                                                                                                                      |

#### **Description:**

- •Contains 25 transistors, 2 diodes and 16 resistors

- Maximum operating voltage 16V

- Maximum output current 200mA

- Best treated as a single component with required

input and output

If you input certain signals they will be processed / controlled in a certain manner and will produce a known output.

60

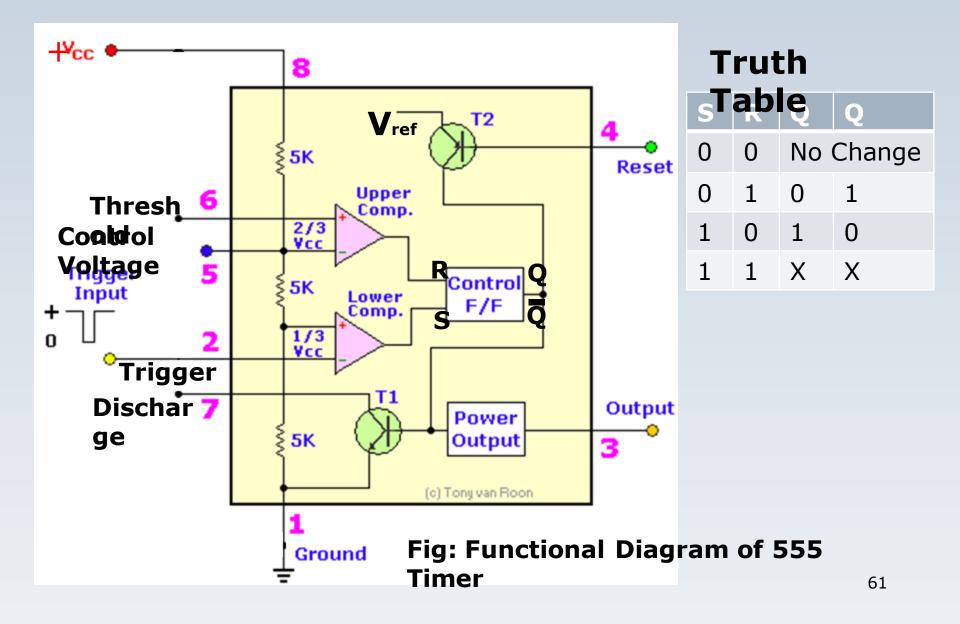

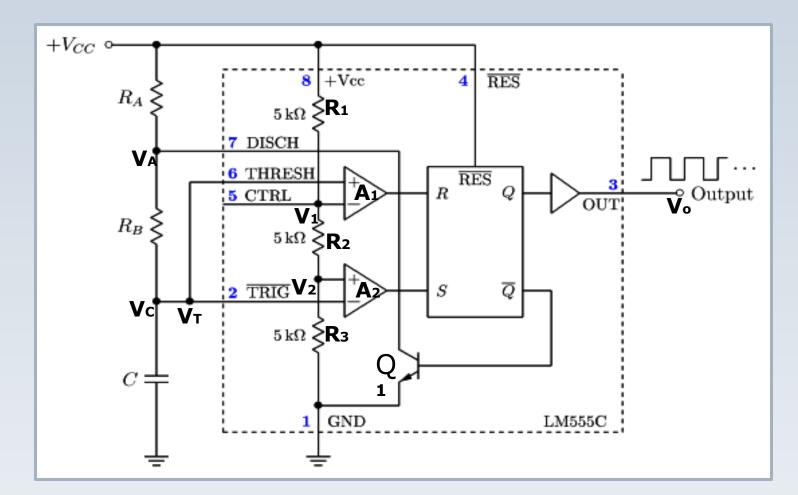

#### **Inside the 555 Timer**

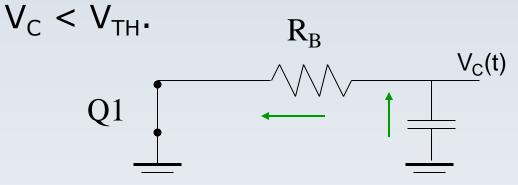

#### **OPERATION**

- The voltage divider has three equal 5K resistors. It divides the input voltage (V<sub>cc</sub>) into three equal parts.

- The two comparators are op-amps that compare the voltages at their inputs and saturate depending upon which is greater.

- The Threshold Comparator saturates when the voltage at the Threshold pin (pin 6) is greater than (2/3)V<sub>cc</sub>.

- The Trigger Comparator saturates when the voltage at the Trigger pin (pin 2)<sup>62</sup>is

#### Features of IC 555 Timer

The Features of IC 555 Timer are:

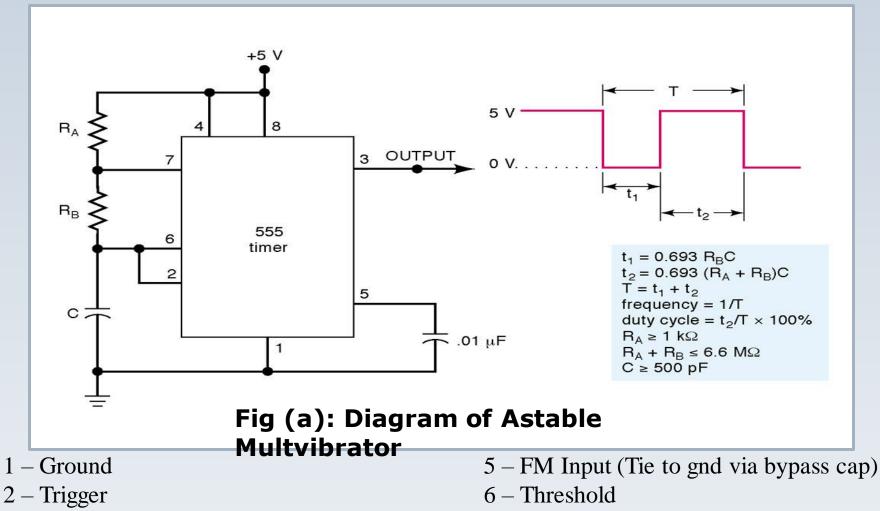

1. The 555 is a monolithic timer device which can be used to produce accurate and highly stable time delays or oscillation. It can be used to produce time delays ranging from few microseconds to several hours.

2. It has two basic operating modes: monostable and astable.

3. It is available in three packages: 8-pin metal can, 8-pin mini DIP or a 14-pin. A 14-pin package is IC 556 which consists of two 555 times.

#### Features of IC 555 Timer

4. The NE 555( signetics ) can operate with a supply voltage in the range of 4.5v to 18v and output currents of 200mA.