### KARPAGAM ACADEMY OF HIGHER EDUCATION (Deemed to be University Established Under Section 3 of UGC Act 1956) Pollachi Main Road, Eachanari Post, Coimbatore – 641 021 FACULTY OF ENGINEERING DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

### **LECTURE PLAN**

| NAME OF THE STAFF | : Dr.K.G.Dharani      |

|-------------------|-----------------------|

| DESIGNATION       | : ASSOCIATE PROFESSOR |

CLASS : B.E-IV YEAR ECE

SUBJECT : ASIC DESIGN

SUBJECT CODE : 16BEEC8E04

| S.No            | TOPICS TO BE COVERED  | TIME       | SUPPORTING           | TEACHING |

|-----------------|-----------------------|------------|----------------------|----------|

|                 |                       | DURATION   | MATERIALS            | AIDS     |

|                 | UNIT-I I              | NTRODUCTIO | N TO ASICs           |          |

|                 | 1                     | Γ          | 1                    |          |

| 1               | Introduction to ASICs | 2          | T1,Pg :No-1 to 4     | PPT , BB |

| 2               | Full-custom           | 1          | T1,Pg :No-5 to 10    | PPT , BB |

|                 |                       |            |                      |          |

| 3               | Semi-custom           | 1          | T1,Pg :No-10 to 16   | PPT , BB |

| 4               | ASIC Design           | 1          | T1,Pg :No-16 to 35   | PPT , BB |

| 5               | CMOS logic            | 2          | T1,Pg :No-39 to 60   | PPT , BB |

| 6               | ASIC library design   | 2          | T1,Pg :No-117 to 130 | PPT , BB |

| Introduction 02 |                       |            |                      |          |

| Total           | Lecture Hours         | 09         |                      |          |

| Total           | Hours                 | 09         |                      |          |

|          | UNIT-II PROGRAMMABLE ASICs               |    |                                       |                      |  |

|----------|------------------------------------------|----|---------------------------------------|----------------------|--|

| 7        | Programmable ASICs                       | 1  | T1,Pg :No-169 to 170                  | PPT , BB             |  |

| 8        | Anti fuse                                | 1  | T1,Pg :No-170 to 172                  | PPT , BB             |  |

| 9        | Static RAM                               | 1  | T1,Pg :No-174                         | PPT,BB               |  |

| 10       | EPROM and Technology                     | 1  | T1,Pg :No-174                         | PPT , BB             |  |

| 11<br>12 | Actel ACT–Xilinx LCA<br>Altera flex      | 1  | T1,Pg :No-191 to 193<br>T1,Pg :No-209 | PPT , BB<br>PPT , BB |  |

| 13       | Altera MAX Logic cells                   | 1  | T1,Pg :No-209                         | PPT, BB              |  |

| 14       | I/O cells–Interconnects                  | 1  | T1,Pg :No-232 to 240                  | PPT , BB             |  |

| 15       | Low level design entry. Schematic entry. | 1  | T1,Pg :No-327                         | PPT , BB             |  |

| Total    | Lecture Hours 09                         |    |                                       |                      |  |

| Total    | Hours                                    | 09 |                                       |                      |  |

|       | UNIT-III SIMULATION AND SYNTHESIS |    |                      |         |

|-------|-----------------------------------|----|----------------------|---------|

| 16    | Logic synthesis: A comparator     | 01 | T1,Pg :No-561        | BB, PPT |

|       | MUX                               |    |                      |         |

| 17    | Inside a logic synthesizer        | 01 | T1,Pg :No-569        | BB, PPT |

| 18    | VHDL                              | 01 | T1,Pg :No-593        | BB, PPT |

| 19    | Logic synthesis                   | 01 | T1,Pg :No-594 to 600 | PPT ,BB |

| 20    | FSM                               | 01 | T1,Pg :No-605        | PPT ,BB |

|       | synthesis                         |    |                      |         |

| 21    | Memory synthesis                  | 01 | T1,Pg :No-611,612    | PPT ,BB |

| 22    | Simulation                        | 01 | T1,Pg :No-641        | BB, PPT |

|       |                                   |    |                      |         |

| 23    | Types of simulation               | 01 | T1,Pg :No-641 to 647 | BB, PPT |

| 24    | Logic systems                     | 01 | T1,Pg :No-656        | BB, PPT |

| Total | Lecture Hours                     |    | 09                   |         |

| Total | Total Hours 09                    |    |                      |         |

|       | UNIT-IV                                     | ASIC | TESTING              |         |

|-------|---------------------------------------------|------|----------------------|---------|

| 25    | Boundary scantest                           | 01   | T1,Pg :No-714 to 724 | BB, PPT |

| 26    | Faults–Fault simulation                     | 01   | T1,Pg :No-736 to 741 | BB, PPT |

| 27    | Automatic test pattern generation algorithm | 02   | T1,Pg :No-755 to 756 | BB, PPT |

| 28    | D- algorithm                                | 02   | T1,Pg :No-755        | BB, PPT |

| 29    | PODEM                                       | 01   | T1,Pg :No-759        | BB, PPT |

| 30    | Built in self-test                          | 02   | T1,Pg :No-766        | BB, PPT |

| Total | Lecture Hours                               | 09   |                      |         |

| Total | Hours                                       | 09   |                      |         |

|       | UNIT-V ASIC CONSTRUCTION                                   |    |                              |         |  |

|-------|------------------------------------------------------------|----|------------------------------|---------|--|

| 37    | System partitioning                                        | 01 | T1,Pg :No-809                | BB, PPT |  |

| 38    | power dissipation                                          | 02 | T1,Pg :No-816                | BB, PPT |  |

| 39    | partitioning methods                                       | 02 | T1,Pg :No-824                | BB, PPT |  |

| 40    | floor planning and placement                               | 02 | T1,Pg :No-853 to 856,<br>873 | BB, PPT |  |

| 41    | Routing: Global routing, detailed routing, special routing | 01 | T1,Pg :No- 910,922,935       | BB, PPT |  |

| 42    | Introduction to SOC                                        | 01 | T1,Pg :No-939                | BB, PPT |  |

| Total | Lecture Hours                                              |    | 09                           |         |  |

| Total | Fotal Hours 09                                             |    |                              |         |  |

Total No of Hours for Introduction: 02Hrs

Total No of Lecture Hours Planned: 45 Hrs

Total No of Hours Planned : 45 Hours

### **TEXT BOOKS:**

| S.NO. | Author(s) Name | Title of the book                             | Publisher         | Year of the publication |

|-------|----------------|-----------------------------------------------|-------------------|-------------------------|

| 1     | M.J.S.SMITH    | "Application Specific<br>Integrated Circuits" | Pearson Education | 2006                    |

| 2.    | Wolf Wayne     | FPGA based system design                      | Pearson Education | 2005                    |

### **REFERENCE BOOKS:**

| S.NO. | Author(s) Name                                                   | Title of the book                             | Publisher                    | Year of the publication |

|-------|------------------------------------------------------------------|-----------------------------------------------|------------------------------|-------------------------|

| 1.    | M. Sarafzadehand<br>C.K.Wong                                     | An Introduction to<br>VLSI Physical<br>Design | McGraw Hill                  | 1996                    |

| 2.    | JanM.Rabaey.<br>Anantha<br>Chandra kasan,<br>Borivoje<br>Nikolic | Digital Integrated<br>Circuits                | Prentice-Hall<br>Publication | 2002                    |

### STAFF IN-CHARGE

### HOD/ECE

### **ASIC** Design

### **Objectives:**

- To focus on the IC Design and the various design

- To understand the principles of design logic cells, I/O cells and interconnect architecture

- To explore the Application Specific Integrated Circuits (ASIC) design flow from the circuit and layout design point of view.

- To study about logic synthesis, placement and routing

### Outcomes:

After completing this course the student will be able to

- Gain knowledge on various types of ASIC design

- Gain knowledge in the circuit design aspects at various levels of abstractions.

- Understand various architecture and its purpose in different application

- Understand placement, routing concepts in optimized IC design

### Unit I Introduction To ASIC, CMOS Logic And ASIC Library Design

Types of ASICs - Design flow - CMOS transistors - Combinational Logic Cell – Sequential logic cell - Data path logic cell - Transistors as Resistors - Transistor Parasitic Capacitance- Logical effort.

### Unit II Programmable Asics, Programmable ASIC Logic Cells And Programmable ASIC I/O Cells

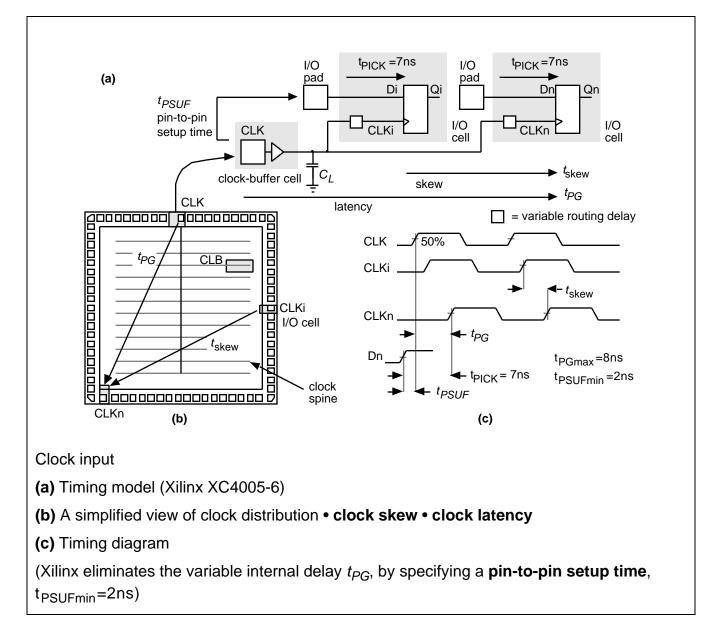

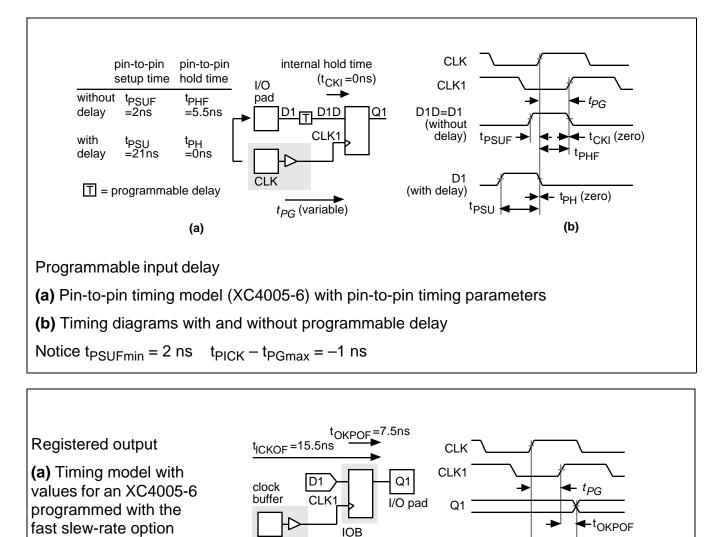

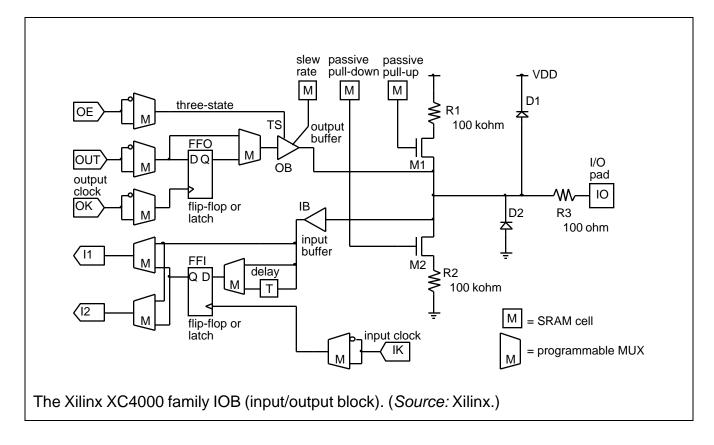

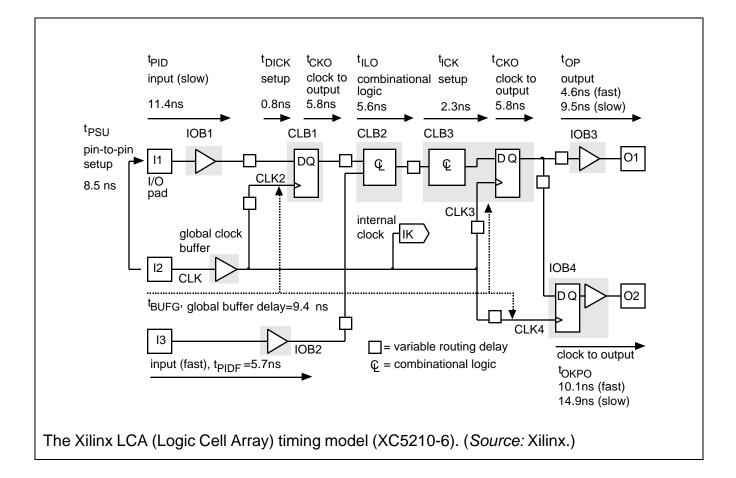

Anti fuse - static RAM - EPROM and EEPROM technology - Actel ACT - Xilinx LCA – Altera FLEX - Altera MAX DC & AC inputs and outputs - Clock & Power inputs - Xilinx I/O blocks.

### Unit III Programmable ASIC Architecture

Architecture and configuration of Spartan / Cyclone and Virtex / Stratix FPGAs – Micro-Blaze / Nios based embedded systems – Signal probing techniques.

### Unit IV Logic Synthesis, Placement And Routing

Logic synthesis - ASIC floor planning- placement and routing – power and clocking strategies.

### Unit V High Performance Algorithms for ASIC / SOCs

DAA and computation of FFT and DCT. High performance filters using delta-sigma modulators. Case Studies: Digital camera, SDRAM, High speed data standards.

Suggested Readings:

1. Douglas J. Smith, HDL Chip Design, Madison, AL, USA: Doone Publications, 1996.

2. M.J.S.Smith, " Application - Specific Integrated Circuits", Pearson, 2003

3. Mohammed Ismail and Terri Fiez, "Analog VLSI Signal and Information Processing ", McGraw Hill, 1994.

4. Roger Woods, John McAllister, Dr. Ying Yi, Gaye Lightbod, "FPGA-based Implementation of Signal Processing Systems", Wiley, 2008

5. Steve Kilts, "Advanced FPGA Design," Wiley Inter-Science.

Weblinks:

https://www.electronics-notes.com/articles/electronic\_components/programmable-logic/what-is-anasic-application-specific-integrated-circuit.php

https://www.tce.edu/sites/default/files/PDF/14EC770-ASIC-DESIGN-K.Kalyani.pdf

# ASIC LIBRARY DESIGN

3

*Key concepts:* Tau, logical effort, and the prediction of delay • Sizes of cells, and their drive strengths • Cell importance • The difference between gate-array macros, standard cells, and datapath cells

ASIC design uses predefined and precharacterized cells from a library—so we need to design or buy a cell library. A knowledge of ASIC library design is not necessary but makes it easier to use library cells effectively.

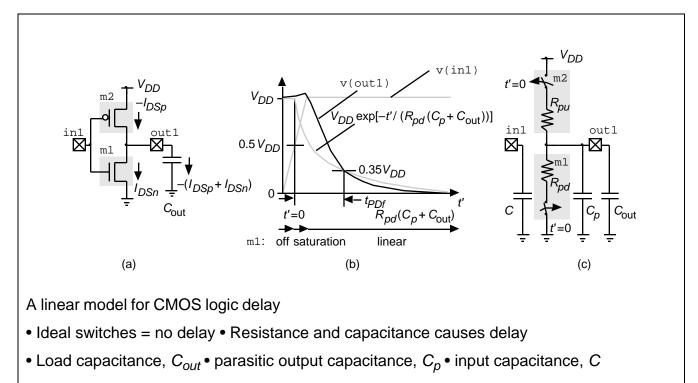

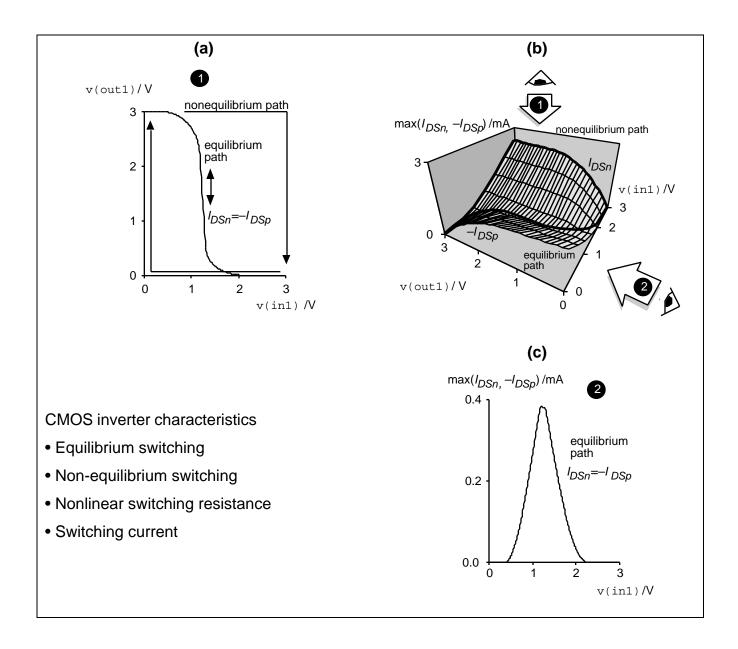

3.1 Transistors as Resistors

$-t_{PDf}$   $0.35 V_{DD} = V_{DD} \exp - \frac{-t_{PDf}}{R_{pd} (C_{out} + C_p)}$

An output trip point of 0.35 is convenient because  $\ln(1/0.35)=1.04$  1 and thus  $t_{PDf} = R_{pd}(C_{out} + C_p) \ln(1/0.35)$   $R_{pd}(C_{out} + C_p)$ For output trip points of 0.1/0.9 we multiply by  $-\ln(0.1) = 2.3$ , because exp (-2.3) = 0.100

- Linearize the switch resistance Pull-up resistance,  $R_{pu}$  pull-down resistance,  $R_{pd}$

- Measure and compare the input, v(in1) and output, v(out1)

- Input trip point of 0.5 output trip points are 0.35 (falling) and 0.65 (rising)

- The linear prop–ramp model: falling propagation delay,  $t_{PDf} R_{pd}(C_p + C_{out})$

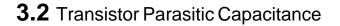

- $C_{BS}$  and  $C_{BD}$  are the sum of the area ( $C_{BSJ}$ ,  $C_{BDJ}$ ), sidewall ( $C_{BSSW}$ ,  $C_{BDSW}$ ), and channel edge ( $C_{BSJGATE}$ ,  $C_{BDJGATE}$ ) capacitances

- $L_D$  is the lateral diffusion  $T_{FOX}$  is the field-oxide thickness

| NAME  | ml       | m2        |

|-------|----------|-----------|

| MODEL | CMOSN    | CMOSP     |

| ID    | 7.49E-11 | -7.49E-11 |

| VGS   | 0.00E+00 | -3.00E+00 |

| VDS   | 3.00E+00 | -4.40E-08 |

| VBS   | 0.00E+00 | 0.00E+00  |

| VTH   | 4.14E-01 | -8.96E-01 |

| VDSAT | 3.51E-02 | -1.78E+00 |

| GM    | 1.75E-09 | 2.52E-11  |

| GDS   | 1.24E-10 | 1.72E-03  |

| GMB   | 6.02E-10 | 7.02E-12  |

| CBD   | 2.06E-15 | 1.71E-14  |

| CBS   | 4.45E-15 | 1.71E-14  |

| CGSOV | 1.80E-15 | 2.88E-15  |

| CGDOV | 1.80E-15 | 2.88E-15  |

| CGBOV | 2.00E-16 | 2.01E-16  |

| CGS   | 0.00E+00 | 1.10E-14  |

| CGD   | 0.00E+00 | 1.10E-14  |

| CGB   | 3.88E-15 | 0.00E+00  |

- ID ( $I_{DS}$ ), VGS, VDS, VBS, VTH ( $V_t$ ), and VDSAT ( $V_{DS(sat)}$ ) are DC parameters

- GM, GDS, and GMB are small-signal conductances (corresponding to  $I_{DS}/V_{GS}$ ,  $I_{DS}/V_{DS}$ , and  $I_{DS}/V_{BS}$ , respectively)

| PSpice             | Equation                                                                                                                                                                                                                                                                                                                                                                          | Values <sup>1</sup> for $V_{GS}$ =0V, $V_{DS}$ =3V, $V_{SB}$ =0V                                                       |  |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--|

| CBD                |                                                                                                                                                                                                                                                                                                                                                                                   | $C_{BD} = 1.855 \times 10^{-13} + 2.04 \times 10^{-16} = 2.06 \times$                                                  |  |

|                    | $C_{BD} = C_{BDJ} + C_{BDSW}$                                                                                                                                                                                                                                                                                                                                                     | 10 <sup>-13</sup> F                                                                                                    |  |

|                    | $C_{BDJ} + A_D C_J (1 + V_{DB}/B)^{-mJ} (B = PB)$                                                                                                                                                                                                                                                                                                                                 | $C_{BDJ}$ = (4.032 × 10 <sup>-15</sup> )(1 + (3/1)) <sup>-0.56</sup> = 1.86 × 10 <sup>-15</sup> F                      |  |

|                    | $C_{BDSW} = P_D C_{JSW} (1 + V_{DB}/B)^{-mJSW}$<br>( $P_D$ may or may not include channel edge)                                                                                                                                                                                                                                                                                   | $C_{BDSW}$ = (4.2 × 10 <sup>-16</sup> )(1 + (3/1)) <sup>-0.5</sup> = 2.04 × 10 <sup>-16</sup> F                        |  |

| CBS                | $C_{BS} = C_{BSJ} + C_{BSSW}$                                                                                                                                                                                                                                                                                                                                                     | $C_{BS} = 4.032 \times 10^{-15} + 4.2 \times 10^{-16} = 4.45 \times 10^{-15} \text{ F}$                                |  |

|                    | $C_{BSJ}$ + A <sub>S</sub> C <sub>J</sub> (1 + V <sub>SB</sub> /B) <sup>-mJ</sup>                                                                                                                                                                                                                                                                                                 | $A_{S} C_{J} = (7.2 \times 10^{-15})(5.6 \times 10^{-4}) = 4.03 \times 10^{-15} F$                                     |  |

|                    | $C_{BSSW} = P_S C_{JSW} (1 + V_{SB}/B)^{-mJSW}$                                                                                                                                                                                                                                                                                                                                   | $P_{S}C_{JSW} = (8.4 \times 10^{-6})(5 \times 10^{-11}) = 4.2 \times 10^{-16} \text{ F}$                               |  |

| CGSOV              | $C_{GSOV}=W_{EFF}C_{GSO}$ ; $W_{EFF}=W-2W$<br>D                                                                                                                                                                                                                                                                                                                                   | $C_{GSOV} = (6 \times 10^{-6})(3 \times 10^{-10}) = 1.8 \times 10^{-16} \text{ F}$                                     |  |

| CGDOV              | $C_{GDOV} = W_{EFF}C_{GSO}$                                                                                                                                                                                                                                                                                                                                                       | $C_{GDOV} = (6 \times 10^{-6})(3 \times 10^{-10}) = 1.8 \times 10^{-15} \text{ F}$                                     |  |

| CGBOV              | $C_{GBOV} = L_{EFF}C_{GBO}$ ; $L_{EFF} = L - 2L_{D}$                                                                                                                                                                                                                                                                                                                              | $C_{GDOV} = (0.5 \times 10^{-6})(4 \times 10^{-10}) = 2 \times 10^{-16} \text{ F}$                                     |  |

| CGS                | $C_{GS}/C_{O} = 0$ (off), 0.5 (lin.), 0.66 (sat.)<br>$C_{O}$ (oxide capacitance) = $W_{EF}L_{EFF}$ ox<br>/ $T_{ox}$                                                                                                                                                                                                                                                               | $C_{O} = (6 \times 10^{-6})(0.5 \times 10^{-6})(0.00345) = 1.03 \times 10^{-14} \text{ F}$<br>$C_{GS} = 0.0 \text{ F}$ |  |

| CGD                | C <sub>GD</sub> /C <sub>O</sub> = 0 (off), 0.5 (lin.), 0 (sat.)                                                                                                                                                                                                                                                                                                                   | $C_{\rm GD} = 0.0 \; {\rm F}$                                                                                          |  |

| CGB                | $C_{GB} = 0$ (on), = C <sub>O</sub> in series with $C_{GS}$ (off)                                                                                                                                                                                                                                                                                                                 | $C_{GB} = 3.88 \times 10^{-15}$ F, $C_{S}$ =depletion capacitance                                                      |  |

| <sup>1</sup> Input | .MODEL CMOSN NMOS LEVEL=3 PHI=0.7 TOX=10E-09 XJ=0.2U TPG=1<br>VTO=0.65 DELTA=0.7<br>+ LD=5E-08 KP=2E-04 UO=550 THETA=0.27 RSH=2 GAMMA=0.6<br>NSUB=1.4E+17 NFS=6E+11<br>+ VMAX=2E+05 ETA=3.7E-02 KAPPA=2.9E-02 CGDO=3.0E-10<br>CGSO=3.0E-10 CGBO=4.0E-10<br>+ CJ=5.6E-04 MJ=0.56 CJSW=5E-11 MJSW=0.52 PB=1<br>m1 outl in1 0 0 cmosn W=6U L=0.6U AS=7.2P AD=7.2P PS=8.4U<br>PD=8.4U |                                                                                                                        |  |

### 3.2.1 Junction Capacitance

• Junction capacitances,  $C_{BD}$  and  $C_{BS}$ , consist of two parts: junction area and sidewall

• Both  $C_{BD}$  and  $C_{BS}$  have different physical characteristics with parameters: CJ and MJ for the junction, CJSW and MJSW for the sidewall, and PB is common

•  $C_{BD}$  and  $C_{BS}$  depend on the voltage across the junction ( $V_{DB}$  and  $V_{SB}$ )

• The sidewalls facing the channel ( $C_{BSJGATE}$  and  $C_{BDJGATE}$ ) are different from the sidewalls that face the field

• It is a mistake to exclude the gate edge assuming it is in the rest of the model-it is not

• In HSPICE there is a separate mechanism to account for the channel edge capacitance (using parameters ACM and CJGATE)

### 3.2.2 Overlap Capacitance

- The overlap capacitance calculations for C<sub>GSOV</sub> and C<sub>GDOV</sub> account for lateral diffusion

- SPICE parameter LD=5E-08 or LD=0.05 µm

- Not all SPICE versions use the equivalent parameter for width reduction,  $\mathtt{WD},$  in calculating  $C_{GDOV}$

Not all SPICE versions subtract W<sub>D</sub> to form W<sub>EFF</sub>

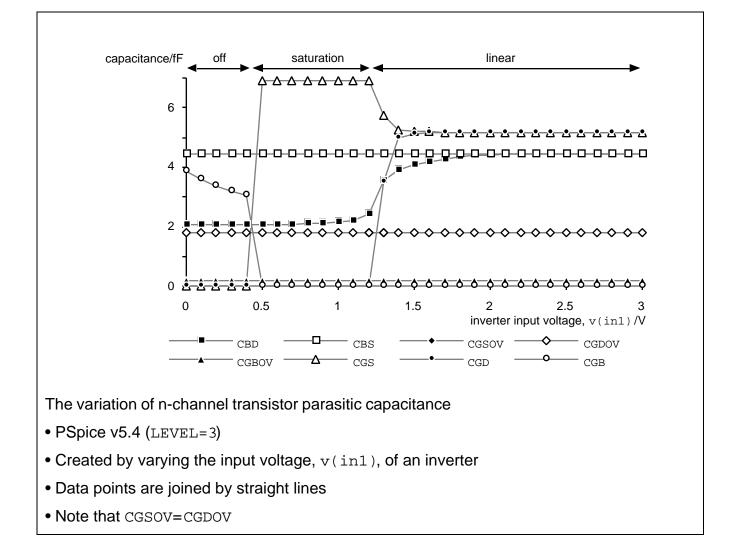

#### 3.2.3 Gate Capacitance

• The gate capacitance depends on the operating region

• The gate–source capacitance  $C_{GS}$  varies from zero (off) to  $0.5C_{O}$  in the linear region to (2/3) $C_{O}$  in the saturation region

• The gate–drain capacitance  $C_{GD}$  varies from zero (off) to 0.5C<sub>O</sub> (linear region) and back to zero (saturation region)

• The gate–bulk capacitance  $C_{GB}$  is two capacitors in series: the fixed gate-oxide capacitance,  $C_{O}$ , and the variable depletion capacitance,  $C_{S}$

• As the transistor turns on the channel shields the bulk from the gate—and  $C_{GB}$  falls to zero

• Even with  $V_{GS}$ =0V, the depletion width under the gate is finite and thus  $C_{GB}$  is less than  $C_O$

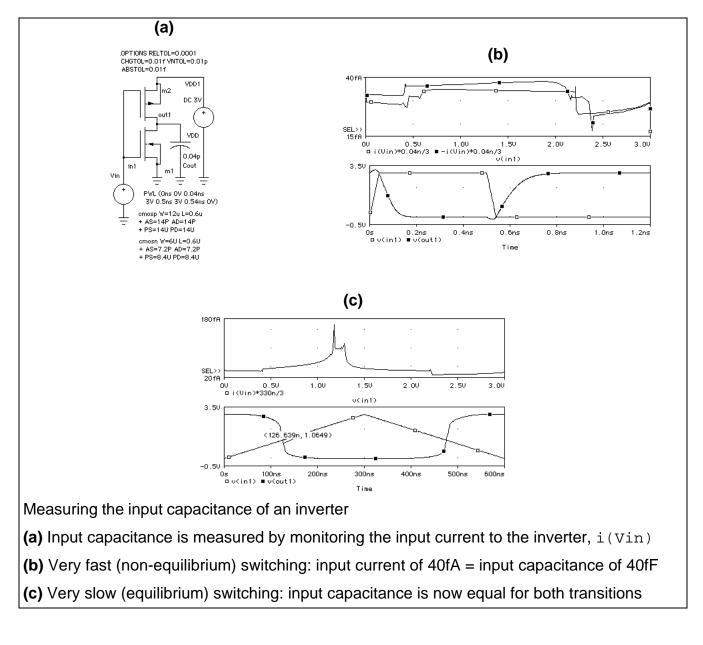

### 3.2.4 Input Slew Rate

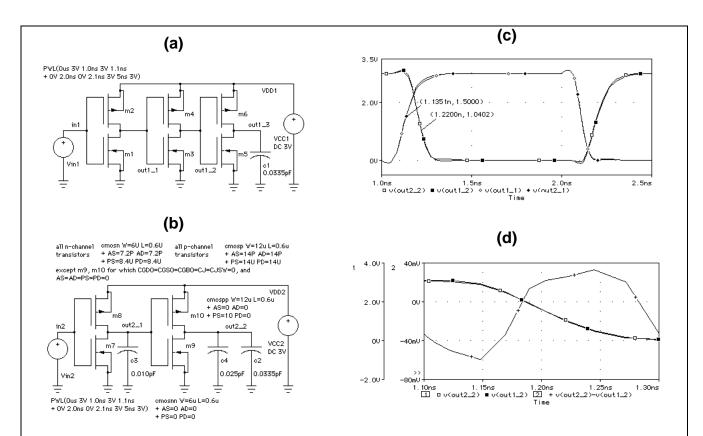

Parasitic capacitance measurement

(a) All devices in this circuit include parasitic capacitance

(b) This circuit uses linear capacitors to model the parasitic capacitance of m9/10.

• The load formed by the inverter (m5 and m6) is modeled by a 0.0335pF capacitor (c2)

• The parasitic capacitance due to the overlap of the gates of  $m_3$  and  $m_4$  with their source, drain, and bulk terminals is modeled by a 0.01pF capacitor (c3)

• The effect of the parasitic capacitance at the drain terminals of m3 and m4 is modeled by a 0.025pF capacitor (c4)

(c) Comparison of (a) and (b). The delay (1.22-1.135=0.085ns) is equal to  $t_{PDf}$  for the inverter m3/4

(d) An exact match would have both waveforms equal at the 0.35 trip point (1.05V).

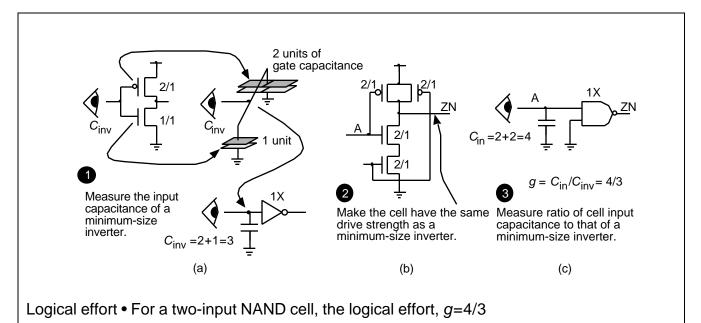

### **3.3** Logical Effort

We extend the prop-ramp model with a "catch all" term,  $t_{q}$ , that includes:

- delay due to internal parasitic capacitance

- the time for the input to reach the switching threshold of the cell

- the dependence of the delay on the slew rate of the input waveform

$t_{PD} = R(C_{out} + C_p) + t_q$ We can **scale** any logic cell by a scaling factor s:  $t_{PD} = (R/s) \cdot (C_{out} + sC_p) + st_q$

$$t_{PD} = RC - C_{out} + RC_p + st_q$$

$$C_{in}$$

The time constant **tau**,  $= R_{inv} C_{inv}$ , is a basic property of any CMOS technology

The delay equation is the sum of three terms, d = f + p + q or delay = effort delay + parasitic delay + nonideal delay

The effort delay f is the product of **logical effort**, g, and **electrical effort**, h: f = gh

Thus, delay = logical effort × electrical effort + parasitic delay + nonideal delay

- R and C will change as we scale a logic cell, but the RC product stays the same

- Logical effort is independent of the size of a logic cell

- We can find logical effort by scaling a logic cell to have the same drive as a 1X minimum-size inverter

- Then the logical effort, g, is the ratio of the input capacitance,  $C_{in}$ , of the 1X logic cell to  $C_{inv}$

(a) Find the input capacitance,  $C_{inv}$ , looking into the input of a minimum-size inverter in terms of the gate capacitance of a minimum-size device

(b) Size a logic cell to have the same drive strength as a minimum-size inverter (assuming a logic ratio of 2). The input capacitance looking into one of the logic-cell terminals is then  $C_{in}$

(c) The logical effort of a cell is  $C_{in}/C_{inv}$

The *h* depends only on the load capacitance  $C_{out}$  connected to the output of the logic cell and the input capacitance of the logic cell,  $C_{in}$ ; thus

### electrical effort $h = C_{out} / C_{in}$

**parasitic delay**  $p = RC_p$  (the parasitic delay of a minimum-size inverter is:  $p_{inv} = C_p / C_{inv}$ )

**nonideal delay**  $q = st_q / dt_q$

| Cell effort, parasitic delay, and nonideal delay (in units of $$ ) for single-stage CMOS cells                                    |                   |                                        |                           |                           |

|-----------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------------------|---------------------------|---------------------------|

| Cell         Cell effort<br>(logic ratio=2)         Cell effort<br>(logic ratio=r)         Parasitic delay/         Nonideal dela |                   |                                        |                           |                           |

| inverter                                                                                                                          | 1 (by definition) | 1 (by definition)                      | $p_{inv}$ (by definition) | $q_{inv}$ (by definition) |

| n-input NAND                                                                                                                      | ( <i>n</i> +2)/3  | ( <i>n</i> + <i>r</i> )/( <i>r</i> +1) | np <sub>inv</sub>         | nq <sub>inv</sub>         |

| n-input NOR                                                                                                                       | (2 <i>n</i> +1)/3 | ( <i>nr</i> +1)/( <i>r</i> +1)         | np <sub>inv</sub>         | nq <sub>inv</sub>         |

#### ASICS... THE COURSE

### 3.3.1 Predicting Delay

- Example: predict the delay of a three-input NOR logic cell

- 2X drive

- driving a net with a fanout of four

0.3pF total load capacitance (input capacitance of cells we are driving plus the interconnect)

- $p=3p_{inv}$  and  $q=3q_{inv}$  for this cell

- the input gate capacitance of a 1X drive, three-input NOR logic cell is equal to gCinv

- for a 2X logic cell,  $C_{in} = 2gC_{inv}$

$gh = g \quad \frac{C_{\text{out}}}{C_{\text{in}}} = \frac{g \cdot (0.3 \text{ pF})}{2gC_{\text{inv}}} = \frac{(0.3 \text{ pF})}{(2) \cdot (0.036 \text{ pF})}$  (Notice g cancels out in this equation)

The delay of the NOR logic cell, in units of , is thus

$$d = gh + p + q = \frac{0.3 \times 10^{-12}}{(2) \cdot (0.036 \times 10^{-12})} + (3) \cdot (1) + (3) \cdot (1.7)$$

= 4.1666667 + 3 + 5.1

= 12.266667 equivalent to an absolute delay,  $t_{PD}$  12.3×0.06ns=0.74ns

The delay for a 2X drive, three-input NOR logic cell is  $t_{PD} = (0.03 + 0.72C_{out} + 0.60)$  ns

With  $C_{out}$ =0.3pF,  $t_{PD}$ = 0.03 + (0.72)·(0.3) + 0.60 = 0.846 ns compared to our prediction of 0.74ns

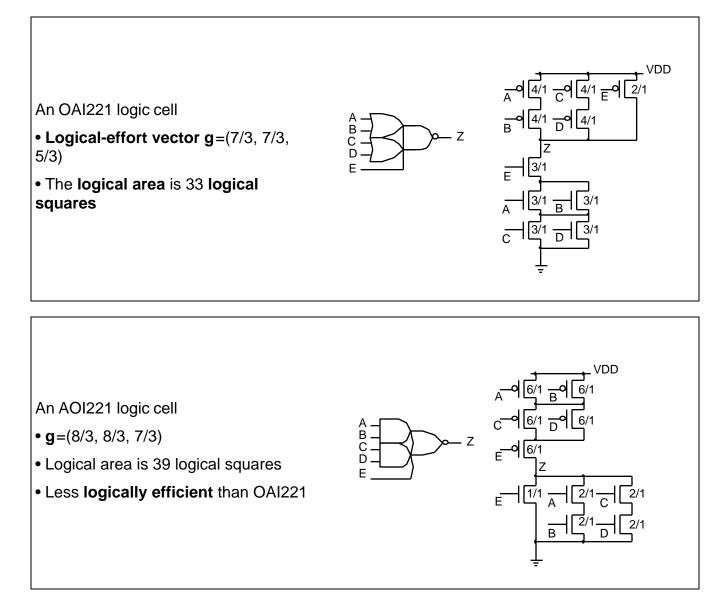

### 3.3.2 Logical Area and Logical Efficiency

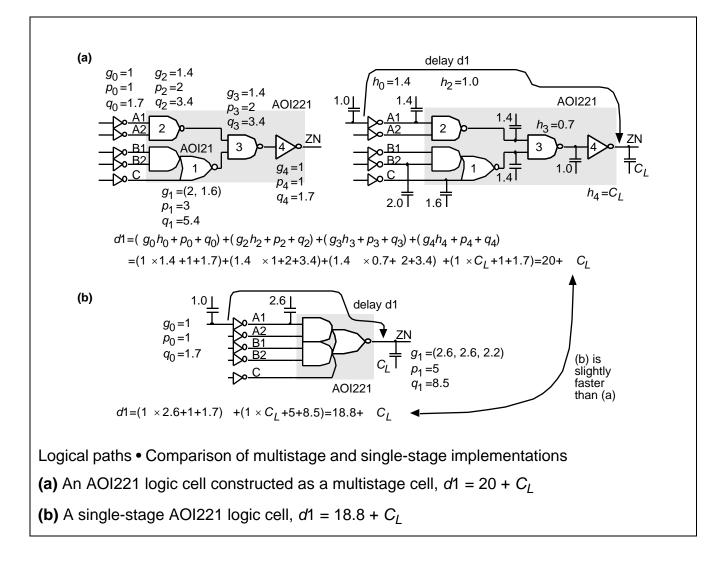

### 3.3.3 Logical Paths

path delay  $D = g_i h_i + (p_i + q_i)$ *i* path *i* path

#### 3.3.4 Multistage Cells

### 3.3.5 Optimum Delay

path logical effort G = gi i path C<sub>out</sub> h<sub>i</sub> path electrical effort H =Cin i path  $C_{out}$  is the load and  $C_{in}$  is the first input capacitance on the path path effort F = GH $f^{n}_{i} = g_{i}h_{i} \qquad = F^{1/N}$ optimum effort delay  $D^{\Lambda} = NF^{1/N} = N(GH)^{1/N} + P + Q$ optimum path delay P + Q = $p_i + h_i$

> i path

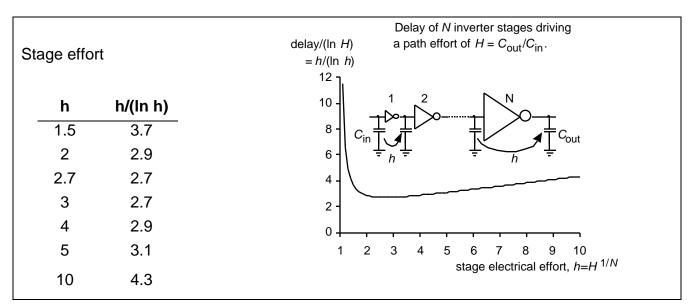

### 3.3.6 Optimum Number of Stages

• Chain of *N* inverters each with equal stage effort, *f=gh*

• Total path delay is Nf=Ngh=Nh, since g=1 for an inverter

- To drive a path electrical effort H,  $h^N = H$ , or  $N \ln h = \ln H$

- Delay, Nh = hln H/ln h

- Since In*H* is fixed, we can only vary *h*/In(*h*)

- $h/\ln(h)$  is a shallow function with a minimum at h=e 2.718

- Total delay is *N*e=eIn *H*

### 3.4 Library-Cell Design

- A big problem in library design is dealing with design rules

- Sometimes we can **waive** design rules

- **Symbolic layout**, **sticks** or **logs** can decrease the library design time (9 months for Virtual Silicon–currently the most sophisticated standard-cell library)

- Mapping symbolic layout uses 10–20 percent more area (5–10 percent with compaction)

- Allowing 45° layout decreases silicon area (some companies do not allow 45° layout)

### 3.5 Library Architecture

### 3.6 Gate-Array Design

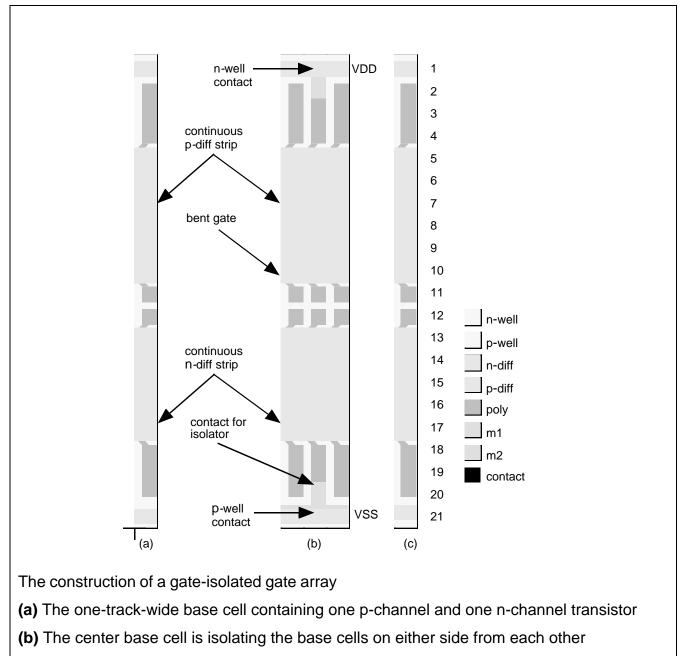

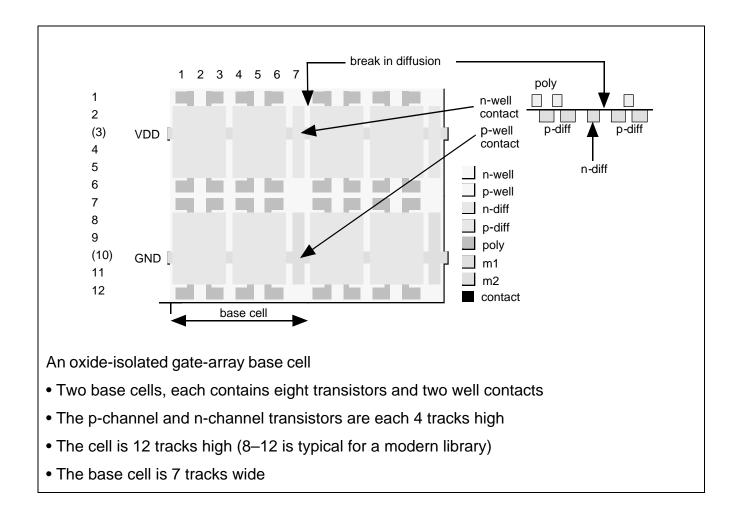

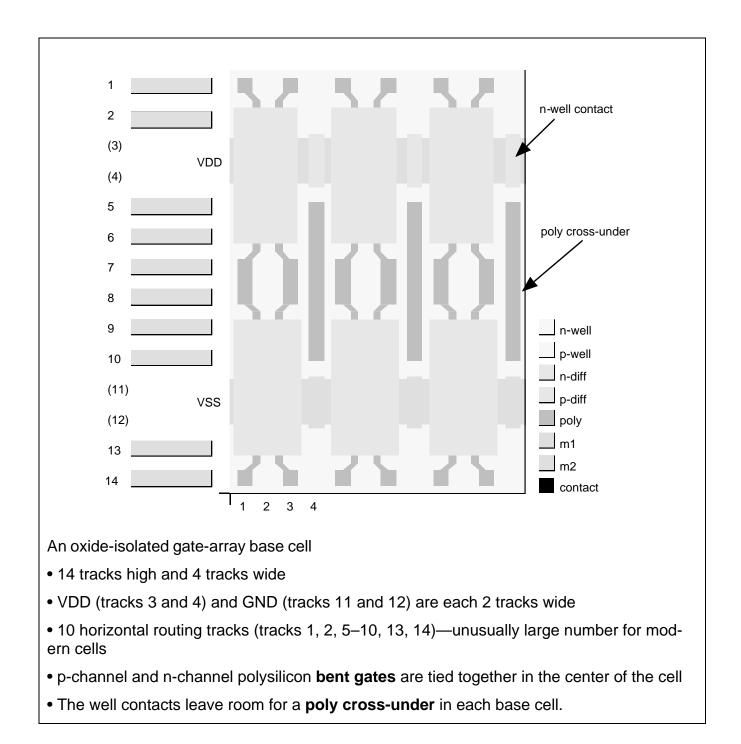

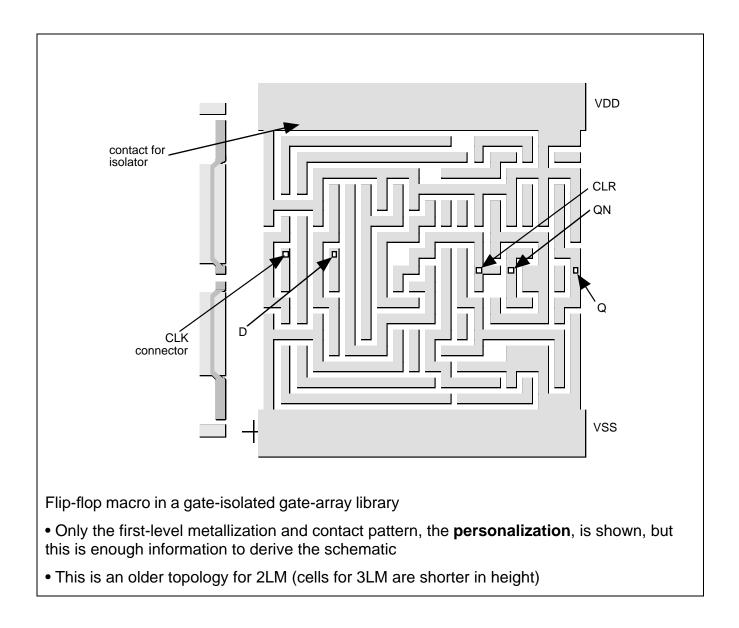

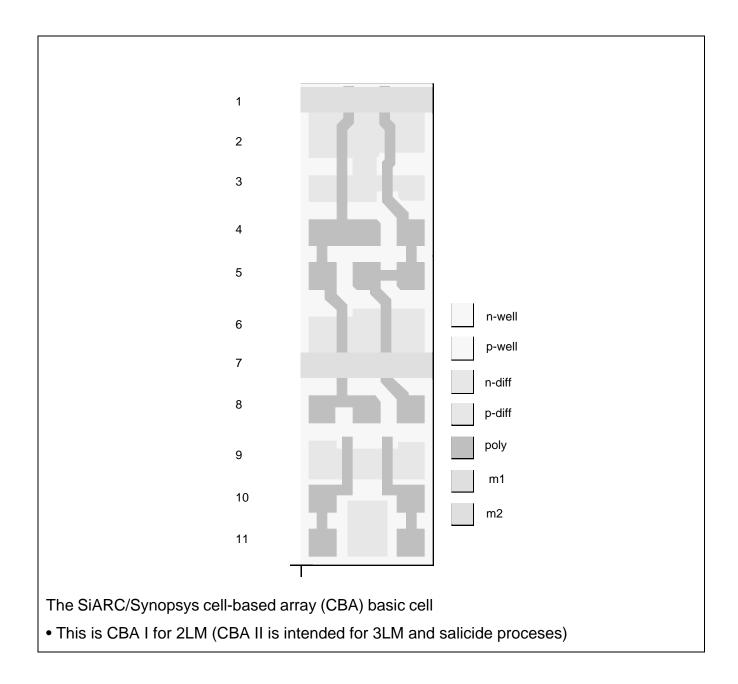

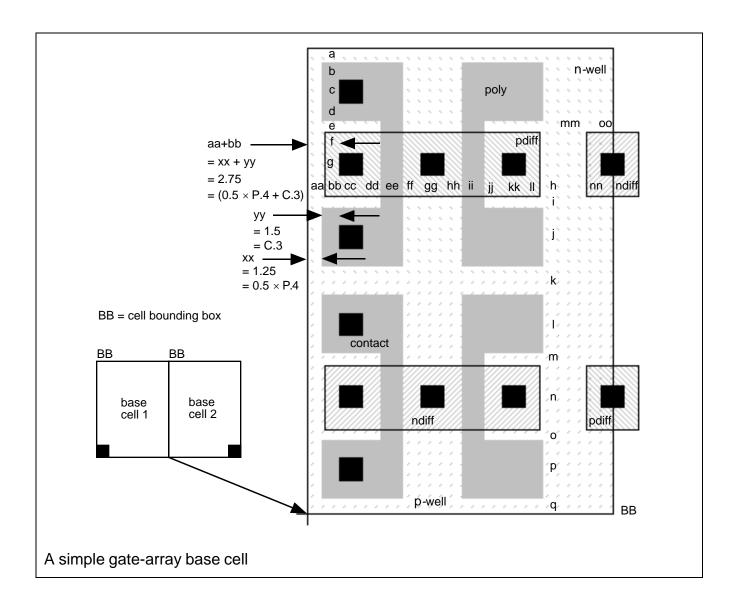

*Key words:* gate-array base cell (or base cell) • gate-array base (or base) • horizontal tracks • vertical track • gate isolation • isolator transistor • oxide isolation • oxide-isolated gate array

(c) The base cell is 21 tracks high (high for a modern cell library)

### 3.7 Standard-Cell Design

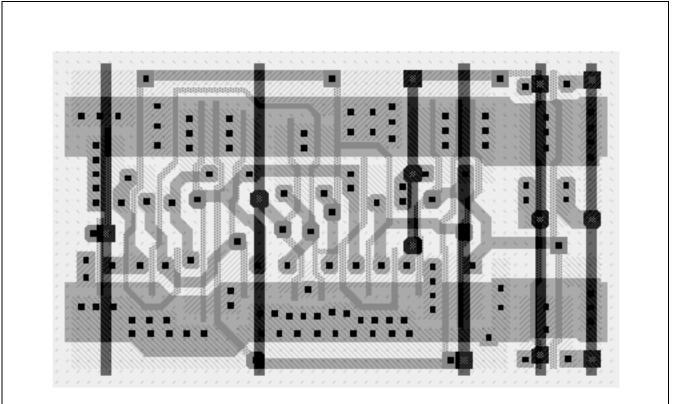

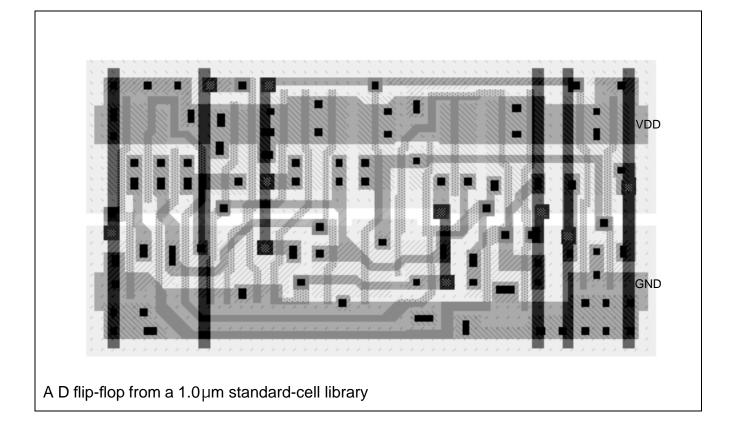

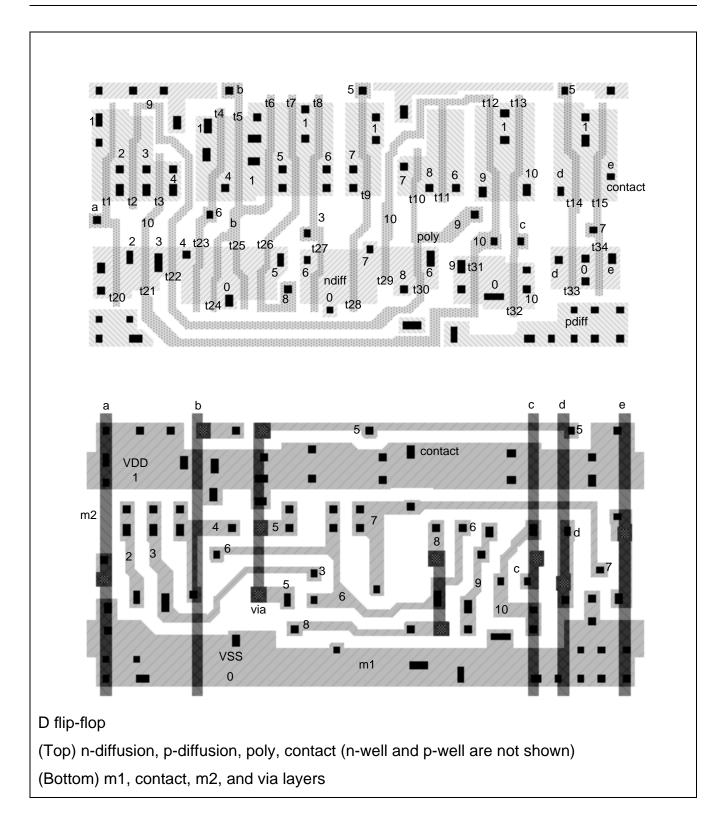

- A D flip-flop standard cell

- Performance-optimized library Area-optimized library

- Wide power buses and transistors for a performance-optimized cell

- Double-entry cell intended for a 2LM process and channel routing

- Five connectors run vertically through the cell on m2

- The extra short vertical metal line is an internal crossover

- bounding box (BB) abutment box (AB) physical connector abut

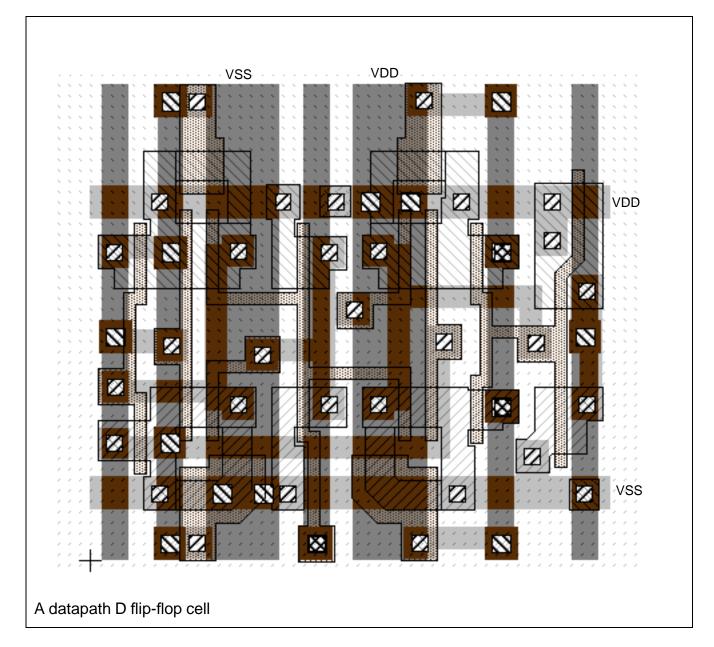

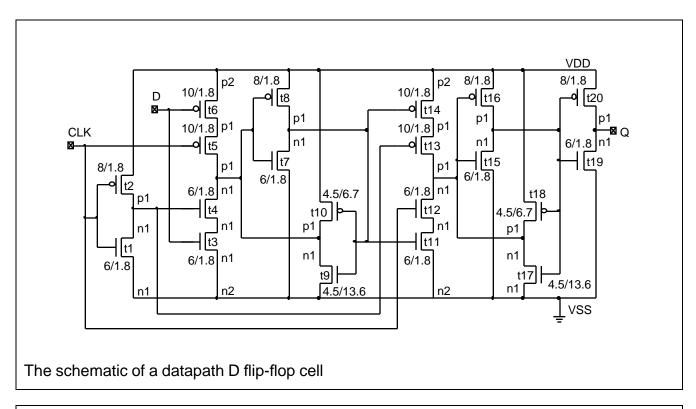

### 3.8 Datapath-Cell Design

(b)

A narrow datapath

(a) Implemented in a two-level metal process

(b) Implemented in a three-level metal process

ASICS... THE COURSE

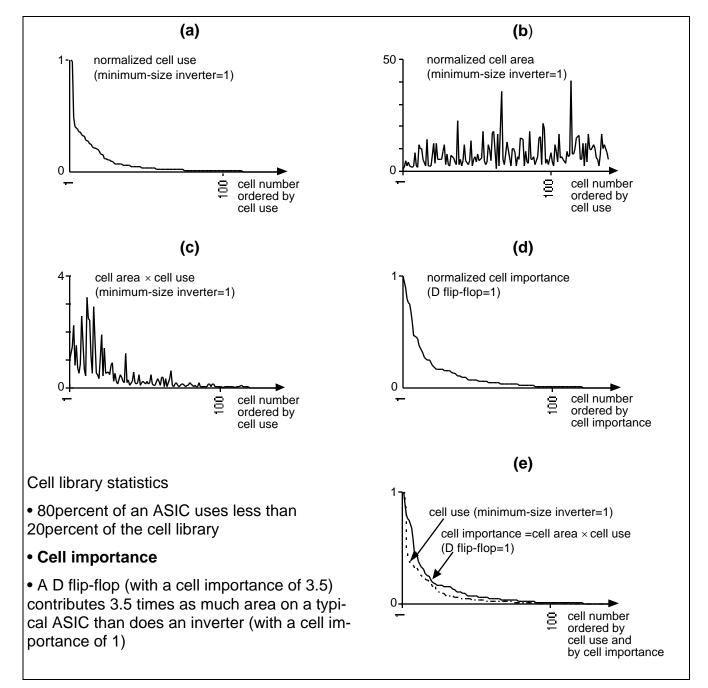

## 3.9 Summary

### Key concepts:

- Tau, logical effort, and the prediction of delay

- Sizes of cells, and their drive strengths

- Cell importance

- The difference between gate-array macros, standard cells, and datapath cells

# PROGRAMMABLE ASIC LOGIC CELLS

*Key concepts:* basic logic cell • multiplexer-based cell • look-up table (LUT) • programmable array logic (PAL) • influence of programming technology • timing • worst-case design

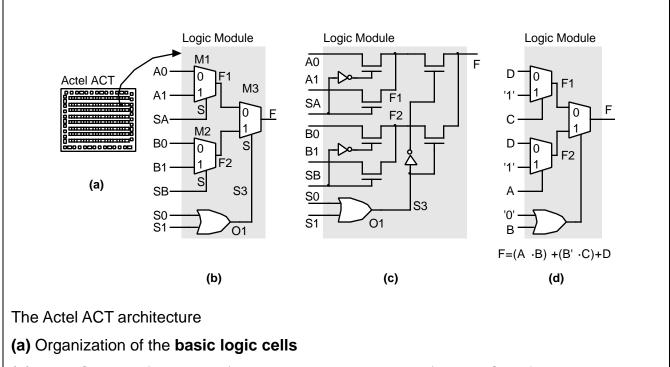

# 5.1 Actel ACT

# 5.1.1 ACT 1 Logic Module

(b) The ACT 1 Logic Module (LM, the Actel basic logic cell). The ACT 1 family uses just one type of LM. ACT 2 and ACT 3 FPGA families both use two different types of LM

(c) An example LM implementation using pass transistors (without any buffering)

(d) An example logic macro. Connect logic signals to some or all of the LM inputs, the remaining inputs to VDD or GND

#### 5.1.2 Shannon's Expansion Theorem

• We can use the Shannon expansion theorem to expand F =A·F(A='1') + A'·F(A='0')

Example:  $F = A' \cdot B + A \cdot B \cdot C' + A' \cdot B' \cdot C = A \cdot (B \cdot C') + A' \cdot (B + B' \cdot C)$

- F(A='1')=B·C' is the **cofactor** of F with respect to (**wrt**) A or F<sub>A</sub>

- If we expand F wrt B, F = A'  $\cdot$  B + A  $\cdot$  B  $\cdot$  C' + A'  $\cdot$  B'  $\cdot$  C = B  $\cdot$  (A' + A  $\cdot$  C') + B'  $\cdot$  (A'  $\cdot$  C)

- Eventually we reach the unique canonical form, which uses only minterms

- (A minterm is a product term that contains all the variables of F—such as A·B'·C)

Another example:  $F = (A \cdot B) + (B' \cdot C) + D$

- Expand F wrt B:  $F=B\cdot(A + D) + B'\cdot(C + D) = B\cdot F2 + B'\cdot F1$

- F = 2:1 MUX, with B selecting between two inputs: F(A='1') and F(A='0')

- F also describes the output of the ACT 1 LM

- Now we need to split up F1 and F2

- Expand F2 wrt A, and F1 wrt C: F2=A + D=(A·1) + (A'·D); F1=C + D=(C·1) + (C'·D)

- A, B, C connect to the select lines and '1' and D are the inputs of the MUXes in the ACT 1 LM

- Connections: A0=D, A1='1', B0=D, B1='1', SA=C, SB=A, S0='0', and S1=B

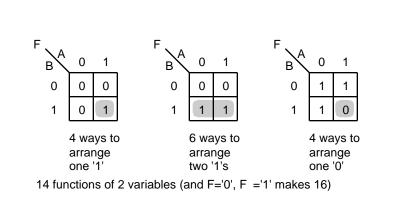

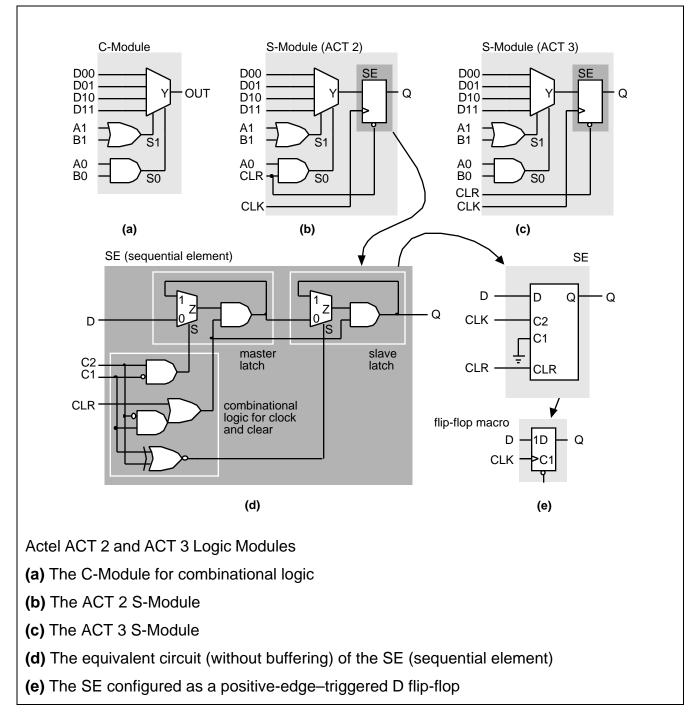

## 5.1.3 Multiplexer Logic as Function Generators

The 16 logic functions of 2 variables:

• 2 of the 16 functions are not very interesting (F='0', and F='1')

• There are 10 functions that we can implement using just one 2:1 MUX

• 6 functions are useful: INV, BUF, AND, OR, AND1-1, NOR1-1

|    |              | _                                | • • • • •                                           | Min-           | Min-      | Func- | M1 |   |   |

|----|--------------|----------------------------------|-----------------------------------------------------|----------------|-----------|-------|----|---|---|

|    | Function, F  | ction, F F= Canonical form terms | term<br>code                                        | tion<br>number | <b>A0</b> | A1    | SA |   |   |

| 1  | '0'          | '0'                              | '0'                                                 | none           | 0000      | 0     | 0  | 0 | 0 |

| 2  | NOR1-1(A, B) | (A+B')                           | A'∙B                                                | 1              | 0010      | 2     | В  | 0 | А |

| 3  | NOT(A)       | Α'                               | A'⋅B' + A'⋅B                                        | 0, 1           | 0011      | 3     | 0  | 1 | А |

| 4  | AND1-1(A, B) | A·B'                             | A-B'                                                | 2              | 0100      | 4     | А  | 0 | В |

| 5  | NOT(B)       | Β'                               | A'•B' + A•B'                                        | 0, 2           | 0101      | 5     | 0  | 1 | В |

| 6  | BUF(B)       | В                                | A'·B + A·B                                          | 1, 3           | 1010      | 6     | 0  | В | 1 |

| 7  | AND(A, B)    | A·B                              | A·B                                                 | 3              | 1000      | 8     | 0  | В | А |

| 8  | BUF(A)       | А                                | A·B' + A·B                                          | 2, 3           | 1100      | 9     | 0  | А | 1 |

| 9  | OR(A, B)     | A+B                              | A'·B + A·B' + A·B                                   | 1, 2, 3        | 1110      | 13    | В  | 1 | А |

| 10 | '1'          | '1'                              | $A' \cdot B' + A' \cdot B + A \cdot B' + A \cdot B$ | 0, 1, 2, 3     | 1111      | 15    | 1  | 1 | 1 |

Example of using the WHEEL functions to implement  $F=NAND(A, B)=(A \cdot B)'$

• 1. First express F as the output of a 2:1 MUX: we do this by expanding F wrt A (or wrt B; since F is symmetric)  $F=A\cdot(B') + A'\cdot('1')$

• 2. Assign WHEEL1 to implement INV(B), and WHEEL2 to implement '1'

• 3. Set the select input to the MUX connecting WHEEL1 and WHEEL2, S0+S1=A. We can do this using S0=A, S1='1'

The ACT 1 Logic Module as a Boolean function generator

(a) A 2:1 MUX viewed as a function wheel

(b) The ACT 1 Logic Module is two function wheels, an OR gate, and a 2:1 MUX

- A 2:1 MUX is a function wheel that can generate BUF, INV, AND-11, AND1-1, OR, AND

- WHEEL(A, B) = MUX(A0, A1, SA)

- MUX(A0, A1, SA)=A0·SA' + A1·SA

- The inputs (A0, A1, SA) ={A, B, '0', '1'}

- Each of the inputs (A0, A1, and SA) may be A, B, '0', or '1'

- The ACT 1 LM is built from two function wheels, a 2:1 MUX, and a two-input OR gate

- ACT 1 LM =MUX [WHEEL1, WHEEL2, OR(S0, S1)]

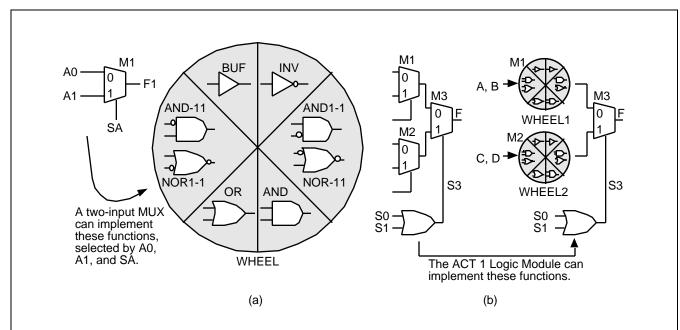

# 5.1.4 ACT 2 and ACT 3 Logic Modules

- ACT 1 requires 2 LMs per flip-flop: with unknown interconnect capacitance

- ACT 2 and ACT 3 use two types of LMs, one includes a D flip-flop

- ACT 2 **C-Module** is similar to the ACT 1 LM but can implement five-input logic functions

- combinatorial module implements combinational logic (blame MMI for the misuse of terms)

- ACT 2 **S-Module** (sequential module) contains a C-Module and a sequential element

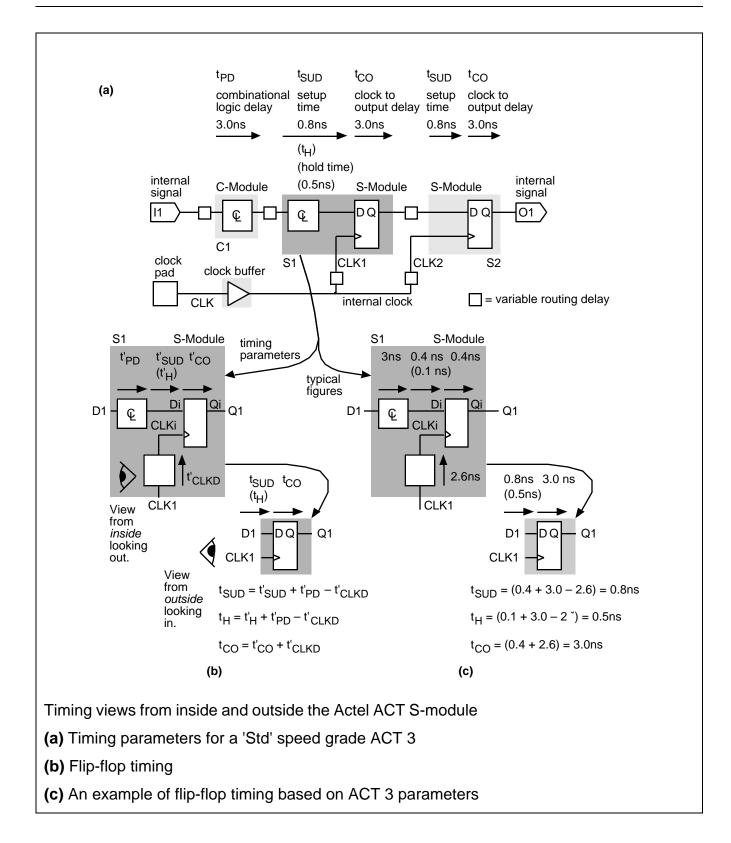

## 5.1.5 Timing Model and Critical Path

*Keywords and concepts:* timing model • deals only with internal logic • estimates delays • before place-and-route step • nondeterministic architecture • find slowest register–register delay or critical path

Example of timing calculations (a rather complex examination of internal module timing):

- The setup and hold times, measured *inside* (not outside) the S-Module, are  $t'_{SUD}$  and  $t'_{H}$  (a prime denotes parameters that are measured inside the S-Module)

- The clock–Q propagation delay is t'<sub>CO</sub>

- The parameters t'<sub>SUD</sub>, t'<sub>H</sub>, and t'<sub>CO</sub> are measured using the *internal* clock signal CLKi

- The propagation delay of the combinational logic inside the S-Module is t'PD

- The delay of the combinational logic that drives the flip-flop clock signal is t'<sub>CLKD</sub>

- From outside the S-Module, with reference to the outside clock signal CLK1:

$t_{SUD} = t'_{SUD} + (t'_{PD} - t'_{CLKD}), t_{H} = t'_{H} + (t'_{PD} - t'_{CLKD}), t_{CO} = t'_{CO} + t'_{CLKD}$

$\bullet$  We do not know the *internal* parameters  $t'_{SUD},\,t'_{H},$  and  $t'_{CO},$  but assume reasonable values:

t'<sub>SUD</sub>=0.4ns, t'<sub>H</sub>=0.1ns, t'<sub>CO</sub>=0.4ns.

- $t'_{PD}$  (combinational logic inside the S-Module) is equal to the C-Module delay, so  $t'_{PD}$ =3ns for the ACT 3

- We do not know t'<sub>CLKD</sub>; assume a value of t'<sub>CLKD</sub>=2.6ns (the exact value does not matter)

- Thus the *external* S-Module parameters are: t<sub>SUD</sub>=0.8ns, t<sub>H</sub>=0.5ns, t<sub>CO</sub>=3.0ns

- $\bullet$  These are the same as the ACT 3 S-Module parameters (I chose t'\_{CLKD} so they would be)

$\bullet$  Of the 3.0ns combinational logic delay: 0.4ns increases the setup time and 2.6ns increases the clock–output delay,  $t_{\rm CO}$

Actel says that the combinational logic delay is *buried* in the flip-flop setup time. But this

is borrowed money—you have to pay it back.

### 5.1.6 Speed Grading

- Speed grading (or speed binning) uses a binning circuit

- Measure  $t_{PD} = (t_{PLH} + t_{PHL})/2$  and use the fact that properties match across a chip

- Actel speed grades are based on 'Std' speed grade

- '1' speed grade is approximately 15 percent faster than 'Std'

- '2' speed grade is approximately 25 percent faster than 'Std'

- '3' speed grade is approximately 35 percent faster than 'Std'.

## 5.1.7 Worst-Case Timing

*Keywords and concepts:* Using synchronous design you worry about how slow your circuit may be—not how fast • **ambient temperature**,  $T_A • package case temperature, <math>T_C$  (military) • temperature of the chip, the **junction temperature**,  $T_J • nominal operating conditions: <math>V_{DD}$ =5.0V, and  $T_J$ =25°C • **worst-case commercial** conditions:  $V_{DD}$ =4.75V, and  $T_J$ =+70°C • always design using **worst-case timing • derating factors • critical path delay** between registers • **process corner** (slow–slow • fast–fast • slow–fast • fast–slow) • Commercial.  $V_{DD}$ =5V ± 5%,  $T_A$  (ambient)=0 to +70°C • Industrial.  $V_{DD}$ =5V ± 10%,  $T_A$  (ambient)=-40 to +85°C • Military:  $V_{DD}$ =5V ± 10%,  $T_C$  (case)=-55 to +125°C • Military: Standard MIL-STD-883C Class B • Military extended: unmanned spacecraft

| ACT 3 timing parameters |                       |        |      |      |      |      |  |

|-------------------------|-----------------------|--------|------|------|------|------|--|

|                         |                       | Fanout |      |      |      |      |  |

| Family                  | Delay                 | 1      | 2    | 3    | 4    | 8    |  |

| ACT 3-3 (data book)     | t <sub>PD</sub>       | 2.9    | 3.2  | 3.4  | 3.7  | 4.8  |  |

| ACT3-2 (calculated)     | t <sub>PD</sub> /0.85 | 3.41   | 3.76 | 4.00 | 4.35 | 5.65 |  |

| ACT3-1 (calculated)     | t <sub>PD</sub> /0.75 | 3.87   | 4.27 | 4.53 | 4.93 | 6.40 |  |

| ACT3-Std (calculated)   | t <sub>PD</sub> /0.65 | 4.46   | 4.92 | 5.23 | 5.69 | 7.38 |  |

| ACT 3 derating factors |                                         |      |      |      |      |      |      |  |

|------------------------|-----------------------------------------|------|------|------|------|------|------|--|

|                        | TemperatureT <sub>J</sub> (junction)/°C |      |      |      |      |      |      |  |

| V <sub>DD</sub> /V     | -55                                     | -40  | 0    | 25   | 70   | 85   | 125  |  |

| 4.5                    | 0.72                                    | 0.76 | 0.85 | 0.90 | 1.04 | 1.07 | 1.17 |  |

| 4.75                   | 0.70                                    | 0.73 | 0.82 | 0.87 | 1.00 | 1.03 | 1.12 |  |

| 5.00                   | 0.68                                    | 0.71 | 0.79 | 0.84 | 0.97 | 1.00 | 1.09 |  |

| 5.25                   | 0.66                                    | 0.69 | 0.77 | 0.82 | 0.94 | 0.97 | 1.06 |  |

| 5.5                    | 0.63                                    | 0.66 | 0.74 | 0.79 | 0.90 | 0.93 | 1.01 |  |

### 5.1.8 Actel Logic Module Analysis

. . . .

• Actel uses a fine-grain architecture which allows you to use almost all of the FPGA

• Synthesis can map logic efficiently to a fine-grain architecture

• Physical symmetry simplifies place-and-route (swapping equivalent pins on opposite sides of the LM to ease routing)

- Matched to small antifuse programming technology

- LMs balance efficiency of implementation and efficiency of utilization

- A simple LM reduces performance, but allows fast and robust place-and-route

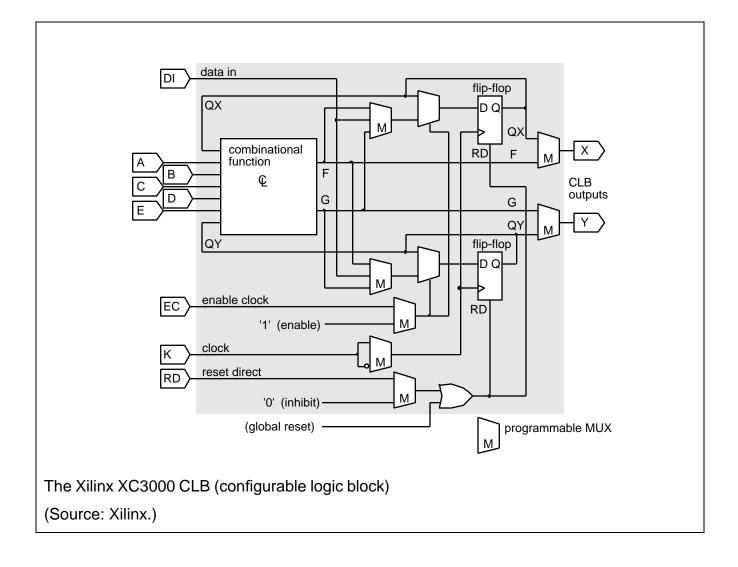

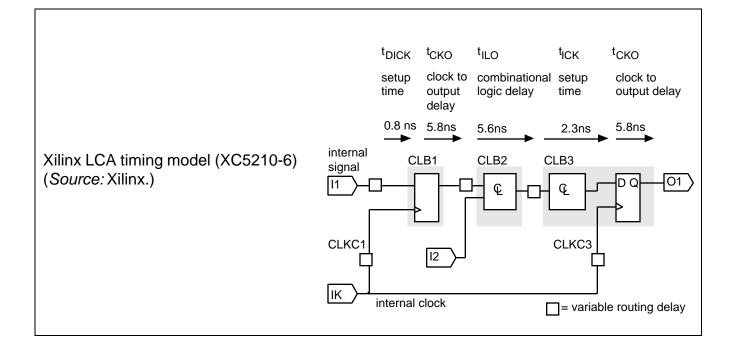

# **5.2** Xilinx LCA

Keywords and concepts: Xilinx LCA (a trademark, logic cell array) • configurable logic block

### • coarse-grain architecture

### 5.2.1 XC3000 CLB

• A 32-bit look-up table (LUT)

CLB propagation delay is fixed (the LUT access time) and independent of the logic function

• 7 inputs to the XC3000 CLB: 5 CLB inputs (A–E), and 2 flip-flop outputs (QX and QY)

• 2 outputs from the LUT (F and G). Since a 32-bit LUT requires only five variables to form a unique address  $(32=2^5)$ , there are several ways to use the LUT:

• Use 5 of the 7 possible inputs (A–E, QX, QY) with the entire 32-bit LUT (the CLB outputs (F and G) are then identical)

• Split the 32-bit LUT in half to implement 2 functions of 4 variables each; choose 4 input variables from the 7 inputs (A–E, QX, QY).You have to choose 2 of the inputs from the 5 CLB inputs (A–E); then one function output connects to F and the other output connects to G.

• You can split the 32-bit LUT in half, using one of the 7 input variables as a select input to a 2:1 MUX that switches between F and G (to implemen some functions of 6 and 7 variables).

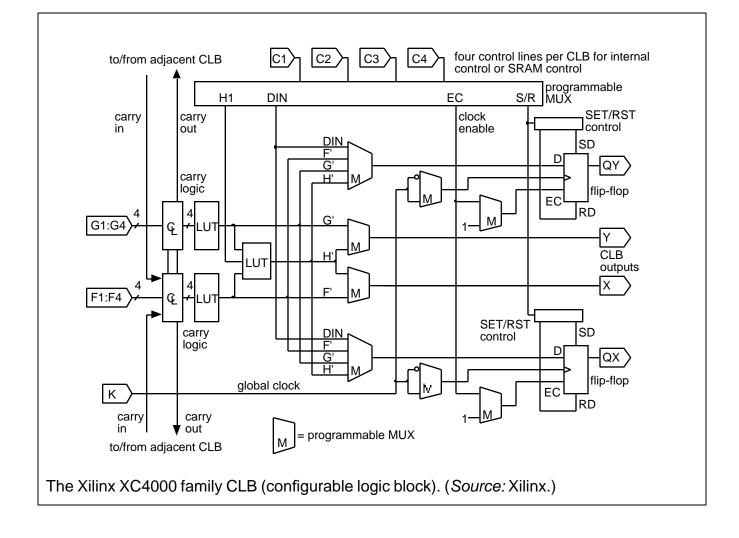

### 5.2.2 XC4000 Logic Block

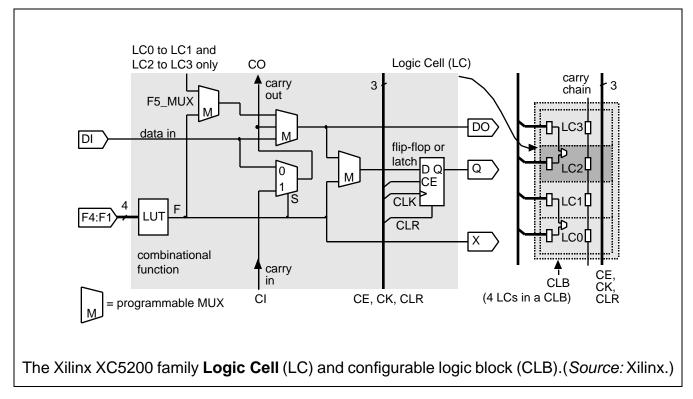

### 5.2.3 XC5200 Logic Block

## 5.2.4 Xilinx CLB Analysis

The use of a LUT has advantages and disadvantages:

- An inverter is as slow as a five-input NAND

- A LUT simplifies timing of synchronous logic

- Matched to large SRAM programming technology

Xilinx uses two speed-grade systems:

- Maximum guaranteed toggle rate of a CLB flip-flop (in MHz) as a suffix—higher is faster

- Example: Xilinx XC3020-125 has a toggle frequency of 125MHz

- Delay time of the combinational logic in a CLB in ns—lower is faster

- Example: XC4010-6 has t<sub>ILO</sub>=6.0ns

- Correspondence between grade and  $t_{\rm ILO}$  is fairly accurate for the XC2000, XC4000, and XC5200 but not for the XC3000

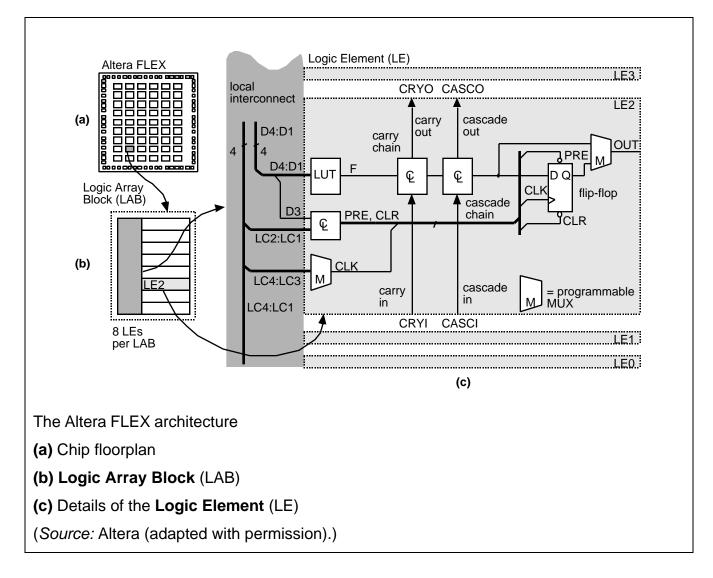

# 5.3 Altera FLEX

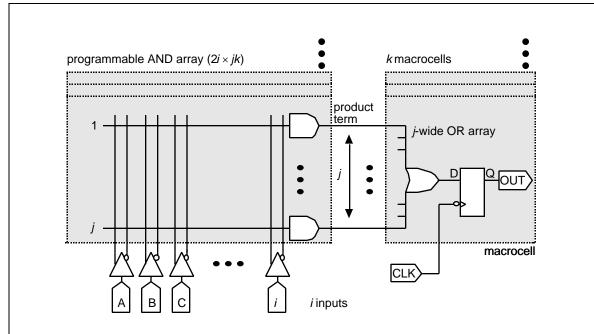

# 5.4 Altera MAX

A registered PAL with *i* inputs, *j* product terms, and *k* macrocells. (*Source:* Altera (adapted with permission).)

Features and keywords:

- product-term line

- programmable array logic

- bit line

- word line

- programmable-AND array (or product-term array)

- pull-up resistor

- wired-logic

- wired-AND

- macrocell

- 22V10 PLD

## 5.4.1 Logic Expanders

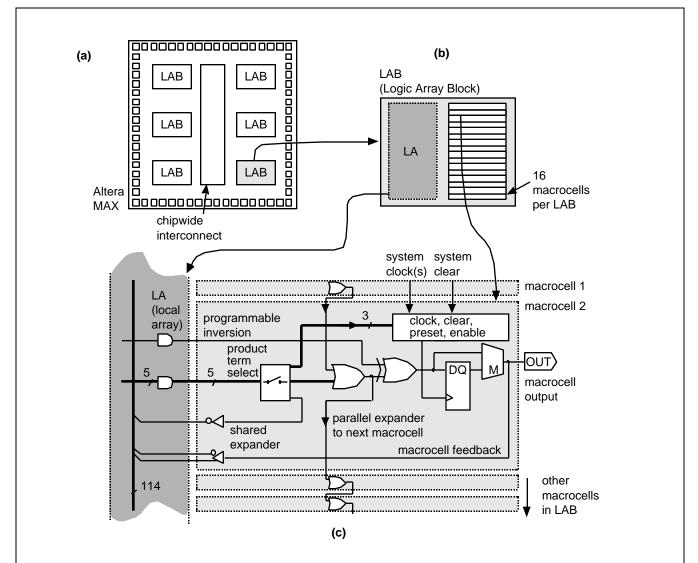

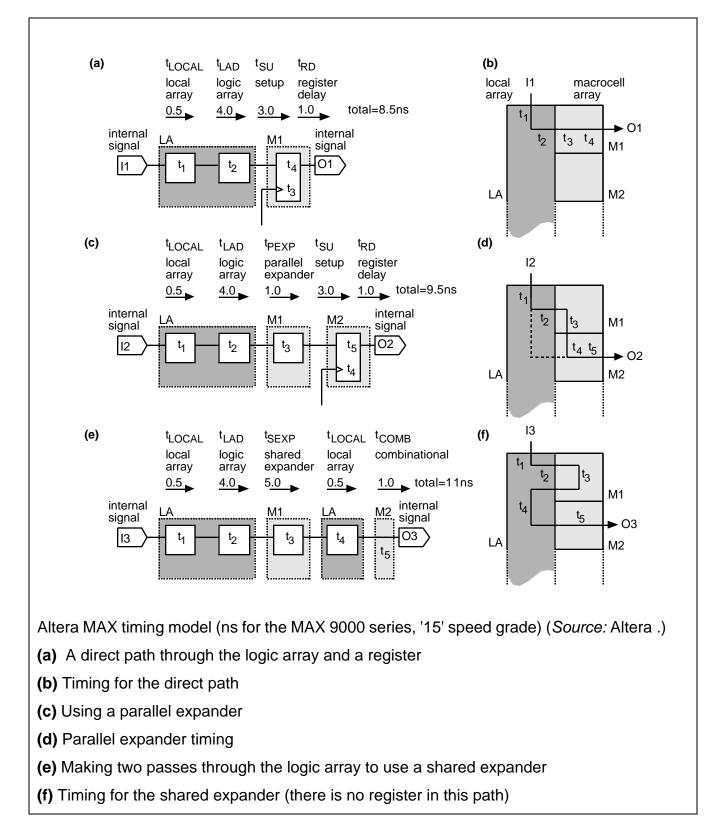

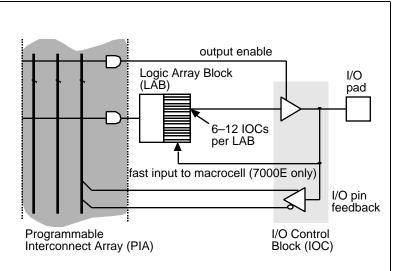

The Altera MAX architecture (the macrocell details vary between the MAX families—the functions shown here are closest to those of the MAX 9000 family macrocells) (*Source:* Altera (adapted with permission).) (a) Organization of logic and interconnect (b) LAB (Logic Array Block) (c) Macrocell

Features:

- Logic expanders and expander terms (helper terms) increase term efficiency

- Shared logic expander (shared expander, intranet) and parallel expander (internet)

- Deterministic architecture allows deterministic timing before logic assignment

- Any use of two-pass logic breaks deterministic timing

- Programmable inversion increases term efficiency

### 5.4.2 Timing Model

## 5.4.3 Power Dissipation in Complex PLDs

Key points: static power • Turbo Bit

# 5.5 Summary

*Key points:* The use of multiplexers, look-up tables, and programmable logic arrays • The difference between fine-grain and coarse-grain FPGA architectures • Worst-case timing design • Flip-flop timing • Timing models • Components of power dissipation in programmable ASICs • Deterministic and nondeterministic FPGA architectures

# 5.6 Problems

# PROGRAMMABLE ASIC I/O CELLS

# Key concepts:

Input/output cell (I/O cell) • I/O requirements • DC output • AC output • DC input • AC input •

Clock input • Power input

# 6.1 DC Output

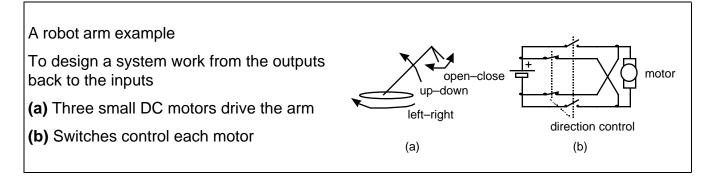

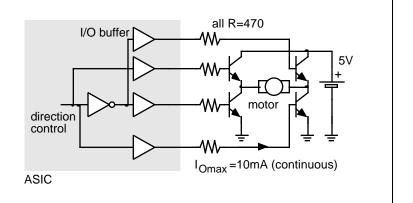

A circuit to drive a small electric motor (0.5A) using ASIC I/O buffers

Work from the outputs to the inputs

The 470 resistors drop up to 5V if an output buffer current approaches 10mA, reducing the drive to the output transistors

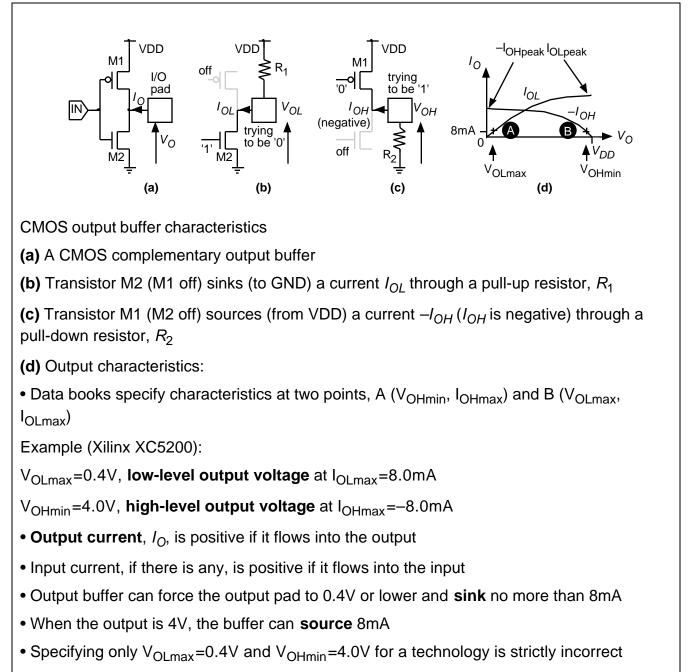

• We do not know the value of I<sub>OLpeak</sub> or I<sub>OLpeak</sub> (typical values are 50–200mA)

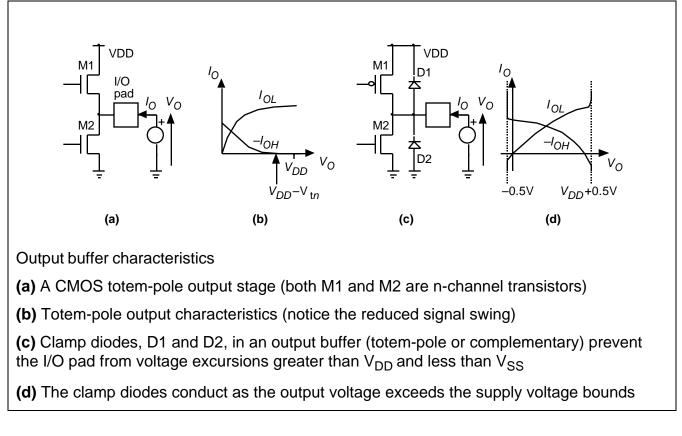

## 6.1.1 Totem-Pole Output

*Keywords:* totem-pole output buffer • similar to TTL totem-pole output • two n-channel transistors in a stack • reduced output voltage swing

## 6.1.2 Clamp Diodes

# 6.2 AC Output

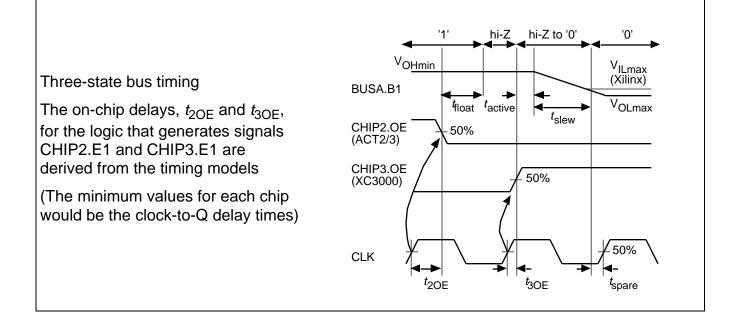

*Keywords:* bus transceivers • bus transaction (a sequence of signals on a bus) • floating a bus

• bus keeper • trip points • three-stated (high-impedance or hi-Z) • time to float • disable time,

time to begin hi-Z, or time to turn off • slew • sustained three-state (s/t/s) • turnaround cycle

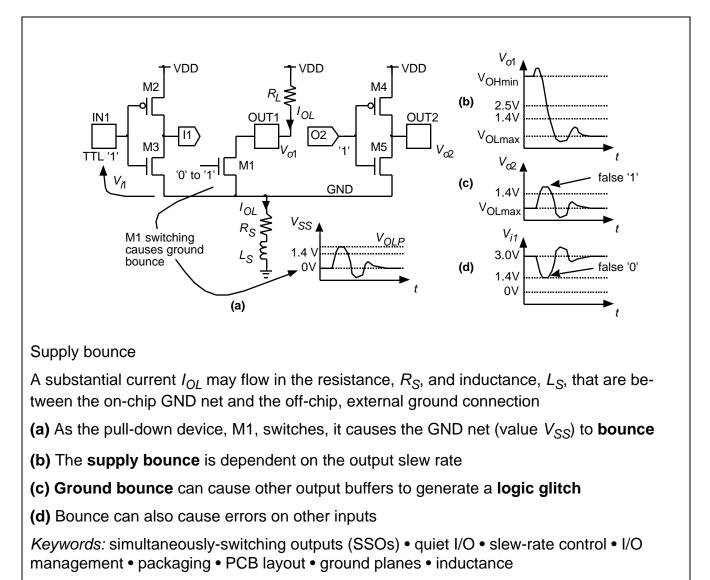

## 6.2.1 Supply Bounce

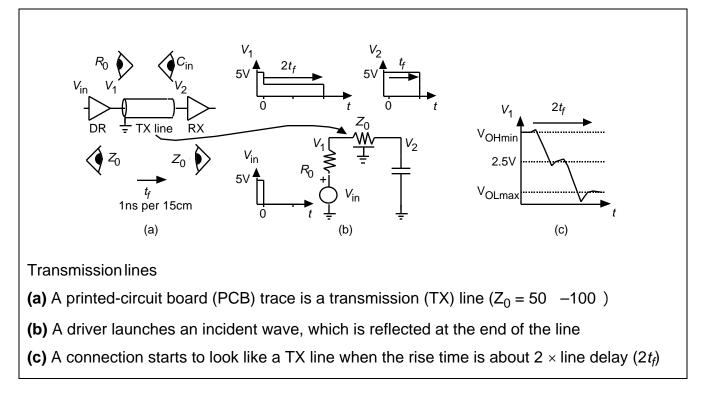

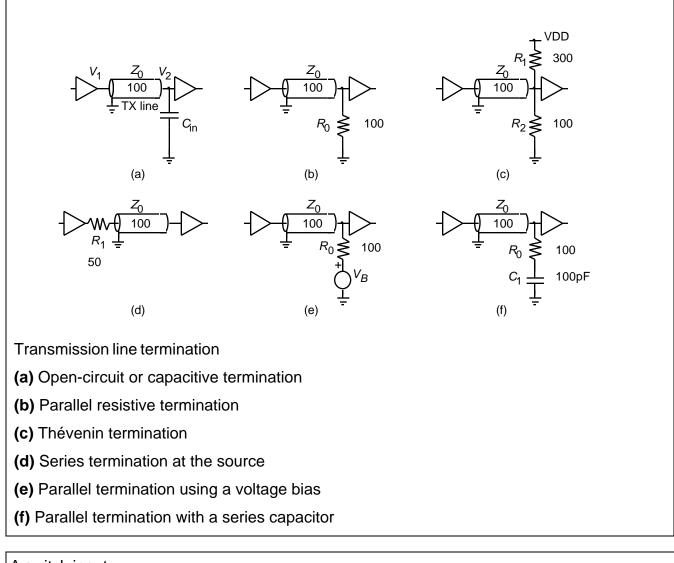

### 6.2.2 Transmission Lines

# 6.3 DC Input

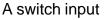

(a) A pushbutton switch V<sub>i1</sub> Switch closes, connected to an input buffer bounces, and VDD R<sub>PU</sub> 5V closes again. I/O with a pull-up resistor 5–50k pad V<sub>i2</sub> (b) As the switch bounces 12 1.4V several pulses may be 0V input Cin t<sub>1</sub>  $t_4$ generated V<sub>i2</sub> buffer 10pF We might have to **debounce**  $t_2 t_3$ *t*5 this signal using an SR flip-flop (a) (b) or small state machine

# DC input

(a) A Schmitt-trigger inverter • lower switching threshold • upper switching threshold • difference between thresholds is the hysteresis

(b) A noisy input signal

(c) Output from an inverter with no hysteresis

(d) Hysteresis helps prevent glitches

(e) A typical FPGA input buffer with a hysteresis of 200mV and a threshold of 1.4V

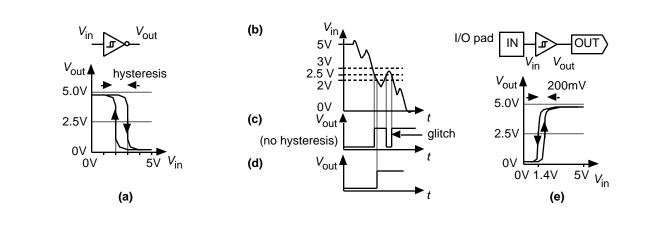

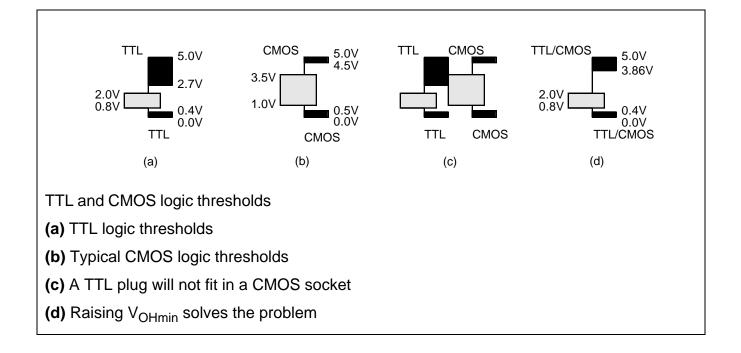

## 6.3.1 Noise Margins

(f) CMOS plugs fit CMOS sockets and the clearances are the noise margins

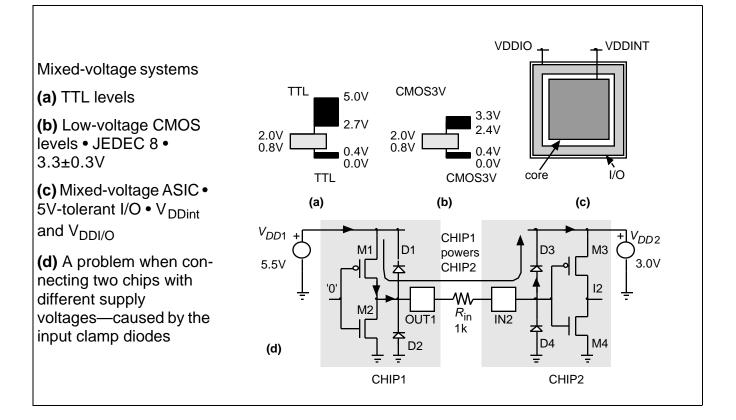

## 6.3.2 Mixed-Voltage Systems

| FPGA logic thresholds |             |       |                 |     |                                 |      |      |                                |      |      |      |     |

|-----------------------|-------------|-------|-----------------|-----|---------------------------------|------|------|--------------------------------|------|------|------|-----|

|                       | I/O options |       | Input<br>levels |     | Output levels (high<br>current) |      |      | Output levels (low<br>current) |      |      |      |     |

| XC3000                | TTL         |       | 2.0             | 0.8 | 3.86                            | -4.0 | 0.40 | 4.0                            |      |      |      |     |

|                       | CMOS        |       | 3.85            | 0.9 | 3.86                            | -4.0 | 0.40 | 4.0                            |      |      |      |     |

| XC3000L               |             |       | 2.0             | 0.8 | 2.40                            | -4.0 | 0.40 | 4.0                            | 2.80 | -0.1 | 0.2  | 0.1 |

| XC4000                |             |       | 2.0             | 0.8 | 2.40                            | -4.0 | 0.40 | 12.0                           |      |      |      |     |

| XC4000H               | TTL         | TTL   | 2.0             | 0.8 | 2.40                            | -4.0 | 0.50 | 24.0                           |      |      |      |     |

|                       | CMOS        | CMOS  | 3.85            | 0.9 | 4.00                            | -1.0 | 0.50 | 24.0                           |      |      |      |     |

| XC8100                | TTL         | R     | 2.0             | 0.8 | 3.86                            | -4.0 | 0.50 | 24.0                           |      |      |      |     |

|                       | CMOS        | С     | 3.85            | 0.9 | 3.86                            | -4.0 | 0.40 | 4.0                            |      |      |      |     |

| ACT 2/3               |             |       | 2.0             | 0.8 | 2.4                             | -8.0 | 0.50 | 12.0                           | 3.84 | -4.0 | 0.33 | 6.0 |

| FLEX10k               |             | 3V/5V | 2.0             | 0.8 | 2.4                             | -4.0 | 0.45 | 12.0                           |      |      |      |     |

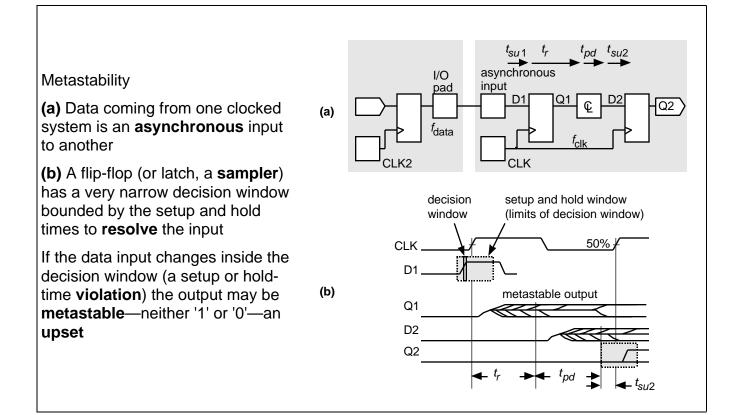

# 6.4 AC Input

*Keywords and concepts:* input bus • sampled data • clock frequency of 100kHz • FPGA • system clock • 10MHz • Data should be at the flip-flop input at least the flip-flop setup time before the clock edge. Unfortunately there is no way to guarantee this; the data clock and the system clock are completely independent

# 6.4.1 Metastability

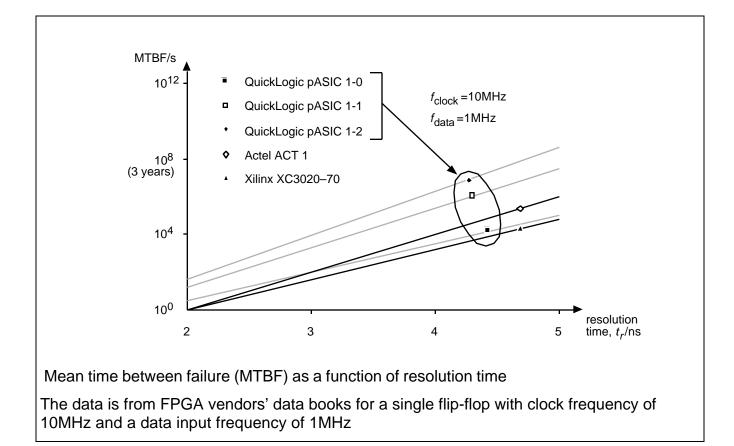

| Metastability parameters for FPGA flip-flops (not guaranteed by the vendors) |                   |          |  |  |  |  |

|------------------------------------------------------------------------------|-------------------|----------|--|--|--|--|

| FPGA                                                                         | T <sub>0</sub> /s | ₀/s      |  |  |  |  |

| Actel ACT 1                                                                  | 1.0E–09           | 2.17E–10 |  |  |  |  |

| Xilinx XC3020-70                                                             | 1.5E–10           | 2.71E-10 |  |  |  |  |

| QuickLogic QL12x16-0                                                         | 2.94E–11          | 2.91E-10 |  |  |  |  |

| QuickLogic QL12x16-1                                                         | 8.38E–11          | 2.09E-10 |  |  |  |  |

| QuickLogic QL12x16-2                                                         | 1.23E–10          | 1.85E–10 |  |  |  |  |

| Altera MAX 7000                                                              | 2.98E-17          | 2.00E-10 |  |  |  |  |

| Altera FLEX 8000                                                             | 1.01E–13          | 7.89E-11 |  |  |  |  |

## The mean time between upsets (MTBU) or MTBF is

$MTBU = \frac{1}{\rho f_{clock} f_{data}} = \frac{exp t_{f'} c}{f_{clock} f_{data}}$

where  $f_{clock}$  is the clock frequency and  $f_{data}$  is the data frequency

A **synchronizer** is built from two flip-flops in cascade, and greatly reduces the effective values of  $_{c}$  and T<sub>0</sub> over a single flip-flop. The penalty is an extra clock cycle of latency.

# 6.5 Clock Input

<sup>t</sup>ICKOF

(b)

## 6.5.1 Registered Input

CLK

t<sub>PG</sub> (variable)

(a)

(b) Timing diagram

# 6.6 Power Input

# 6.6.1 Power Dissipation

| Thermal characteristics of ASIC packages |           |                                   |                                                 |                                                 |  |  |  |  |

|------------------------------------------|-----------|-----------------------------------|-------------------------------------------------|-------------------------------------------------|--|--|--|--|

| Package                                  | Pin count | Max. power<br>P <sub>max</sub> /W | <sub>JA</sub> /°CW <sup>−1</sup><br>(still air) | <sub>JA</sub> /°CW <sup>−1</sup><br>(still air) |  |  |  |  |

| CPGA                                     | 84        |                                   | 33                                              | 32–38                                           |  |  |  |  |

| CQFP                                     | 84        |                                   | 40                                              |                                                 |  |  |  |  |

| CQFP                                     | 172       |                                   | 25                                              |                                                 |  |  |  |  |

| VQFP                                     | 80        |                                   | 68                                              |                                                 |  |  |  |  |

## 6.6.2 Power-On Reset

*Key concepts:* Power-on reset sequence • Xilinx FPGAs configure all flip-flops (in either the CLBs or IOBs) as either SET or RESET • after chip programming is complete, the global SET/RESET signal forces all flip-flops on the chip to a known state • this may determine the initial state of a state machine, for example

## 6.7 Xilinx I/O Block

## 6.7.1 Boundary Scan

*Key concepts:* IEEE boundary-scan standard 1149.1 • Many FPGAs contain a standard boundary-scan test logic structure with a four-pin interface • **in-system programming** (ISP)

## 6.8 Other I/O Cells

A simplified block diagram of the Altera I/O Control Block (IOC) used in the MAX 5000 and MAX 7000 series

The **I/O pin feedback** allows the I/O pad to be isolated from the macrocell

It is thus possible to use a LAB without using up an I/O pad (as you often have to do using a PLD such as a 22V10)

The **PIA** is the chipwide interconnect

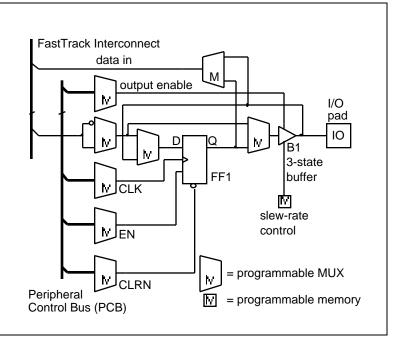

A simplified block diagram of the Altera **I/O Element** (IOE), used in the FLEX 8000 and 10k series

The MAX 9000 IOC (I/O Cell) is similar

The FastTrack Interconnect bus is the chipwide interconnect

The **Peripheral Control Bus** (PCB) is used for control signals common to each IOE

## 6.9 Summary

| Key concepts:                                                             |

|---------------------------------------------------------------------------|

| Outputs can typically source or sink 5–10mA continuously into a DC load   |

| Outputs can typically source or sink 50–200mA transiently into an AC load |

| Input buffers can be CMOS (threshold at 0.5 $V_{DD}$ ) or TTL (1.4V)      |

| Input buffers normally have a small hysteresis (100–200mV)                |

| CMOS inputs must never be left floating                                   |

| Clamp diodes to GND and VDD are present on every pin                      |

| Inputs and outputs can be registered or direct                            |

| I/O registers can be in the I/O cell or in the core                       |

| Metastability is a problem when working with asynchronous inputs          |

| Questions<br>In which design all                                                                             | opt1                        | opt2                                      | opt3                                         | opt4                                    | opt<br>5 | opt<br>6 | Answer                                |

|--------------------------------------------------------------------------------------------------------------|-----------------------------|-------------------------------------------|----------------------------------------------|-----------------------------------------|----------|----------|---------------------------------------|

| circuitry and all<br>interconnections are<br>designed?<br>Which design                                       | full custom<br>design.      | semi-custom<br>design                     | gate<br>array<br>design                      | transistor<br>design                    |          |          | full custom<br>design.                |

| contains only the<br>interconnections<br>designed?<br>In which method                                        | full custom<br>design       | semi-<br>custom<br>design<br>hierarchical | gate<br>array<br>design .<br>algorithm<br>ic | transistor<br>design<br>semi-<br>docign |          |          | gate array<br>design .<br>hierarchica |

| regularity is used to reduce complexity?                                                                     | random<br>approach          | approach.                                 | approach<br>area of                          | design<br>approach<br>length of         |          |          | l approach.                           |

| Size of the die is determined using                                                                          | transistor<br>size          | inverter size                             | the<br>circuitry .<br>gate                   | the<br>circuitry                        |          |          | area of the<br>circuitry              |

| Which design is faster?                                                                                      | full custom<br>design       | semi-custom<br>design<br>computer         | array<br>design .<br>compute                 | transistor<br>design<br>silicon         |          |          | gate array<br>design .<br>computer    |

| Which has relatively<br>low-level<br>capabilities?                                                           | hand-<br>crafted<br>designs | assisted<br>textual entry                 | r assisted<br>graphical<br>entry             | compiler-<br>based<br>design            |          |          | assisted<br>textual<br>entry .        |

| Computer-assisted<br>graphical entry is                                                                      | monochrom                   | grayscale                                 | entry                                        | uesign                                  |          |          | monochro                              |

| done through<br>Which method is                                                                              | е.                          | graphics                                  | bichrome<br>compute                          | trichrome<br>silicon                    |          |          | me .<br>computer                      |

| used for verification<br>along with                                                                          | hand-<br>crafted            | computer<br>assisted                      | r assisted<br>graphical                      | compiler-<br>based                      |          |          | assisted<br>graphical                 |

| generation?<br>Whih method uses                                                                              | designs                     | textual entry                             | entry.<br>compute                            | design<br>silicon                       |          |          | entry.<br>silicon                     |

| high level                                                                                                   | hand-<br>crafted            | computer<br>assisted                      | r assisted                                   | compiler-<br>based                      |          |          | compiler-<br>based                    |

| programming<br>language?<br>The set of design                                                                | designs                     | textual entry                             | graphical<br>entry                           | design .                                |          |          | design .                              |

| rules does not give<br>When setting the<br>voltage for an<br>external device that<br>must interface with     | widths                      | spacing                                   | colours .                                    | overlaps                                |          |          | colours .                             |

| an FPGA, you must<br>Which of the<br>following digital IC<br>logic families is most<br>susceptible to static | VCCIO .                     | VDDIN                                     | VDDiO                                        | VCCIN                                   |          |          | VCCIO .                               |

| discharge?<br>Which of the                                                                                   | RTL<br>mechanical           | ECL                                       | MOS.                                         | TTL<br>under                            |          |          | MOS.<br>electrostati                  |

| following is a                                                                                               | shock                       | electrostatic                             | fan out                                      | voltage                                 |          |          | С                                     |

| concern when using<br>CMOS type devices?<br>Which of the                                                                                      |                                             | discharge .                                        |                                 |                                      | discharge .                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|----------------------------------------------------|---------------------------------|--------------------------------------|--------------------------------------|

| following is not a<br>solution to interface<br>problems between<br>CMOS and TTL?<br>Which of the<br>following is not a<br>common logic family | pull- up<br>resistor                        | pull- down<br>resistor .                           | level-<br>shifter               | buffer                               | pull- down<br>resistor .             |

| used today?                                                                                                                                   | RTL.                                        | ECL                                                | TTL                             | CMOS                                 | RTL.                                 |

| The output current<br>for a LOW output is<br>called a(n)<br>Which of the                                                                      | exit current                                | sink<br>current.                                   | ground<br>current               | fan- out.                            | sink<br>current.                     |

| following are not<br>characteristics of TTL<br>logic gates?<br>) Which of the<br>following output<br>levels would not be                      | Totem-<br>pole output                       | Bipolar<br>transistors                             | CMOS<br>transistor<br>s .       | Multiemitt<br>er<br>transistors      | CMOS<br>transistors                  |

| a valid LOW for a<br>TTL gate?<br>A family of logic<br>devices designed for<br>extremely high<br>speed applications is                        | 0.3                                         | 0.5                                                | 0.2                             | All are<br>valid .                   | All are<br>valid .                   |

| called                                                                                                                                        | NMOS                                        | ECL .<br>if left open                              | PMOS                            | TTL                                  | ECL .                                |

| ) Unused inputs on<br>TTL, AND, and NAND<br>gates<br>) The lower<br>transistor of a<br>totem- nole output                                     | degrade<br>the gate's<br>noise<br>immunity. | will have the<br>same effect<br>as HIGH<br>inputs. | should<br>be tied<br>HIGH.      | All of the<br>above are<br>correct . | All of the<br>above are<br>correct . |

| totem- pole output<br>is OFF when the gate<br>output is<br>) The input                                                                        | HIGH.                                       | malfunctioni<br>ng                                 | LOW                             | over<br>driven                       | HIGH.                                |

| transistor on a TTL<br>circuit is unusual in<br>that it has                                                                                   | multiple<br>bases.                          | no collector.<br>more<br>stringent                 | no base<br>higher               | multiple<br>emitters .               | multiple<br>emitters .               |

| ) The 54XX TTL IC series is the military version and has                                                                                      | a wider<br>temperatur<br>e range.           | power<br>supply<br>requirement<br>s.               | current<br>output<br>capability | all of the<br>above                  | a wider<br>temperatur<br>e range.    |

| Which potential<br>problem must be<br>overcome when<br>interfacing TTL to<br>CMOS?<br>Typical TTL LOW<br>level output voltage | The HIGH<br>output<br>voltage<br>may be too<br>low. | The LOW<br>output<br>voltage may<br>be too high. | The<br>HIGH<br>output<br>voltage<br>may be<br>too high. | The<br>output<br>current<br>may not<br>be<br>sufficient | The HIGH<br>output<br>voltage<br>may be too<br>low. |

|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------|

| is<br>When the outputs of<br>several open-                                                                                    | 0.3V.                                               | 0.0V                                             | 3.4V                                                    | 4.0V                                                    | 0.3V.                                               |

| collector TTL gates<br>are connected                                                                                          | produce                                             |                                                  | are<br>ANDed                                            | produce                                                 |                                                     |

| together, the gate                                                                                                            | more fan-                                           | usually                                          | together                                                | more                                                    | are ANDed                                           |

| outputs<br>) The abbreviated<br>designation for<br>output current with                                                        | out.                                                | burn out.                                        |                                                         | voltage.                                                | together .                                          |

| a LOW output is<br>The input transistor<br>(Q 1) of a TTL gate                                                                | OOL                                                 | IOL .                                            | iOH                                                     | IIH                                                     | IOL                                                 |

| acts like<br>The unused input<br>for a NOR gate                                                                               | NAND                                                | NOR.                                             | AND<br>another<br>unused                                | OR<br>both B and                                        | AND                                                 |

| should be tied to<br>Which of the<br>following output<br>levels would be a                                                    | HIGH.                                               | ground                                           | input.                                                  | C                                                       | ground.                                             |

| valid HIGH for a TTL                                                                                                          | 2.01/                                               | 2.04                                             | F 4                                                     | All are                                                 | All are                                             |

| gate?                                                                                                                         | 3.0V                                                | 2.6V                                             | 5.1                                                     | valid .                                                 | valid.                                              |

| The noise margin for a<br>standard TTL gate is<br>) When a TTL gate<br>output connects to a<br>CMOS gate, what must<br>be added to the circuit?<br>Which of the following<br>levels would not be a                                                                                                                      | <b>1.0V</b><br>a decoupling<br>capacitor                      | 0.4V .<br>a pull- up<br>resistor .                       | 1.4V<br>a pull-<br>down<br>resistor                                     | 0.8V<br>an open-<br>collector<br>gate                        | <b>0.4V</b> .<br>a pull- up<br>resistor .                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| valid LOW for a TTL                                                                                                                                                                                                                                                                                                     |                                                               |                                                          |                                                                         | All are                                                      |                                                                                                            |

| <ul> <li>valid LOW for a TTL</li> <li>gate?</li> <li>) What advantage does</li> <li>the 74HXX series</li> <li>device have over</li> <li>standard TTL?</li> <li>The CMOS series that</li> <li>is pin compatible with</li> <li>the TTL family is the</li> <li>) The propagation</li> <li>delay of standard TTL</li> </ul> | 0.1V<br>reduced<br>propagation<br>delay .<br>74C00<br>series. | 0.7V<br>higher<br>propagation<br>delay<br>4000 series.   | 1.0V .<br>low<br>power<br>consumpti<br>on<br>5400<br>series.<br>4 nsec. | valid<br>lower<br>voltage<br>requirement<br>s<br>7400 series | <ul><li>1.0V .</li><li>reduced</li><li>propagation</li><li>delay .</li><li>74C00</li><li>series.</li></ul> |

| gates is approximately<br>) Which alteration is<br>made in the manufacture<br>of a TTL gate to create                                                                                                                                                                                                                   | 2 μsec<br>The output<br>transistors are<br>replaced by        | 10 nsec .<br>The input<br>transistor is<br>replaced by a | The<br>output<br>transistors                                            | 1 μsec<br>The top<br>output<br>transistor is                 | 10 nsec .<br>The top<br>output<br>transistor is                                                            |

| an open- collector     | diodes.      | diode.      | are       | missing   | missing      |

|------------------------|--------------|-------------|-----------|-----------|--------------|

| output?                |              |             | missing.  |           |              |

| ) One advantage that   | reduced      | higher      | high      |           |              |

| MOSFET transistors     | propagation  | switching   | input     |           |              |

| have over bipolar      | delay.       | speed.      | impedance | low input | high input   |

| transistors is         | -            | -           | •         | impedance | impedance.   |

| The original CMOS line | 5400 series. | 4000 series | 74C00     | 74HCOO    | 4000 series. |

| of circuits is the     |              |             | series    | series.   |              |

| Questions                                                                                                              | opt1                                       | opt2                                     | opt3                                                   | opt4                                 | opt<br>5 | opt<br>6 | Answer                                            |

|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------------------------------------------|--------------------------------------------------------|--------------------------------------|----------|----------|---------------------------------------------------|

| new generation<br>ofa<br>re emerging that<br>could add<br>flexibility and<br>investment<br>protection for<br>networks. | FPGA<br>Applicatio                         | programm<br>able<br>ASICs<br>Applicati   | ASIC                                                   | logic<br>cell<br>Applicat            |          |          | programma<br>ble ASICs                            |

| ASIC stands<br>for<br>FPGAs may be                                                                                     | n-<br>specified<br>integrated<br>circuit   | on-<br>specific<br>integrated<br>circuit | Application<br>-specific<br>intermodul<br>ated circuit | ion-<br>specific<br>inter<br>circuit |          |          | Application<br>-specific<br>integrated<br>circuit |