2018-2019

**Semester-III**

#### 18BEEC302

#### **ELECTRONIC DEVICES**

3H-

**3C**

Instruction Hours/week: L:3 T:1 P:0 Marks: Internal:40 External:60

Total:100

**End Semester Exam:**3 Hours

#### **Course Objectives**

To expose the students about the construction working and applications of basic electronic devices essential for subsequent courses on

- Analog electronics

- Analog & digital communication and

- CMOS design.

#### Course outcomes

At the end of this course students will demonstrate the ability to

- Understand the principle of semiconductor physics

- Understand and utilize the mathematical models of semiconductor junctions and MOS transistors for circuits and systems.

- Understand the fabrication process of integrated circuits.

#### UNIT I INTRODUCTION TO SEMICONDUCTOR PHYSICS

Review of Quantum Mechanics, Electrons in periodic Lattices, E-k diagrams. Energy bands in intrinsic and extrinsic silicon; Carrier transport: diffusion current, drift current, mobility and resistivity; sheet resistance, design of resistors

#### UNIT II SEMICONDUCTOR DIODES

Generation and recombination of carriers; Poisson and continuity equation P-N junction characteristics, I-V characteristics, and small signal switching models; Avalanche breakdown, Zener diode, Schottky diode, LED, photodiode and solar cell

#### UNIT III BIPOLAR TRANSISTORS

Bipolar Junction Transistor- Construction – working, I-V characteristics, transistor configurations and input- output characteristics, Early effect (base width modulation) – Ebers-Moll Model, transistor as an amplifier –Transistor as a switch.

#### UNIT IV FIELD EFFECT TRANSISTORS

Field-Effect Transistors: construction, working and VI characteristics of JFET, MOSFET – enhancement MOSFET, depletion MOSFET, their working principle and VI characteristics, MOS capacitor, C-V characteristics, and small signal models of MOS transistor.

#### UNIT V IC FABRICATION

Integrated circuit fabrication process: oxidation, diffusion, ion implantation, photolithography,

etching, chemical vapor deposition, sputtering, twin-tub CMOS process.

#### **Suggested Readings**

- 1. G. Streetman, and S. K. Banerjee, "Solid State Electronic Devices," 7th edition, Pearson, 2014.

- 2. D. Neamen, D. Biswas "Semiconductor Physics and Devices," McGraw-Hill Education 2003.

- 3. S. M. Sze and K. N. Kwok, "Physics of Semiconductor Devices," 3rd edition, John Wiley &Sons, 2006.

- 4. C.T. Sah, "Fundamentals of solid state electronics," World Scientific Publishing Co. Inc, 1991.

- 5. Y. Tsividis and M. Colin, "Operation and Modeling of the MOS Transistor," Oxford Univ.Press,2010.

- 6. Salivahanan Electronic Devices and circuits Tata McGraw-Hill publishing company 2007

**FACULTY IN-CHARGE**

**HOD / ECE**

# KARPAGAM ACADEMY OF HIGHER EDUCATION COIMBATORE-21.

## Faculty of Engineering Department of Electronics and Communication Engineering

#### **LECTURE PLAN**

NAME OF THE STAFF: G.R. MAHENDRA BABU

**DESIGNATION** : ASSISTANT PROFESSOR

CLASS : B.E-II YEAR ECE

SUBJECT : ELECTRONIC DEVICES

SUBJECT CODE : 18BEEC302

| S.No.                                                                   | TOPICS TO BE COVERED                        | TIME       | TEACHING AIDS                 |  |  |

|-------------------------------------------------------------------------|---------------------------------------------|------------|-------------------------------|--|--|

|                                                                         |                                             | DURATION   |                               |  |  |

| UNIT-I SEMICONDUCTOR DIODES AND SPECIAL PURPOSE DIODES                  |                                             |            |                               |  |  |

| 1                                                                       | Introduction                                | 3          |                               |  |  |

| 2                                                                       | Formation of PN junction – working          | 1          | T1-Pg.No: 42-46, 56, 85       |  |  |

|                                                                         | principle                                   |            |                               |  |  |

| 3                                                                       | VI characteristics – PN diode currents      | 1          | T1-Pg.No:93,60-65             |  |  |

| 4                                                                       | diode current equation                      | 1          | T1-Pg.No: 86-87, 100-         |  |  |

|                                                                         |                                             |            | 101                           |  |  |

| 5                                                                       | Diode resistance – transition and diffusion | 1          | T1-Pg.No:102-104              |  |  |

|                                                                         | capacitance                                 |            |                               |  |  |

| 6                                                                       | Tutorial                                    | 1          |                               |  |  |

| 7                                                                       | diode models – voltage breakdown in         | 1          | T1-Pg.No: 113-117,120-        |  |  |

|                                                                         | diodes.                                     |            | 128                           |  |  |

| 8                                                                       | Special purpose diodes : Zener diode-       | 1          | T1-Pg.No:130-141,143-         |  |  |

| 0                                                                       | point-contact diode                         | 1          | 146                           |  |  |

| 9                                                                       | backward diode- varactor diode              | 1          | T1-Pg.No:143-146,163-         |  |  |

| 10                                                                      |                                             | 1          | 164                           |  |  |

| 10                                                                      | step- recover y diode- schottky diode,      | 1          | T1-Pg.No:137, R3-             |  |  |

| 11                                                                      | PNPN diode – RF diode                       | 1          | Pg.No:105<br>T1-Pg.No:164-170 |  |  |

| 12                                                                      |                                             | 1          | 11-Pg.N0:104-170              |  |  |

| 12                                                                      |                                             | Tutorial 1 |                               |  |  |

| Total (Theory + Tutorial)   14 Hrs (12+2) UNIT II   BIPOLAR TRANSISTORS |                                             |            |                               |  |  |

| 1                                                                       |                                             | 1          |                               |  |  |

| 1                                                                       | Bipolar Transistors: Construction – working | 1          | T1-Pg.No:255-256,259-<br>261  |  |  |

| 2                                                                       |                                             | 1          | T1-Pg.No:257-259,261-         |  |  |

| Z                                                                       | transistor currents                         | 1          | 262                           |  |  |

| 3                                                                       | transistor configurations and input- output | 2          | T1-Pg.No:264-268,274          |  |  |

| 3                                                                       | characteristics                             | 2          | 11-1 g.110.204-200,274        |  |  |

| 4                                                                       | Early effect (base width modulation)        | 1          | T1-Pg.No:265                  |  |  |

| 5                                                                       | Tutorial                                    | 1          | <u> </u>                      |  |  |

| 6                                                                       | Ebers Moll model                            | 1          | T1-Pg.No:262,277              |  |  |

| 7                                                                       | transistor as an amplifier                  | 1          | T1-Pg.No:259                  |  |  |

| 8                                                                       | Transistor as a switch.                     | 1          | T1-Pg.No:293-298              |  |  |

|                                                                         |                                             |            |                               |  |  |

| 9  | Transistor applications                                                                              | 1            |                         |  |  |

|----|------------------------------------------------------------------------------------------------------|--------------|-------------------------|--|--|

| 10 | Tutorial                                                                                             | 1            |                         |  |  |

|    | Total (Theory + Tutorial)                                                                            | 11 Hrs (9+2) |                         |  |  |

|    | UNIT III FIELD EFFECT                                                                                | TRANSISTO    | RS                      |  |  |

| 1  | Field-Effect Transistors: construction, working and VI characteristics of JFET                       | 2            | T1-Pg.No:462-469        |  |  |

| 2  | comparison of BJT and JFET                                                                           | 1            | W1,W2                   |  |  |

| 3  | MOSFET – enhancement MOSFET,<br>depletion MOSFET, their working<br>principle and VI characteristics, | 2            | T1-Pg.No:472-475        |  |  |

| 4  | Tutorial                                                                                             | 1            |                         |  |  |

| 5  | comparison of MOSFET with JFET                                                                       | 1            | W3,W4                   |  |  |

| 6  | Comparison of D-MOSFET with E MOSFET                                                                 | 1            | W5                      |  |  |

| 7  | CMOS, MESFET                                                                                         | 1            | W6,W7                   |  |  |

| 8  | CCD.                                                                                                 | 1            | w8                      |  |  |

| 9  | Tutorial                                                                                             | 1            |                         |  |  |

|    | Total (Theory + Tutorial)                                                                            | 11 Hrs (9+2) |                         |  |  |

|    | UNIT IV DC POWE                                                                                      | R SUPPLIES   |                         |  |  |

| 1  | Rectifiers and Filters: Block schematic of a typical DC power supply                                 | 1            |                         |  |  |

| 2  | Single phase HWR, FWR, full- wave bridge rectifier                                                   | 1            |                         |  |  |

| 3  | Power supply filters (ripple factor and efficiency analysis)                                         | 1            |                         |  |  |

| 4  | Bleeder resistor, voltage dividers                                                                   | 1            |                         |  |  |

| 5  | Voltage regulators: voltage regulation,                                                              | 1            | S.Salivahanan, N Suresh |  |  |

| 6  | Tutorial                                                                                             | 1            | Kumar, "Electronic      |  |  |

| 7  | Zener diode shunt regulator, transistor series regulator                                             | 1            | Devices and Circuits"   |  |  |

| 8  | Transistor shunt regulator                                                                           | 1            |                         |  |  |

| 9  | Switching regulators                                                                                 | 1            |                         |  |  |

| 10 | Design of complete DC power supply circuit                                                           | 1            |                         |  |  |

| 11 | Tutorial                                                                                             | 1            |                         |  |  |

|    | Total (Theory + Tutorial)                                                                            | 11 Hrs (9+2) |                         |  |  |

|    |                                                                                                      |              |                         |  |  |

|    | UNIT V INTEGRATED CIRC                                                                               | 1            |                         |  |  |

| 1  | Integrated circuit – advantages and drawback of ICs                                                  | 1            | R7-Pg.No:1              |  |  |

| 2  | Scale of integration –classification of ICs                                                          | 1            | R7-Pg.No:2-3            |  |  |

| 3  | Definition of linear IC and digital IC with examples                                                 | 2            | R7-Pg.No:1-2            |  |  |

| 4  | manufacturing process of monolithic ICs                                                              | 2            | T1-Pg.No:500-508        |  |  |

| 5  | Tutorial                                                                                             | 1            |                         |  |  |

| 6  | Fabrication of components (diode, capacitor, bipolar transistor and                                  | 2            | T1-Pg.No:509-517        |  |  |

| 7  | resistor) on monolithic IC                                                                           | 4            |                         |  |  |

| 7  | Comparison of MOS ICs and bipolar ICs.                                                               | 1            |                         |  |  |

| 8 | Tutorial                  | 1            |  |

|---|---------------------------|--------------|--|

|   | Total (Theory + Tutorial) | 11 Hrs (9+2) |  |

**Total Lecture: 58 Hours (48+10)**

#### **TEXT BOOKS:**

| S.NO | Author(s) Name      | Title of the book                              | Publisher                            | Year of publication |

|------|---------------------|------------------------------------------------|--------------------------------------|---------------------|

| 1    | Millman and Halkias | Electronic devices and Circuits                | Tata McGraw<br>Hill<br>International | 2010                |

| 2    | David A.Bell        | Fundamental of electronic devices and circuits | Oxford press                         | 2009                |

#### **REFERENCES:**

| NEI ENEI (CES) |                                              |                                                                  |                                          |                     |  |

|----------------|----------------------------------------------|------------------------------------------------------------------|------------------------------------------|---------------------|--|

| S.NO.          | Author(s) Name                               | Title of the book                                                | Publisher                                | Year of publication |  |

| 1              | Street Man                                   | Solid State Electronic<br>Devices'                               | Prentice Hall<br>Of India,6th<br>edition | 2005                |  |

| 2              | Mathur Kulshrestha and<br>Chadha             | Electron devices and<br>Applications and<br>Integrated circuits' | Umesh<br>Publications                    | 2005                |  |

| 3              | Thomas L. Flo yd                             | Electron Devices                                                 | Charles and<br>Messil<br>Publications    | 2012                |  |

| 4              | G.K.Mithal                                   | Electronic Devices and Circuits                                  | Khanna<br>Publishers                     | 2013                |  |

| 5              | Robert L. Bo ylestad and<br>Louis Nashelsk y | Electronic Devices and<br>Circuit Theor y                        | Pearson<br>Education, 9th<br>Edition,    | 2009.               |  |

| 6              | B. Somanathan Nair                           | Electronic Devices and Applications                              | PHI,                                     | 2006                |  |

#### **ADDITIONAL REFERENCES:**

| 7. | D.roy Choudhury, | Linear Integrated      | New Age        | 2010 |

|----|------------------|------------------------|----------------|------|

|    | Shail B.jain     | Circuits               | International  |      |

|    |                  |                        | Limited        |      |

| 8. | S.Salivahanan    | Electronic Devices and | Tata Mcgraw    | 2012 |

|    | N Suresh Kumar   | Circuits               | Hill Education |      |

|    |                  |                        | Private        |      |

|    |                  |                        | Limited        |      |

#### Websites:

- 1. http://www.rfwireless-world.com/Terminology/BJT-vs-FET.html

- 2. <a href="http://swissen.in/JFETvsBJT.php">http://swissen.in/JFETvsBJT.php</a>

- 3. <a href="http://www.circuitstoday.com/jfet-and-mosfet-comparison">http://www.circuitstoday.com/jfet-and-mosfet-comparison</a>

- 4. <a href="http://www.electricalbasicprojects.com/mosfet-vs-jfet-comparison/">http://www.electricalbasicprojects.com/mosfet-vs-jfet-comparison/</a>

- 5. <a href="http://www.rfwireless-world.com/Terminology/Depletion-MOSFET-vs-Enhancement-MOSFET.html">http://www.rfwireless-world.com/Terminology/Depletion-MOSFET-vs-Enhancement-MOSFET.html</a>.

- 6. https://en.wikipedia.org/wiki/CMOS

- 7. <a href="http://www.radio-electronics.com/info/data/semicond/fet-field-effect-transistor/gaasfet-mesfet-basics.php">http://www.radio-electronics.com/info/data/semicond/fet-field-effect-transistor/gaasfet-mesfet-basics.php</a>

- 8. <a href="https://www.elprocus.com/know-about-the-working-principle-of-charge-coupled-device/">https://www.elprocus.com/know-about-the-working-principle-of-charge-coupled-device/</a>

**FACULTY IN-CHARGE**

HOD/ECE

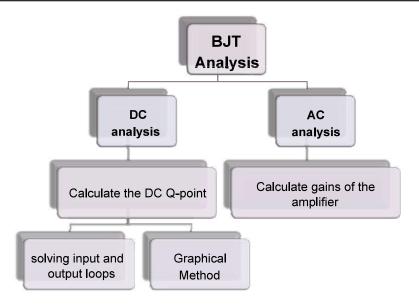

### **Introduction – Biasing**

The analysis or design of a transistor amplifier requires knowledge of both the dc and ac response of the system. In fact, the amplifier increases the strength of a weak signal by transferring the energy from the applied DC source to the weak input ac signal The analysis or design of any electronic amplifier therefore has two components:

The dc portion

and

• The ac

portion

During the design stage, the choice of parameters for the required dc levels will affect the ac response.

#### What is biasing circuit?

Biasing: Application of dc voltages to establish a fixed level of current and voltage.

#### Purpose of the DC biasing circuit

- To turn the device "ON"

- To place it in operation in the region of its characteristic where the device operates most linearly.

- Proper biasing circuit which it operate in linear region and circuit have centered Q-point or midpoint biased

- Improper biasing cause Improper biasing cause

- •, Distortion in the output signal

Important basic relationship

$$I_{E} = I_{B} + I_{B}$$

$$\beta = I^{C}$$

$$\beta = I^{C}$$

$$I = (\beta + 1)I \cong I$$

$$V = V \quad C$$

$$CE - V^{BE}$$

# **Operating Point**

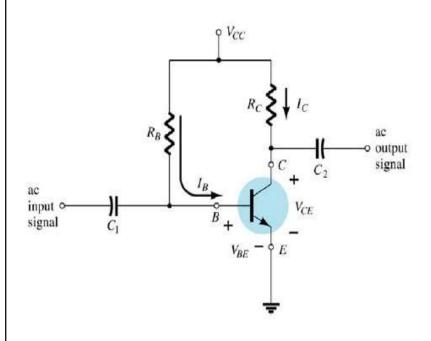

### **DC Biasing Circuits**

- •Fixed-bias circuit

- •Emitter-stabilized bias circuit

- •Collector-emitter loop

- •Voltage divider bias circuit

- •DC bias with voltage feedback

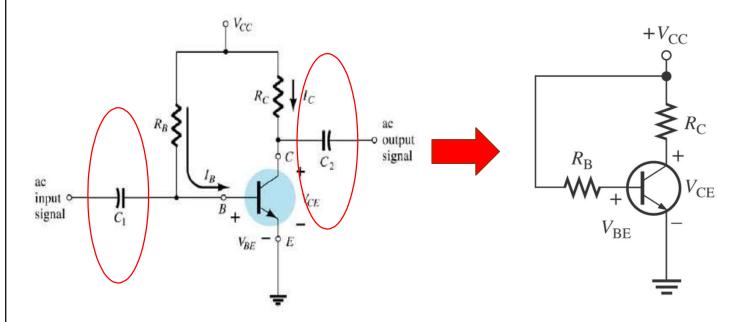

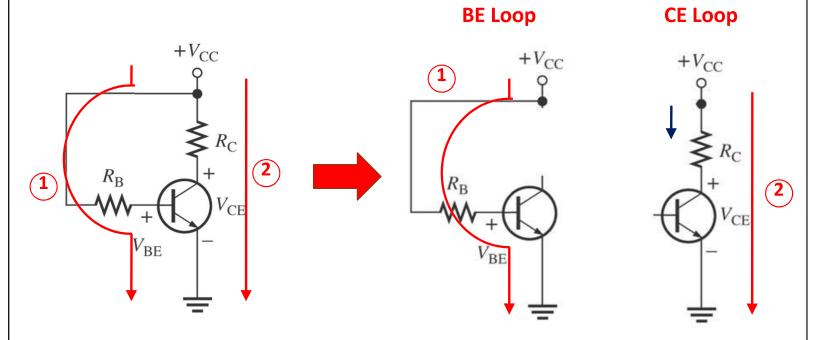

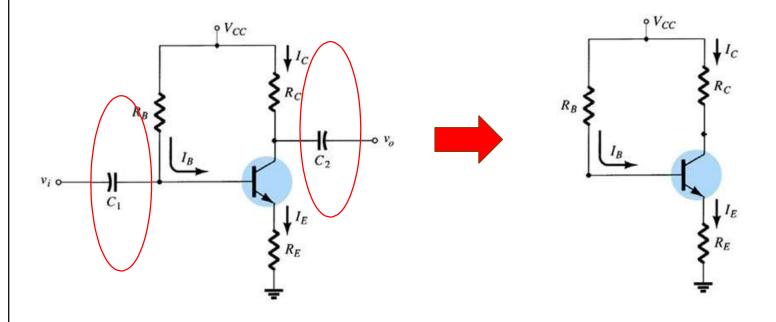

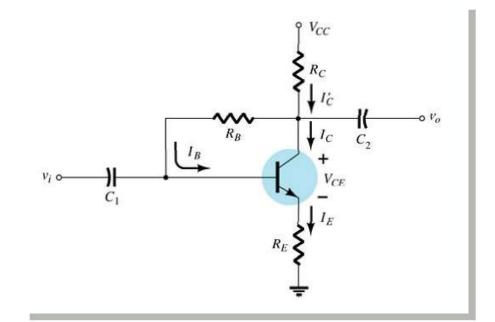

- This is common emitter (CE) configuration

- 1<sup>st</sup>step: Locate capacitors replace them with an open and circuit

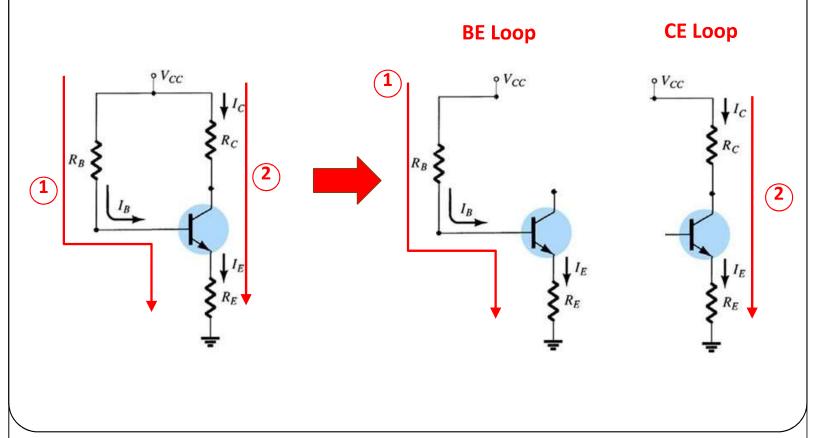

- 2<sup>nd</sup>/<sub>m</sub>step: Locate 2 main loops

- ☐ BE loop (input loop)

- ☐ CE loop(output loop)

•  $1_{st}$  step: Locate capacitors and replace them with an operfult

• 2<sub>nd</sub> step: Locate 2 main loops.

BE Loop

From KVL;

$$\begin{array}{c} - \quad CC + I_B R_B + V_{BE} = 0 \\ V \quad V_{CC} - V_{BE} \\ \vdots \quad I_B = R \end{array}$$

CE Loop

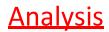

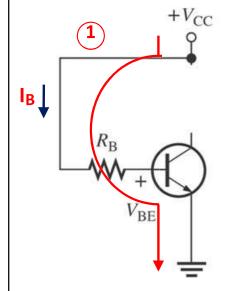

### **Analysis**

From KVL;

$$-V + I R + V = 0$$

$$V^{CC} = V^{C} - I R$$

As we known;  $C^{C}$

$$I = \beta I$$

$I = \beta I$ Substituting A with B

$$I_{C} = \beta_{DC} \left( \frac{V_{CC}}{R_{B}} \right)$$

Note that  $\stackrel{R}{ }_{ }$  does not affect the value of Ic

#### DISADVANTAGE

☐ Unstable – because it is too dependent on and produce

β ក្រុក្ស ក្រុម ្នាស្ស ក្រុម ក្រុម

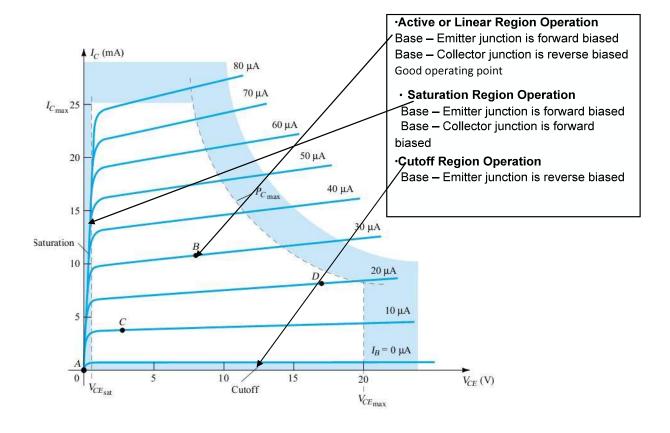

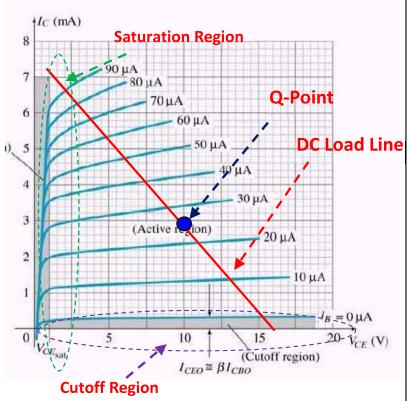

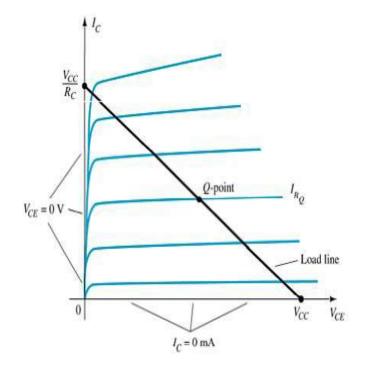

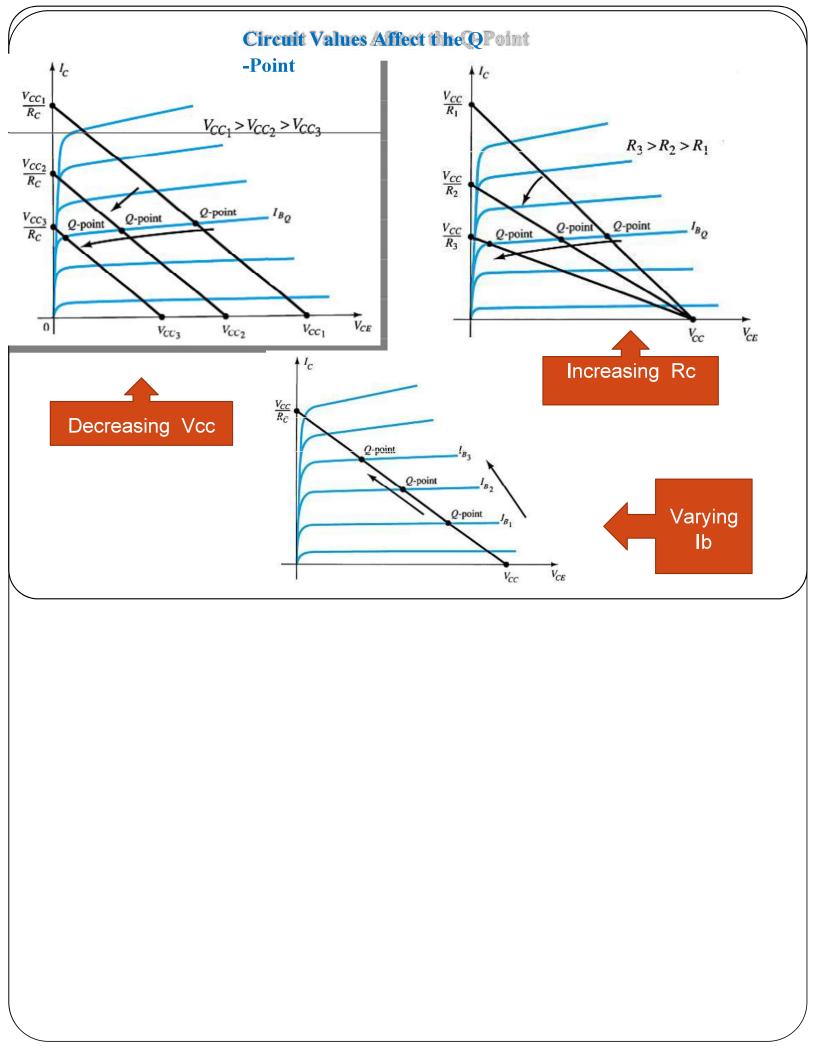

# **Load line analysis**

A fixed bias circuit with given and Sect (Markers, d Recan be determining the values of Iba, Ica and Vcea) using the concept of load line also.

Here the input loop KVL equation is not used for the purpose of analysis, instead, the output characteristics of the transistor used in the given circuit and output loop

KVL equation are made use

of.

#### ☐ Plot load line equation

$$I_{C_{sat}} = \left. egin{array}{c} V \ R_{C} \end{array}

ight|_{V_{c}=0}$$

$\square V_{CE(off)}$  occurs when transistor operating in *cut-off region*

$$V_{CE_{(off)}} = V_{CC} - I_C R_C \Big|_{I_{c}=0}$$

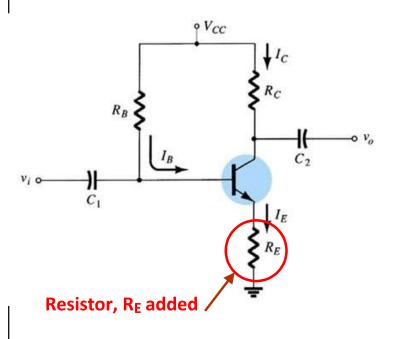

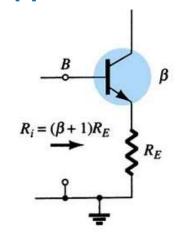

- An emitter resistor, R is added to improve stability

- 1<sup>st</sup> step: Locate capacitors replace them with an open and rouit

- 2<sup>nd</sup> step: Locate 2 main loops

- BE loop

- CE loop

•  $1_{st}$  step: Locate capacitors and replace them with an operfult

• 2<sub>nd</sub> step: Locate 2 main loops.

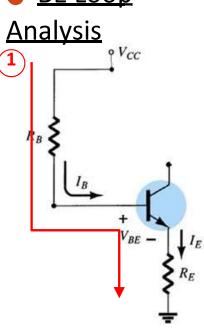

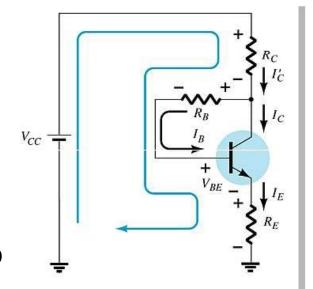

### BE Loop

#### From kvl;

$$-V_{CC} + I_{B}R_{B} + (\beta + 1)I_{B}R =$$

$$+V_{CC} - V_{D} =$$

$$\therefore I_{B} = \frac{V_{CC} - V_{BE}}{R_{B} + (\beta + 1)R_{E}} =$$

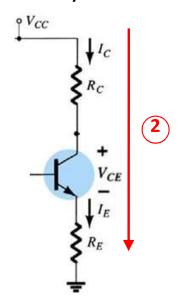

CE Loop

### <u>Analysis</u>

From KVL;

$$\blacksquare \stackrel{\therefore V}{\subset} = V - I (R + R)$$

$$CE = CC - C C E$$

### Improved Bias Stability

The addition of the emitter resistor to the dc bias of the BJT provides improved stability, that is, the dc bias currents and voltages remain closer to where they were set by the circuit when outside conditions, such as temperature, and transistor beta, change.

#### Without Re

$$I_{c} = \left(\frac{V_{BE}}{CC_{R_{B}}}\right) \beta$$

#### With Re

$$I_{c} = \left(\frac{V_{CC}}{R_{B}}\right)\beta$$

$$I_{c} = \left(\frac{V_{CC}}{R_{B}}\right)\beta$$

$$1)R$$

Note: it seems that beta in numerator canceled with beta in denominator

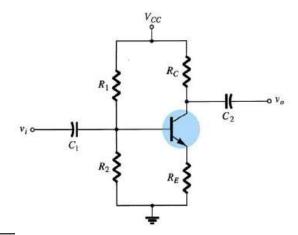

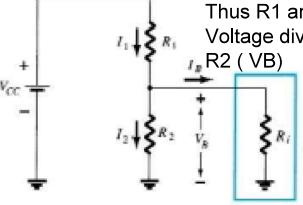

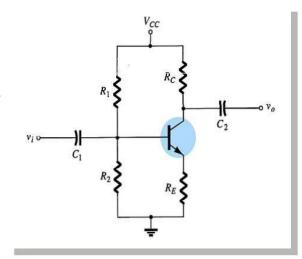

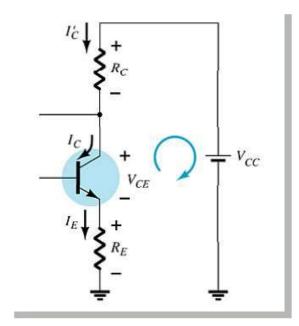

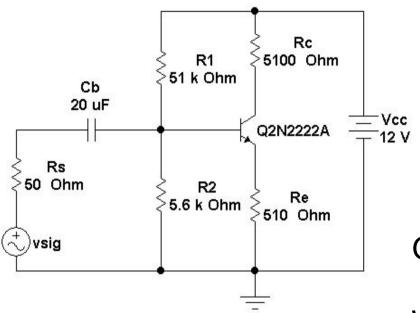

### **VOLTAGE DIVIDER BIAS CIRCUIT**

- Provides good Q-point stability with a single polarity supply voltage

- This is the biasing circuit wherein, ICQ and VCEQ are almost independent of beta.

- P Voe texaboft Remidde heartheith patie act a air you integration of values of the Atand

- Two Approximate method: direct method, saves time and energy, 1st step: Locate capacitors and replace them with an open

- **h**ஞ்**gste**p: Locate 2 main loops whic்ந் loop

- CE loop

# VOLTAGE DIVIDER

# **BIAS CIRCUIT**

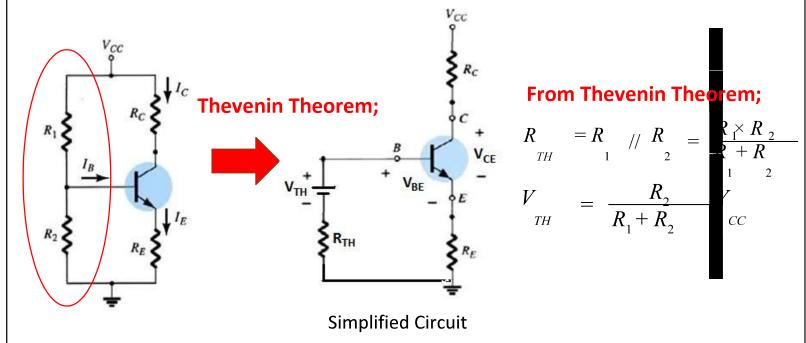

#### **Thevenin Theorem**

2<sup>nd</sup> step: : Simplified circuit using

# **VOLTAGE**

# **BIAS CIRCUIT**

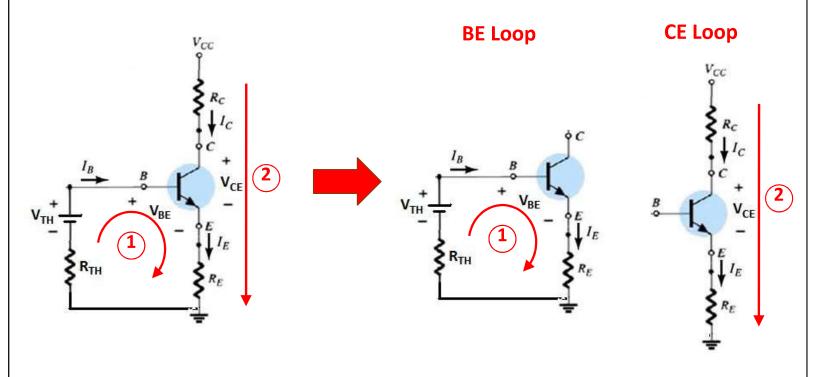

• 2<sub>nd</sub> step. Locate 2 main loops.

# VOLTAGE DIVIDER BIAS CIRCUIT

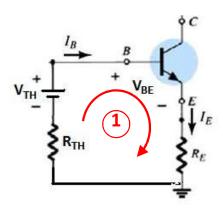

BE Loop

**Analysis**

From KVL;

# **VOLTAGE DIVIDER BIAS**

### **CIRCUIT**

CE Loop

<u>Analysis</u>

■ From KVL;

$$-V_{CC} + I_{C}R_{C} + V_{CE} + I_{E}R_{E} = 0$$

Assume;

Therefore;

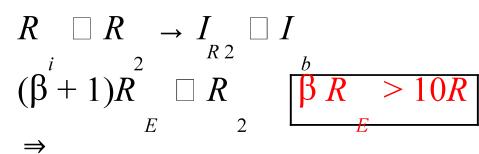

### **Approximate analysis:**

- ☐ If this condition applied then you can use approximation method.

- ☐ This makes IB to be negligible. Thus I1 through R1 is almost same as the current I2 through R2.

Thus R1 and R2 can be considered as in series.

Voltage divider can be applied to find the voltage across

# **Approximate Analysis**

When

$$\beta R > 10R$$

, Then  $I \ll I$  and  $I \cong I$ :

$$\mathbf{V_B} = \frac{\mathbf{R}}{\mathbf{V_1}} \underbrace{\mathbf{V}}_{\mathbf{CC}} \qquad \mathbf{V} = \mathbf{V} - \mathbf{V}$$

$$\underline{\mathbf{V}}$$

$$\mathbf{V} = \mathbf{V} - \mathbf{V}$$

$\mathbf{E} = \mathbf{B} - \mathbf{B}$

$$I_E = \frac{\underline{\mathbf{V}}}{R_E^E}$$

#### From Kirchhoff's voltage law:

$$V = V - IR - IR$$

$$CE \quad CC \quad C \quad C \quad E$$

$$I \cong I \quad E$$

$$V = V - I(R + R)$$

$$CE \quad CC \quad C \quad C \quad E$$

This is a very stable bias circuit. The currents and voltages are nearly independent of any variations in  $\beta$ .

# DC Bias with Voltage Feedback

Another way to improve the stability of a bias circuit is to add a feedback path from collector to base.

In this bias circuit the Q-point is only slightly dependent on the transistor beta,  $\beta$ .

# **Base-Emitter Loop**

#### From Kirchhoff's voltage law:

Where  $I_R \ll I_C$ : C

Knowing  $I_C \equiv \beta I_B$  and  $I_C \equiv I_B$  the loop

equation becomes:

**Solving for I**:

$$I_{B} = \frac{V}{R} + \frac{V}{P} \left(R + \frac{BF}{R}\right)$$

# **Collector-Emitter Loop**

#### Applying Kirchoff's voltage law:

$$I + V + I' R - V = 0$$

$$E \quad CE \quad C \quad C$$

Since

$$I' \stackrel{\cong}{=} I \quad and \quad I = \beta I :$$

$$I \quad (R + ) + V - V = 0$$

$$C \quad C \quad RE \quad CE \quad CC$$

Solving for

$$V :$$

$$CE \quad CC \quad C \quad C \quad E$$

\c\_vl,....\_,."\ "i. • 12,ifo\ c,.,( 0 c, ~ ,f *Pro'b\e.w-* i,ve\_ 11 c e\_d f {01 o < -J + wtool e: Cl<;o $\v$ d y (6t fex: coot LdYly) le..- $_{1,1^{\sim}}$  , f  $_{\text{t}\sim\text{e}}$  yVtq1,h  $_{at7e/<ll'o'V}$  is ncl\,  $dbv''t^{\circ}ctUS$  - S "1<:lk3" J- ~5Juvt1  $U_{\overline{c}}fh_{1}v_{t}$  +~c.. t•ctll\s,st-c,y' YJ,'° e.  $f_{cYt}$ ,  $J_{ar-e:I}$ ,  $f_{cYt}$ ,  $J_{ar-e:I}$ ,  $f_{cYt}$ ,  $J_{ar-e:I}$ ,  $f_{cYt}$ ,  $f_{ar-e:I}$ ,  $f_{cYt}$ ,  $Q_- \sim \stackrel{\text{t.d.}}{\sim} \stackrel{\text{J.}}{\sim} \stackrel{\text{J.}}$  $g_{\text{-}}$  ev-~ie..

e.  $r e s : \text{tt<~} <; \quad \text{--c: '} r \sim \text{si~to-,};$ ~C\.he. cIf  $f \sim C = \frac{(\circ vi + 1 + 1)^{C}}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi + 1 + 1)^{C}} = \frac{\circ Vi + 1}{(\circ vi$ °'- SJu (s &>vteGb. 1 \\~~ V\ ,'f , ~~ 1.}\1'k~ 4- It the initial assumption is proven incorrect then a new assumption must be made and the new circulis must be analyzed, Step3 must be then be repeated. بالمختصر ا فرها عنامات عن عنامات كا كدم مال الراجع عن الماجع عنه الماجع عنه الماجع عنه الماجع عنه الم العرضية وعيرطل.

```

, find a point , IL

V se ∹j ⊥

c: / {?.-::: lo o

~ ~''' ~\2-) 5~

5 \text{ k It} \sim \text{k}^{< 5 \text{ k}}

S

\downarrow, Y'

\mathsf{ti} \sim_0 - \mathsf{If} + \mathsf{s} : \mathsf{g} \cdot \mathsf{J} ) \quad \mathsf{r} ,

|<|k '\' (~ ,:

-t-l)Jk

1e. a_1 @1b a_2 ~uo a_3. a_4 ~ a_4 < JS a_5 a_4 ~ a_4 < JS

r~,r~ ci~ J

~ ({1+916+10 + VCE + 5k x IE -5=0

\JC. t ~ ( /~"$5 ~ 1 • k - 5 ~ , g '-1 J \ - :: I.f.

"lce;; l, q_{lc..}- l \sim \simc. s \simcc; -t '1 ~

\sim C- -S ,- , k J <sub>s: -/=/-'</sub>

= \frac{{}^{s} \cdot {}^{'} 1 \cdot c, r \cdot 3 \cdot {}^{6} \cdot D5}{{}^{C} fl5} \cdot 11 = \frac{3--C}{fl} \cdot {}^{s}, -=/!t.

$(<

```

O1: It VB=1, find Vc, B, a

T..., \( \cdots \), \( \cdots

4

*£*,~*le*: :=-, '4t= r, ,7~\Is - '\_+ s: '' \SJ M L  $r_{>1,...} = r_{>1,...} = r_{>1,1}$   $r_{>1,...} = r_{>1,...} = r_{>1,...}$ Ic = B Ib = 100 x ,026 x 103 = 2.6 m. '1c£~5- i.21"1·6-=- -,71 • ~c..c;< '1~~~ OU« C(JJvI"1'f;I'~ 1? .\_\_,./(~.  $\label{eq:continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous$  $\cdot_{\mathrm{c..}}$  e.r.  $\sim_{\scriptscriptstyle{I}} L$ " ~ , −, ²

• - t.o' -

$$q$$

. e/

f Q

M./1

Example find & posts, Vc, VE, VB assum V E:, -17 +10 - 10+,7 = ,093-,107 = -,014mA Ib = -,014mA > X wrong assumption The transistor is cut of by  $c = c \sim T[\sim V_{t} = 0]$  c = -10, c = -10, c = -10= /, ut Q /<7'1 Vcc = 10  $Gr_{liu}le_{fN}e$  a.u., ve. -\\l-+ -z."Tt -t\uokTb T1"t+lk.TEs- Tu == (? +~ Tb 1b-; Lo-,1- ,0i..l,,,. ,4  $1 < J_{Q} k$ . "t  $(\sim -t \sim \{k + \})$ ' T - fl | z: ~ · M A . **t**::: ; b'2..31' w. .A ~CE:. lo - 1.J ~ > Vce (506) لافظ هذه للائرة مستقيل التهير التهير التهير إ:\.? ~y j~ ~ c,

-

$$1u^{\text{"""}}$$

lck  $1b + 2u \text{?} A + \sim 1b$ ) -+  $1_{\text{(Jo)}}$  k (Ti.""  $\sim 17 = 0$ )  $\circ$

JIC

$$< 5$$

$< 5$   $< 5$   $< 5$   $< 5$   $< 5$   $< 5$   $< 5$   $< 5$   $< 5$   $< 5$   $< 5$   $< 5$   $< 5$   $< 5$   $< 5$   $< 5$   $< 5$   $< 5$   $< 5$   $< 5$   $< 5$   $< 5$   $< 5$   $< 5$   $< 5$   $< 5$   $< 5$   $< 5$   $< 5$   $< 5$   $< 5$   $< 5$   $< 5$   $< 5$   $< 5$   $< 5$   $< 5$   $< 5$   $< 5$   $< 5$   $< 5$   $< 5$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$   $< 7$

lo u

Example: find Q

```

-\() -t ~Jb -Γ.) \III. -\- -,:1 + (βτι) Ib *\k=0

T2.J\.Huk f

... 11. I'c,1- ~@

.:\sim .==''eJ_{\Gamma}, \quad \text{for } f?J [

- b_k \sim \{ \cdot , f_{ij} \in (\sim \cdot_{r} ) 1 \text{ b } \text{ ic } y\{L \} \}

-\u \frac{\lambda}{\sigma} \sigma \frac{\lambda}{\sigma} \frac{\lambda}{\sigma} \frac{\lambda}{\lambda} \frac{\lambda}{\lambd

16 · s / S M ~

Ii \int_{10}^{S} \log^{111} A 1 11- 10|Cf w.

SI')(

's1.

```

$E\sim te;$  ttv1 Q ~ J>u. ct Iph>.~ tS *²:*--*v*A~*e* u....-e CAccv..\\: .; ~e..vl<- ~*V\:Je,r* **°-ff{'''**  $\sim \ 'c/V \$ 330  $y3\tilde{q}_{f}^{c;} > 1$ c'  $S c/\sim 100 \text{ K} \sim d$  °'-(f I( $\sim$  L'QV) wh.~\_:\'-',Q J $\sim$ . '{ (o ''''  $\setminus S$ ,  $(y \stackrel{r:}{\stackrel{--}{-}} 8, 1 \stackrel{\circ}{\circ}$ ~ 'o\: z: "1500 '1. f.:: ',\/, -, 1 i ·\\ VCE = 1/5 - 2 m (lok + 4,05 h) = -13.14 : -> our assumption is wrong the transistor is saburation -> Resolve -- \lc.<;.(5-v\) s l(.. O' "1 ~~) ~ o R C.E. C::..t 5~

(10

Example: (PNP).

UeG--k

$f_{\text{f.'t}}$  cat  $\cdot$  q, S"  $\times$  Z/.<. / L o

'idk s g

VE 5 8.7

Jes 10.7-8.7 5 1m

106 = 6.7 - 8 kx/m = 4.7 > VCE (sab).

" lok

#### ANALOG CIRCUITS

Presented By,

G.R.Mahendra Babu,

Assistant Professor,

Dept of ECE/ FoE/ KAHE.

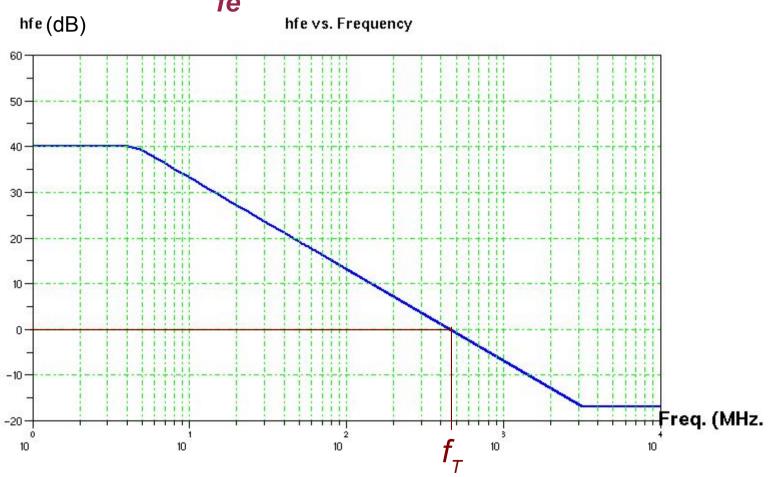

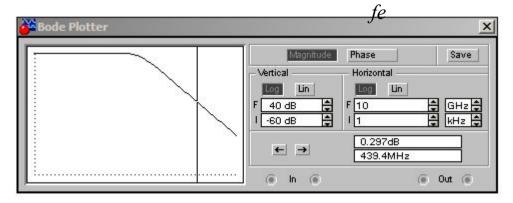

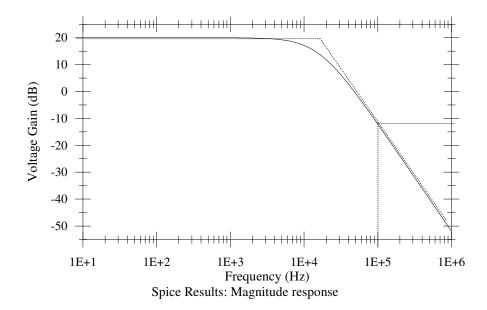

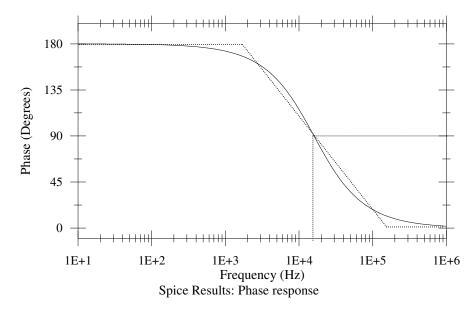

## High Frequency BJT Model

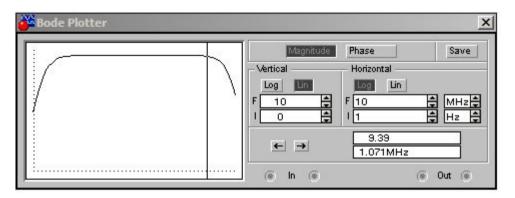

## Gain of 10 Amplifier – Non-ideal Transistor

Gain starts dropping at about 1MHz.

Why!

Because of internal transistor capacitances that we have ignored in our models.

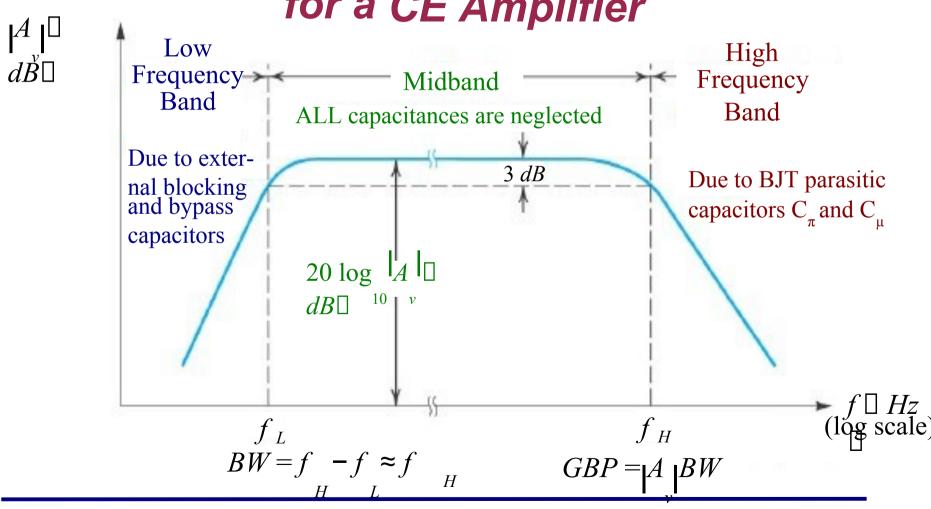

Sketch of Typical Voltage Gain Response for a CE Amplifier

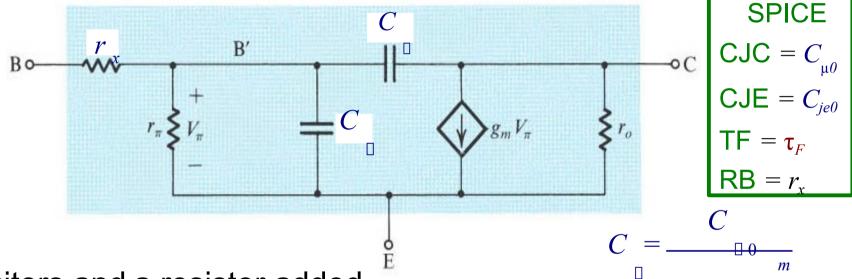

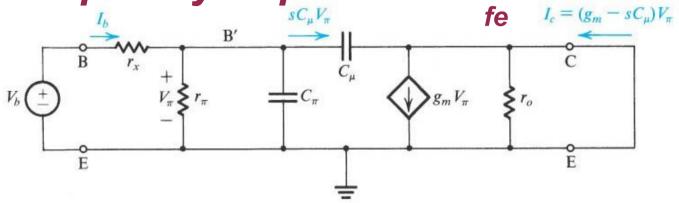

## High Frequency Small-signal Model

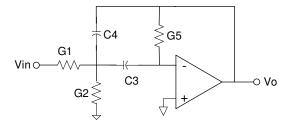

Two capacitors and a resistor added. A base to emitter capacitor, *C*

A base to collector capacitor,  $C_{\mu}$  A resistor, r, representing the base terminal resistance (r << r)

$$C = C \xrightarrow{je \cdot 0} \stackrel{0c}{\approx} C \qquad \square 2 C \xrightarrow{je \cdot 0}$$

$$\square 1 - \frac{V_{BE}}{V_{0e}} \qquad C = \square g$$

$$de \qquad F$$

$\tau_{E}$  = forward-base transit time

## High Frequency Small-signal Model

The internal capacitors on the transistor have a strong effect on circuit high frequency performance! They attenuate base signals, decreasing v since their reactance approaches zero (short circuit) as frequency increases.

As we will see later C is the principal cause of this gain loss at high frequencies. At the base  $C_{\mu}$  looks like a capacitor of value k  $C_{\mu}$  connected between base and emitter, where k > 1 and may be >> 1.

This phenomenon is called the *Miller Effect*.

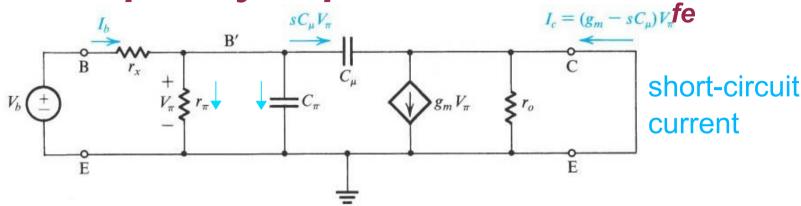

## Frequency-dependent "beta" h

@ node B':  $\int_{c}^{c} \frac{1}{r_0} \, ds \, C_0 \, ds$  where  $r_x \approx 0$  (ignore  $r_x$ )  $NOTE: s = \int_{c}^{c} + j\omega, \text{ in sinusoidal steady-state } s = j\omega.$

Frequency-dependent h or "beta"  $fe^{SC_{\mu}V_{\pi}}$  or  $fe^{I_{c}=(g_{m}-sC_{\mu})V_{\pi}}$

$$h = \frac{I}{\Leftarrow} \quad \frac{g - \overset{b}{S}C}{m} \quad \Box$$

$$fe \quad I_b \quad \frac{1}{r} \quad \Box \quad S \quad C_{\Box} \Box \quad S \quad C_{\Box}$$

## Frequency Response of h

$$h = \frac{g_{m} - s C}{1} \quad | s C \quad | s C$$

$$\frac{1}{r} \quad | s C \quad | s C$$

$$multiply N&D by \quad | and set \quad s = j\omega$$

$$h_{fe} = \frac{\left[ g_{m} - j \quad | C \quad | \right]}{1 \quad | j \quad | \quad | C \quad | \quad |}$$

$$factor N \text{ to isolate } g_{m} \qquad C$$

$$h_{fe} = \frac{\left[ 1 - j \quad | g_{m} \quad | c \quad | \quad | \quad | \quad |}{1 \quad | \quad | \quad | \quad |} \right]$$

$$fe$$

$$g^{m} = \frac{L_{C}}{V} \qquad r = \square \qquad \frac{V_{T}}{I}$$

For small  $\square = \square : \square_{low} : \square_{c} \qquad \frac{C}{g} = \ll 1 \square \qquad \frac{1}{10}$

and:  $\square_{low} \square C \square C \square C \square r = \square_{low} : \square_{c} \qquad \frac{1}{10}$

Note:  $\square_{low} \square C \square C \square r = \square_{low} : \square_{c} \qquad \square_{c} \qquad$

$$h_{fe} = \frac{C}{g_{m}r_{0}} \xrightarrow{1-j} g_{m}r_{0}$$

$$1 \cap j \cap C \cap r_{0} = \frac{f}{g_{m}r_{0}} \xrightarrow{f_{0}} f_{0}$$

$$1 \cap j \cap C \cap r_{0} = \frac{f}{g_{m}r_{0}} \xrightarrow{f_{0}} f_{0}$$

$$1 \cap j \cap C \cap r_{0} = \frac{f}{g_{m}r_{0}} \xrightarrow{f_{0}} f_{0}$$

$$1 \cap j \cap C \cap r_{0} = \frac{f}{g_{m}r_{0}} \xrightarrow{f_{0}} f_{0}$$

$$1 \cap j \cap C \cap r_{0} = \frac{f}{g_{m}r_{0}} \xrightarrow{f_{0}} f_{0}$$

$$1 \cap j \cap C \cap r_{0} = \frac{f}{g_{m}r_{0}} \xrightarrow{f_{0}} f_{0}$$

$$1 \cap j \cap C \cap r_{0} = \frac{f}{g_{m}r_{0}} \xrightarrow{f_{0}} f_{0}$$

$$1 \cap j \cap C \cap r_{0} = \frac{f}{g_{m}r_{0}} \xrightarrow{f_{0}} f_{0}$$

$$1 \cap j \cap C \cap r_{0} = \frac{f}{g_{m}r_{0}} \xrightarrow{f_{0}} f_{0}$$

$$1 \cap j \cap C \cap r_{0} = \frac{f}{g_{m}r_{0}} \xrightarrow{f_{0}} f_{0}$$

$$1 \cap j \cap C \cap r_{0} = \frac{f}{g_{m}r_{0}} \xrightarrow{f_{0}} f_{0}$$

$$1 \cap j \cap C \cap r_{0} = \frac{f}{g_{m}r_{0}} \xrightarrow{f_{0}} f_{0}$$

$$1 \cap j \cap c \cap r_{0} = \frac{f}{g_{m}r_{0}} \xrightarrow{f_{0}} f_{0}$$

$$1 \cap j \cap c \cap r_{0} = \frac{f}{g_{m}r_{0}} \xrightarrow{f_{0}} f_{0}$$

$$1 \cap j \cap c \cap r_{0} = \frac{f}{g_{m}r_{0}} \xrightarrow{f_{0}} f_{0}$$

$$1 \cap j \cap c \cap r_{0} = \frac{f}{g_{m}r_{0}} \xrightarrow{f_{0}} f_{0}$$

$$1 \cap j \cap c \cap r_{0} = \frac{f}{g_{m}r_{0}} \xrightarrow{f_{0}} f_{0}$$

$$1 \cap j \cap c \cap r_{0} = \frac{f}{g_{m}r_{0}} \xrightarrow{f_{0}} f_{0}$$

$$1 \cap j \cap c \cap r_{0} = \frac{f}{g_{m}r_{0}} \xrightarrow{f_{0}} f_{0}$$

$$1 \cap j \cap c \cap r_{0} = \frac{f}{g_{m}r_{0}} \xrightarrow{f_{0}} f_{0}$$

$$1 \cap j \cap c \cap r_{0} = \frac{f}{g_{m}r_{0}} \xrightarrow{f_{0}} f_{0}$$

$$1 \cap j \cap c \cap r_{0} = \frac{f}{g_{m}r_{0}} \xrightarrow{f_{0}} f_{0}$$

$$1 \cap j \cap r_{0} = \frac{f}{g_{m}r_{0}} \xrightarrow{f_{0}} f_{0}$$

$$1 \cap j \cap r_{0} = \frac{f}{g_{m}r_{0}} \xrightarrow{f_{0}} f_{0}$$

$$1 \cap j \cap r_{0} = \frac{f}{g_{m}r_{0}} \xrightarrow{f_{0}} f_{0}$$

$$1 \cap j \cap r_{0} = \frac{f}{g_{m}r_{0}} \xrightarrow{f_{0}} f_{0}$$

$$1 \cap j \cap r_{0} = \frac{f}{g_{m}r_{0}} \xrightarrow{f_{0}} f_{0}$$

$$1 \cap j \cap r_{0} = \frac{f}{g_{m}r_{0}} \xrightarrow{f_{0}} f_{0}$$

$$1 \cap j \cap r_{0} = \frac{f}{g_{m}r_{0}} \xrightarrow{f_{0}} f_{0}$$

$$1 \cap j \cap r_{0} = \frac{f}{g_{m}r_{0}} \xrightarrow{f_{0}} f_{0}$$

$$1 \cap j \cap r_{0} = \frac{f}{g_{m}r_{0}} \xrightarrow{f_{0}} f_{0}$$

$$1 \cap j \cap r_{0} = \frac{f}{g_{m}r_{0}} \xrightarrow{f_{0}} f_{0}$$

$$1 \cap j \cap r_{0} = \frac{f}{g_{m}r_{0}} \xrightarrow{f_{0}} f_{0}$$

$$1 \cap j \cap r_{0} = \frac{f}{g_{m}r_{0}} \xrightarrow{f_{0}} f_{0}$$

$$1 \cap j \cap r_{0} = \frac{f}{g_{m}r_{0}} \xrightarrow{f_{0}} f_{0}$$

$$1 \cap j \cap r_{0} = \frac{f}{g_{m}r_{0}} \xrightarrow{f_{0}} f_{0}$$

$$1 \cap j \cap r_{0} = \frac{f}{g_{m}r_{0}} \xrightarrow{f_{0}} f_{0}$$

$$1 \cap j \cap r_{0} = \frac{f}{g_{m}r_{0}} \xrightarrow{f_{0}} f_{0}$$

$$1 \cap j \cap r_$$

Hence, the lower break frequency or -3dB frequency is  $f_{s}$

$$f_{\square} = \frac{1}{2 \square \square C^{\square} \square C$$

Using Bode plot concepts, for the range where:  $f \Box f \Box$

$$h_{f_e} = g_m r$$

For the range where:  $f_{\Box} f = f_z$  s.t.  $|f_z|^{1-jf/f} |f_z|^{1-jf/f}$

We consider the frequency-dependent numerator term to be 1 and focus on the response of the denominator:

$$h = \frac{g}{m} \frac{r}{d}$$

$$f = \frac{g}{m} \frac{r}{d}$$

$$1 \square j \frac{f}{f}$$

Neglecting numerator term:

$$h = \frac{g}{m} \int_{fe}^{r} \int_{fe}^{$$

And for  $f/f_{\square} >> 1$  (but  $< f/f_z$ ):  $|h_{fe}|^{\approx}$

Unity gain bandwidth:

$$|h|_{fe} = 1 \Rightarrow \prod_{f} |f|_{fe} = 1 \Rightarrow f = \prod_{f} |f|_{fe}$$

$$f_T = \frac{\Box^T}{\Box f_{\square}}$$

BJT unity-gain frequency or GBP

$$\Box = 100 \qquad r = 2500 \ \Box \qquad C = 12 \ pF \qquad C = 2 \ pF \qquad g = 40 \times 10^{-3} \ S$$

$$\Box \Box = \frac{1}{C_{\Box} \Box C_{\Box} r_{\Box}} = \Box c$$

$$f_{\Box} = \frac{1}{C_{\Box} \Box C_{\Box} r_{\Box}} = \Box c$$

$$f_{\Box} = \frac{28.57}{6.28} 10^{6} Hz = 4.55 \ MHz \qquad f_{T} = \Box f_{\Box} = 455 \ MHz$$

$$\Box_{z} = \frac{g}{c} = 40 \times 10^{\frac{-3}{2}} \times 10^{1} \ Hz = 20 \times 10^{9} \ rps$$

$$f_{z} = \frac{g}{c} = 3.18 \times 10^{9} Hz = 3180 \ MHz$$

## Scilab f, Plot

```

//fT Bode Plot

Beta=100;

KdB= 20*log10(Beta);

fz=3180;

fp=4.55;

f= 1:1:10000;

term1=KdB*sign(f); //Constant array of len(f)

term2=max(0,20*log10(f/fz)); //Zero for f < fz;

term3=min(0,-20*log10(f/fp)); //Zero for f < fp;

BodePlot=term1+term2+term3;

plot(f,BodePlot);

```

## h Bode Plot

fe

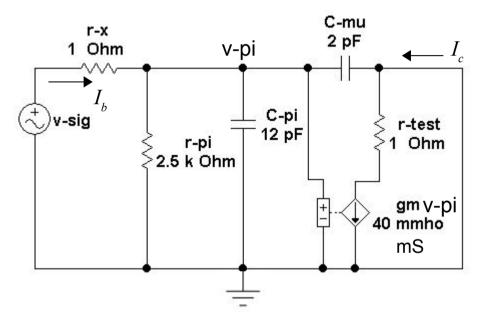

## **Multisim Simulation**

Insert 1 ohm resistors – we want to measure a current ratio.

$$h = \frac{I}{\Leftarrow} \frac{g - s C}{m} \square$$

$$fe \qquad I^b \quad \frac{1}{r} \square s \square \square C \square$$

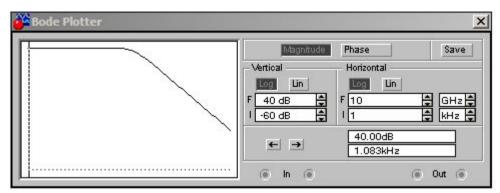

## Simulation Results

## Low frequency |h

## Theory:

Unity Gain frequency about 449 MHz

#### ANALOG CIRCUITS

Presented By,

G.R.Mahendra Babu,

Assistant Professor,

Dept of ECE/ FoE/ KAHE.

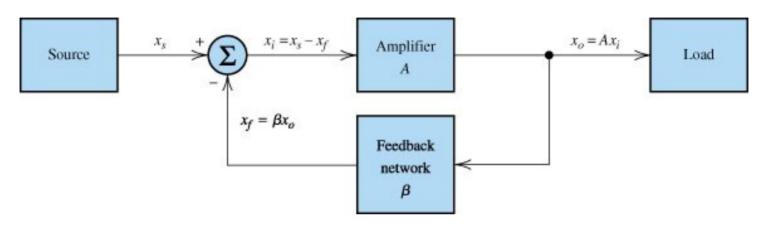

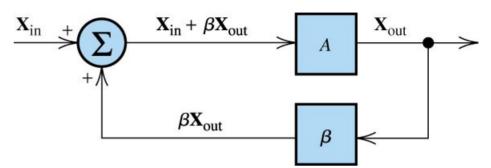

## **Feedback and Oscillators**

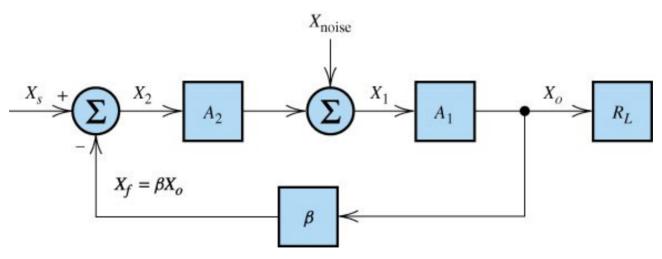

### 9.1 Effect of Feedback on Gain

#### **Closed-Loop Gain**

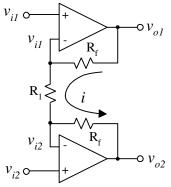

**Figure 9.1** Feedback amplifier. Note that the signals are denoted as x, x, x, and so on. The signals can be either currents or voltages.

$$x = x - \beta x$$

$$x = A(x - \beta x)$$

$$x = A(x - \beta x)$$

$$A = A(x$$

$A_f - \textbf{closed-loop gain};$  A - open-loop gain;  $A\beta - \textbf{loop gain};$   $If A\beta > 0 - \textbf{negative feedback};$   $if A\beta < 0 - \textbf{positive feedback}.$

### **Problems Associated With Positive Feedback**

$$A = \underbrace{x_o}_{f} = \underbrace{\frac{A}{1 + A\beta}} \tag{9.1}$$

#### 1. Positive feedback:

Let

$$A = -10$$

;  $\beta = 0.099$ .  $A = -10_4$ .

Let  $A = -9.9$ ;  $\beta = 0.099$ .  $A_f = -901$ .

1% change of  $A$  causes 91% change of  $A$ .

#### 2. Negative feedback:

Let

$$A = 10^4$$

;  $\beta = 0.01$ .  $A_f = 100$ .

Let  $A = 9000$ ;  $\beta = 0.01$ .  $A_f = 10\%$  change of  $A$  causes  $1\%$  change of  $A$ .

**Conclusion:** *Positive feedback* increases the gain, but the gain is unstable. In contrast *negative feedback* decreases the gain and stabilizes it.

#### **Gain Stabilization**

$$\frac{dA}{dA} = \frac{1 + A\beta - A\beta}{(1 + A\beta)} = \frac{1}{(1 + A\beta)}$$

$$dA = \frac{dA}{A} \frac{A}{(1 + A\beta)}; \quad A = \frac{A}{1 + A\beta}$$

$$\int_{f}^{2} \frac{dA}{(1 + A\beta)}; \quad A = \frac{A}{1 + A\beta}$$

$$\frac{dA_{f}}{A_{f}} = \frac{dA}{A} \frac{A}{(1 + A\beta)}$$

$$\frac{dA_{f}}{A_{f}} = \frac{dA}{A} \frac{1}{(1 + A\beta)}$$

(9.2)

$dA_f A_f$  relative instability of the closed-loop gain;

dA/A – relative instability of the open-loop gain.

#### **Exercise**

9.2 (a) An amplifier has  $A = 10^5 \pm 10$  %. Suppose that we want a feedback amplifier with  $A_f$  that varies by no more than  $\pm 1$  % due to variations in A. What is the maximum value of nominal gain  $A_f$  allowed? (b) Repeat if  $A_f$  is allowed to vary by only  $\pm 0.1$  %.

#### **Solution:**

(a) In (9.2)

$$\frac{dA}{A_f} = \frac{dA}{A} \frac{1}{(1 + A\beta)}$$

(9.2)

$$\frac{dA}{A} = 10\% = \frac{dA}{A} = 1\% = 0.01$$

$$0.1 = 0.01 \frac{1}{(1 + A\beta)} \Rightarrow (1 + A\beta) = 10;$$

Since  $A = 10^5$  the maximum gain with variation less than 1% is

$$A_f = \frac{A}{1 + A\beta} = \frac{10^5}{10} = 10^4$$

(b)

$$\frac{dA}{\frac{f}{A_f}} = \frac{dA}{\frac{1}{(1+A\beta)}}$$

$$\frac{dA}{\frac{dA}{f}} = 10\% = \frac{\frac{dA}{A}}{\frac{1}{(1+A\beta)}}$$

$$\frac{dA}{\frac{dA}{f}} = 10\% = \frac{\frac{dA}{A}}{\frac{1}{f}} = 0.1\% = 0.001$$

$$\frac{dA}{\frac{1}{f}} = 10\% = \frac{\frac{dA}{A}}{\frac{1}{f}} = 0.1\% = 0.001$$

$$0.1 = 0.001 \frac{1}{\frac{1}{A\beta}} \Rightarrow (1+A\beta) = \frac{10^5}{100} = 10^5$$

$$10;$$

$$\frac{dA}{\frac{1}{f}} = 10\% = \frac{\frac{dA}{A}}{\frac{1}{f}} = 0.1\% = 0.001$$

$$\frac{dA}{\frac{1}{f}} = 10\% = \frac{\frac{dA}{A}}{\frac{1}{f}} = 0.1\% = 0.001$$

$$\frac{dA}{\frac{1}{f}} = 10\% = \frac{\frac{dA}{A}}{\frac{1}{f}} = 0.1\% = 0.001$$

$$\frac{dA}{\frac{1}{f}} = 10\% = \frac{\frac{dA}{A}}{\frac{1}{f}} = 0.1\% = 0.001$$

$$\frac{dA}{\frac{1}{f}} = 10\% = \frac{\frac{dA}{A}}{\frac{1}{f}} = \frac{100\%}{100} = \frac{100\%}{100$$

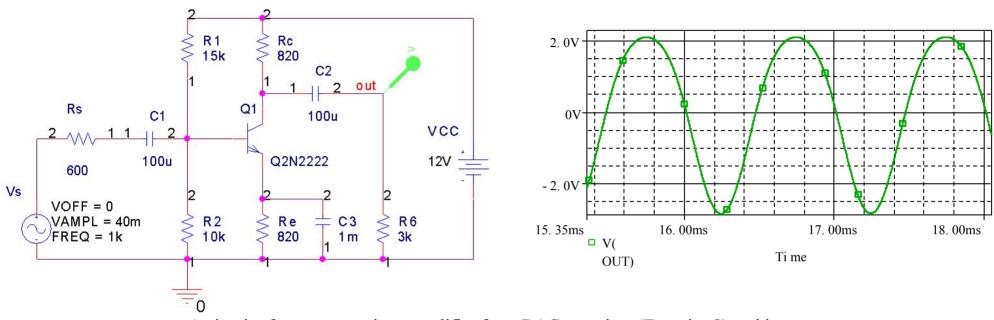

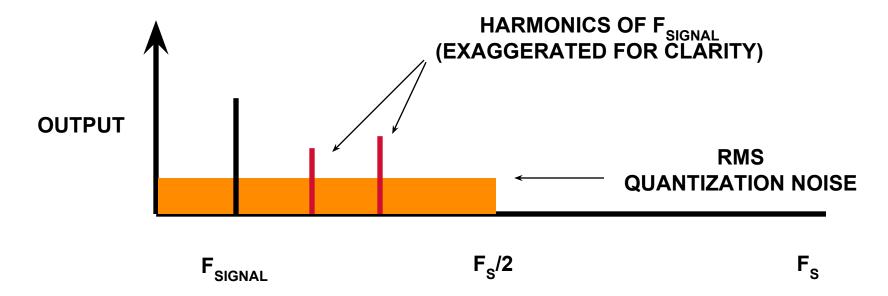

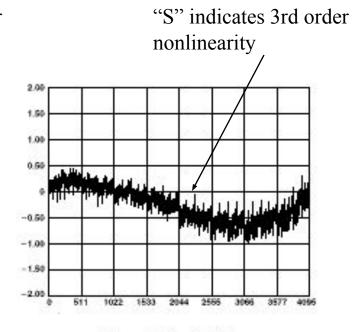

### 9.2 Reduction of Nonlinear Distortion and Noise

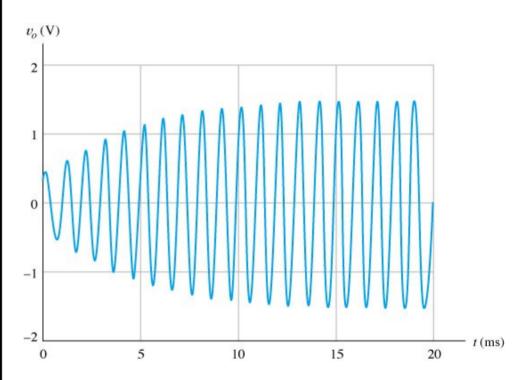

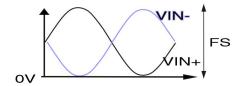

A circuit of common-emitter amplifier from BAC exercises (Exercise 8) and its output waveshape. The signal at the output is distorted.

The distortion of the output signal is basically due to the curvature of the input characteristic of the BJT.

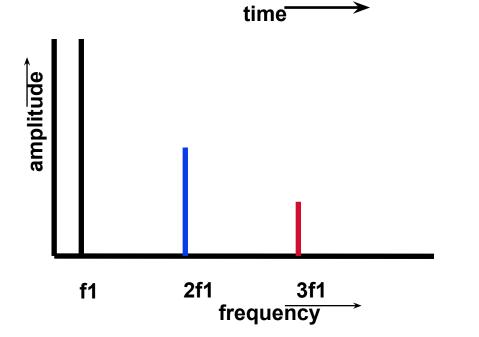

The output signal is not any more sinusoidal and has harmonics.

Figure of merit of the distortion: the amplitudes of the harmonics.

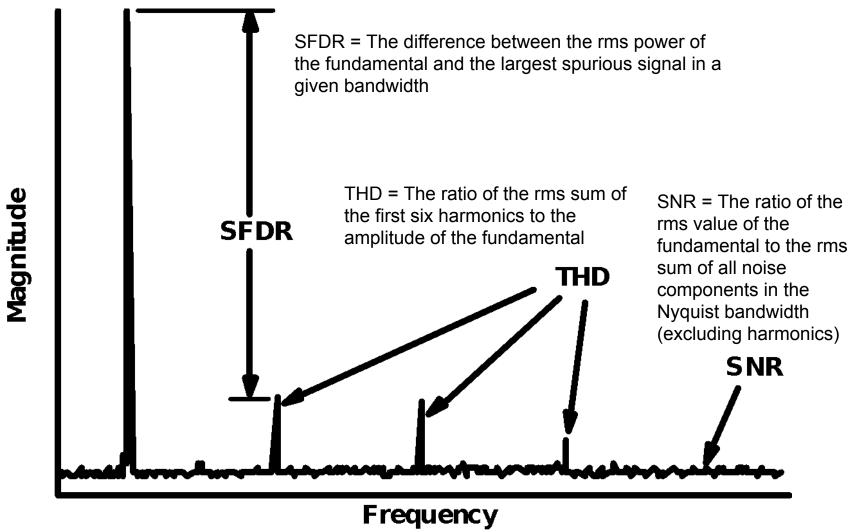

#### **Total harmonic distortion (THD:**

$$THD = \frac{\sqrt{V_2^2 + V_3^2 + V_4^2 + V_4^2}}{V}$$

V – amplitude of the fundamental harmonic;  $V^1, V, \ldots$  -amplitudes of the higher harmonics.

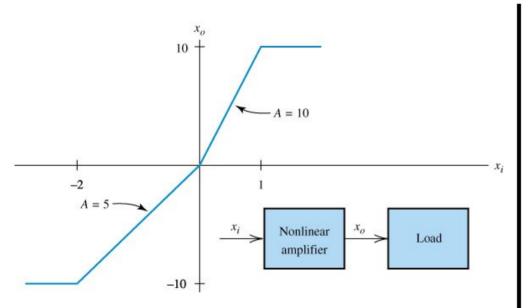

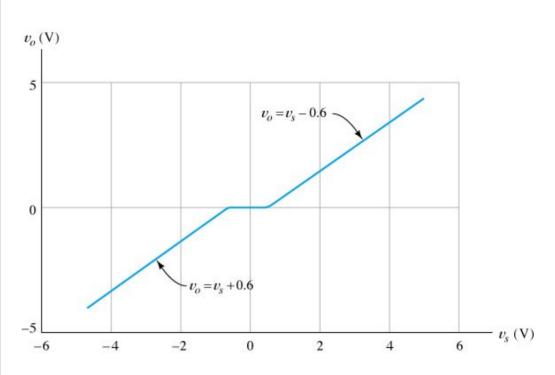

**Figure 9.2** Transfer characteristic of a certain nonlinear amplifier.

Gain of the nonlinear amplifier in Figure 9.2:

- if 0 < x < 10; A = 10;

- if  $-10 < x_i < 0$ ; A = 5.

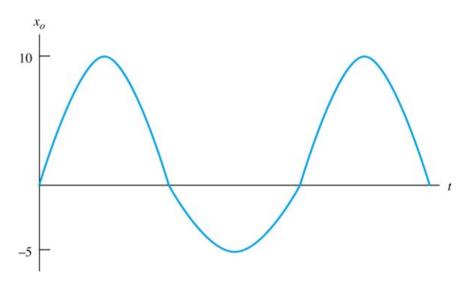

**Figure 9.3** Output of amplifier of Figure 9.2 for  $x = \sin(\omega t)$ . Notice the distortion resulting from the nonlinear transfer characteristic.

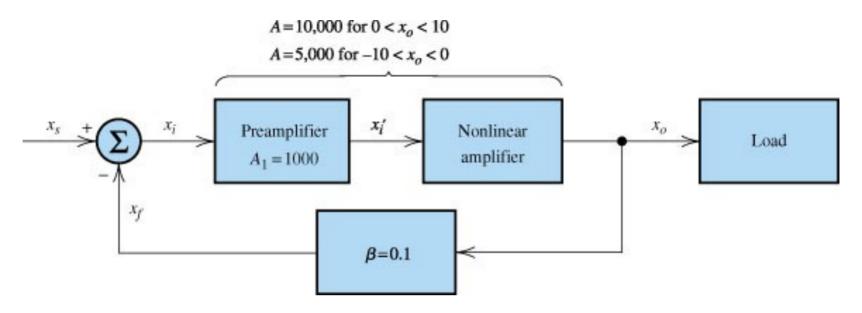

Figure 9.4 Addition of a linear high-gain preamplifier and negative feedback to reduce distortion.

Open loop gain of the cascade of preamplifier and nonlinear amplifier:

- if 0 < x < 10;  $A = 10_4$ ;

- if  $-10 < x_i < 0$ ; A = 5000.

Closed loop gain of the whole amplifier:

• if

$$0 < x < 10$$

$$A_f = \frac{A}{1 + A\beta} = \frac{10^4}{1 + 10^4 \times} = 9.99$$

• if

$$-10 < 0.1 < 0$$

$$A_f = \frac{A}{1 + A\beta} = \frac{5000}{1 + 5000} \times = 9.98$$

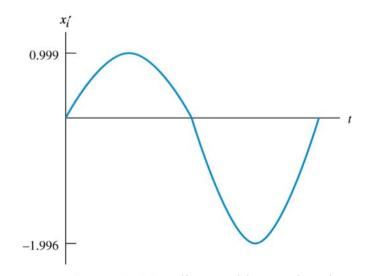

### **Compensatory Distortion of the Input Signal**

**Figure 9.4** Addition of a linear high-gain preamplifier and negative feedback to reduce distortion.

$$x = x - x$$

$$x_{i} = x_{s} - x \xrightarrow{f}$$

$$x_{i} = x_{s} - x \xrightarrow{\frac{A\beta}{1}}$$

$$x = x \xrightarrow{\frac{1}{1 + A\beta}}$$

$$x = x \xrightarrow{\frac{1}{1 + A\beta}}$$

$$x_{i} = x_{s} / 1001 \quad \text{for} \quad 0 < x^{i} < 10$$

$$x_{i} = x_{s} / 501 \quad \text{for} \quad -2 \times 10^{-3} < x^{i} < 0$$

$$(9.4)$$

Figure 9.5 Predistorted input signal.

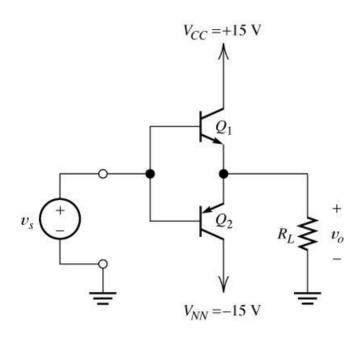

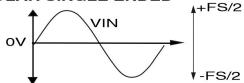

## **An Example with Crossover Distortion**

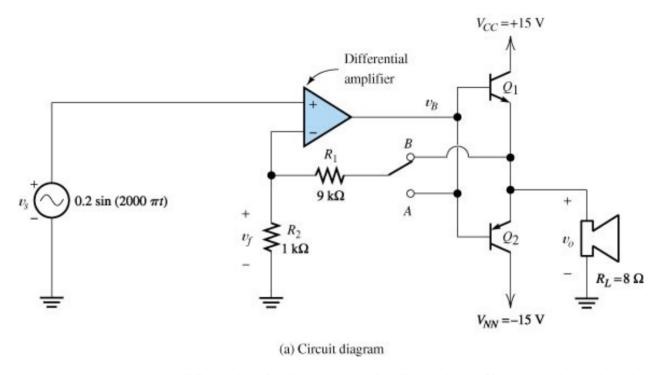

Figure 9.7 Nonlinear class-B power amplifier.

$$v_o = v_s - 0.6$$

for  $v_s > 0.6$

$$v \approx v + 0.6$$

for  $v < -0.6$

**Figure 9.8** Transfer characteristic for the amplifier of Figure 9.7.

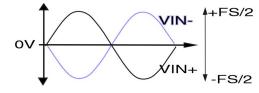

**Figure 9.9a** Class-B power amplifier with feedback. The feedback has effect to reduce the distortion if the source of the distortion is included in the feedback loop. In the circuit above the switch must be in position B. If the switch is in position A, the feedback has no effect on the distortion.

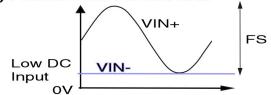

## Influence of the Feedback on the Noise in Amplifiers

**Noise** – a random signal, generated in the circuit or penetrating from outside in the circuit. The noise adds to the desired signal and deteriorates its quality. The noise generation in the circuit is basically due to the transfer of the current by charged particles (electrons and holes) and the thermal agitation.

All electronic elements, except capacitors and inductors generate noise.

Generally the **negative feedback doesn't reduce the noise in the amplifier**, since the feedback also generates noise.

The negative feedback can help in some particular cases, when the source of the noise is localized in one stage of the circuit only. Than including this stage in a feedback loop reduces the noise.

**Figure 9.13** Feedback amplifier with a noise source. The noise is generated in one stage of the circuit (A) and the feedback can reduce this noise only.

11

## 9.3 Input and Output Impedance

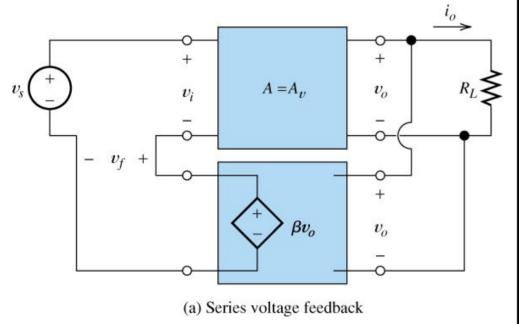

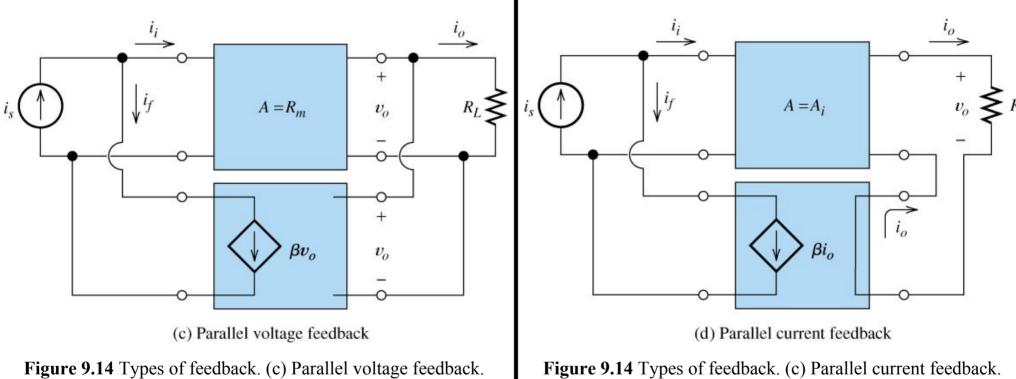

## **Types of Feedback**

Conditionally the feedback is divided in 4 types:

- series voltage;

- series current;

- parallel voltage;

- parallel current.

Figure 9.14 Types of feedback. (a) Series voltage feedback.

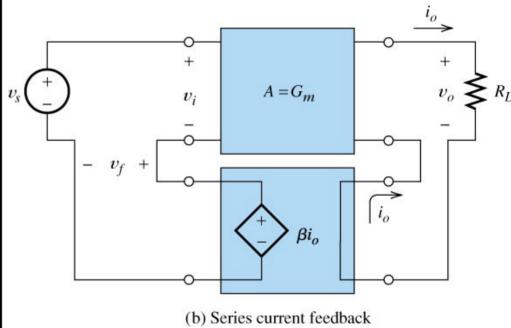

Figure 9.14 Types of feedback. (b) Series current feedback.

Figure 9.14 Types of feedback. (c) Parallel current feedback.

## The Effects of Various Types of Feedback on Gain

The general formula

$$A_f = \frac{x_o}{x} = \frac{A}{1 + A\beta}$$

is valid for all feedback types. For the different feedback types the gains assumed as A, A and  $\beta$  are different quantities.

```

For series voltage feedback: x = v, x = v.

A, A and \beta are voltage gains. o s

For series current feedback: x = i, x = v.

A and A are transconductances: {}^sG \stackrel{\$}{=} i / v;

\beta^f is a transresistance: \beta = v/i.

For parallel voltage feedback: x^f \stackrel{o}{=} v, x = i.

A and A are transresistances: R = \sqrt[p]{i},

\beta^f is a transconductance: \beta = i/v^m.

For parallel current feedback: x_s = i_o, x_s = i_s.

```

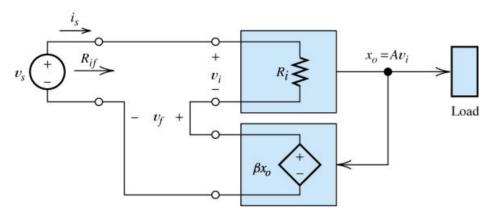

# The Effects of Series Feedback on Input Impedance

**Figure 9.15** Model for analysis of the effect of series feedback on input impedance.

$$R_{if} = \frac{v}{i_s} = R \left( 1 + A\beta \right) >$$

The series feedback increases the input impedance.

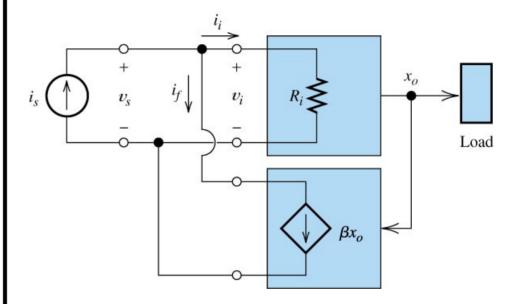

# The Effects of Parallel Feedback on Input Impedance

**Figure 9.16** Model for analysis of the effect of parallel feedback on input impedance.

$$R_{if} = \frac{v_s}{i} = \frac{R_i}{1 + A\beta} < R_i$$

The parallel feedback decreases the input impedance.

# The Effects of Voltage Feedback on Output Impedance

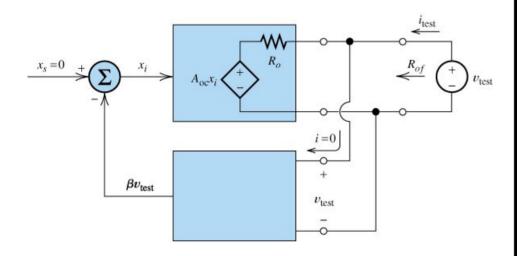

**Figure 9.17** Model for the analysis of output impedance with voltage feedback.

$$R_{of} = \frac{v_{test}}{i} = \frac{R_o}{1 + A\beta} < R_o$$

The voltage feedback decreases the output impedance.

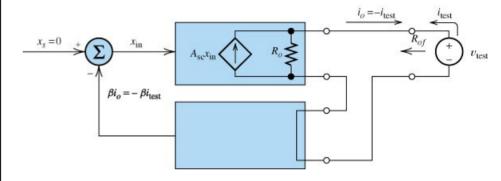

# The Effects of Current Feedback on Output Impedance

**Figure 9.18** Model for the analysis of output impedance with current feedback.

$$R_{of} = \frac{v}{i_{test}} = R \left( 1 + A\beta \right) >$$

The current feedback increases the output impedance.

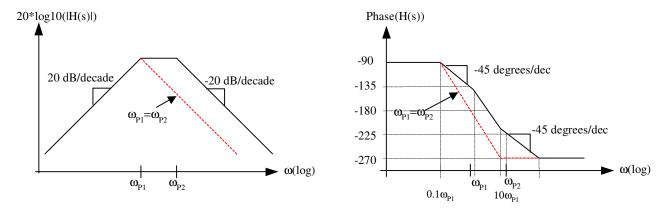

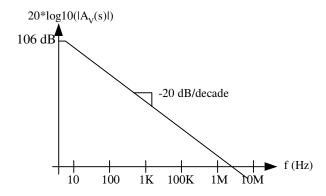

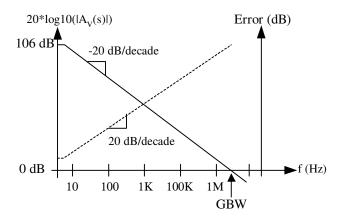

## 9.7 Effect of Feedback on Pole Locations

## **Dominant - Pole Amplifiers**

**Poles** – roots of the denominator of the gain. Gain is expressed as a function of Laplace transform variable *s*.

Expression for open-loop gain

$$A(s) \frac{A}{(s/2\pi f_b)} +$$

$$= 1$$

$$(9.42)$$

If  $\beta$  is constant, the closed-loop gain is

$$A_{f}(s) = \frac{\frac{A_{0}}{s/(2\pi f)} \pm 1}{1 + \frac{A \beta}{s/(2\pi f_{b})} + 1}$$

The closed-loop gain can be put into the form

$$A(s) \frac{A_{0f}}{(s/2\pi f_{bf})+1}$$

$$= (9.43)$$

The closed-loop dc gain is

$$A_{0f} = \frac{A_0}{1 + A}$$

(9.44)

The closed-loop break frequency

$$f = f \left( 1 + A \beta \right) \tag{9.45}$$

Conclusion: negative feedback increases the upper break frequency of the amplifier.

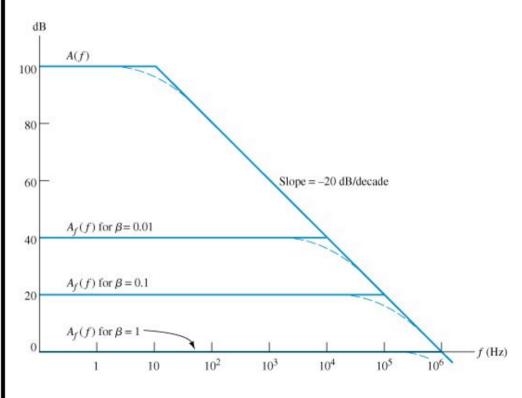

# Example 9.5 Bode Plots for a Dominant - Pole Amplifier with Feedback

A certain integrated - circuit operational amplifier has a single pole in its gain function. The open - loop dc gain is  $A_f = 10^5$  and the open - loop break frequency is  $f = 10^6$  Hz. Prepare magnitude Bode plots for A(f) and  $A_f(f)$  if  $\beta = 0.01$ , 0.1, and 1.

### **Solution:**

Open-loop dc gain in dB is

$$A_{0 \text{ dB}} = 20 \log_{10} |A_0| = 20 \log^{10} 10^5 = 100 \text{dB}$$

For  $\beta = 0.01$

$$A_{0f} = \frac{A_{0}}{1 + A_{0}\beta} = \frac{10^{5}}{1 + 0.01 \times 10^{5}} = 99.9 \approx 40dB$$

$$f_{bf} = f(1 + A\beta) = 10 \times (1 + 0.01 \times 10^5) \approx 10 \text{kHz}$$

For

$$\beta = 0.1$$

:  $\frac{A}{0f} = 20 \text{dB}$  and  $\frac{f}{bf} = 100 \text{kHz}$ .

For  $\beta = 1$ :  $\frac{A}{0f} = 0 \text{dB}$  and  $\frac{f}{bf} = 1 \text{MHz}$ .

**Figure 9.38** Bode plots for the feedback amplifier of, Example 9.5.

### **Gain Bandwidth Product**

$$A \int_{0 f b f} = \frac{A}{1 + A} \times f \left( 1 + A \beta \right) = A$$

$$\beta \int_{0}^{0} f \int_{0}^{b} (9.46)$$

The product of dc gain and the bandwidth of an amplifier is independent of the feedback. It is an important parameter of the amplifier and is called **gain-bandwidth product** or **unity gain frequency**.

## **Influence of Negative Feedback on Amplifiers - Summary**

- 1. **Gain** is decreased and divided by  $1 + \beta A$ .

- 2. Gain stability is improved. Relative gain variation dA/A is divided by  $1 + \beta A$ .

- 3. **Nonlinear distortion** is reduced.

- 4. In general the **noise** is increased. Only in some particular cases, when the noise source is localized in a part of the amplifier, the negative feedback can reduce the noise from this source.

- 5. **Input and output impedances** are affected from the feedback. Depending on its type (series or parallel, voltage or current) input and output impedances are increased or decreased.

- 6. Upper half-power frequency is increased and multiplied by  $1 + \beta A$ .

## 9.11 Oscillator Principles

### **Linear Oscillators**

**Oscillators**: circuits, which produce periodic ac signals with prescribed properties: waveform; frequency and amplitude.

**Linear oscillators**: the output is approximately sinusoidal. The transistors are operating basically in active region.

**Switching oscillators**: the electronic devices operate like switches. Usually rectangular pulses at the output.

Basic principle of the linear oscillator: part of the output signal is returned at the input of the amplifier via positive feedback loop. The returned signal is enough to produce after amplification the same output signal.

## The Barkhausen Criterion

Figure 9.69 Linear oscillator with external signal X in injected.

$$\mathbf{X} = A \left( f + \beta \right) \mathbf{X}$$

$$(9.52)$$

$$\mathbf{X}_{out} = i \frac{A \left( f \right)}{1 - A \left( f \right)} \mathbf{X}_{in}$$

$$(9.53)$$

To have output signal when X = 0, closed-loop gain must be infinity. This is possible if its denominator is 0, i.e.

$$A(f)\beta(f) = 1 \tag{9.54}$$

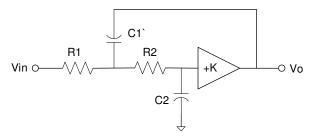

## Example 9.12 Analysis of an Oscillator Circuit

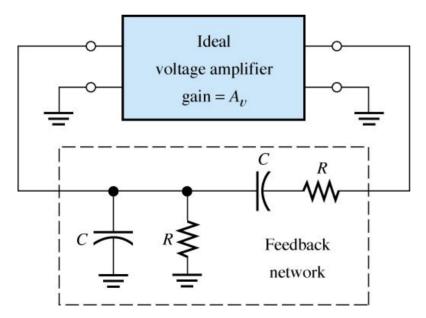

An oscillator is shown in Figure 9.70. The amplifier is an ideal voltage amplifier (infinite input impedance and zero output impedance) with a voltage gain of  $A_v$ . The RC network connected from the amplifier output to the input forms the feedback

network. Find the value of gain  $A_v$  required for oscillation, and find the frequency of oscillation of the circuit.

Figure 9.70 Typical linear oscillator.

#### **Solution:**

$$\beta(f) \frac{V_o}{V} = \frac{R(1/j\omega C)}{R + 1/j\omega C}$$

$$= \frac{R(1/j\omega C)}{R + 1/j\omega C}$$

$$\beta(f) \frac{R}{j\omega C} + \frac{R}{R} \frac{1/j\omega C}{R}$$

$$= \frac{R(1/j\omega C)}{R + 1/j\omega C}$$

$$A \beta = 1$$

$$R \left(3 - A\right) + \left( \omega R - \frac{1}{\omega C} \right) = 0$$

$$R \left(3 - A\right) = 0$$

$$A = 3$$

$$\omega R^{2}C - \frac{1}{\omega C} = 0$$

$$\omega = \frac{1}{RC}$$

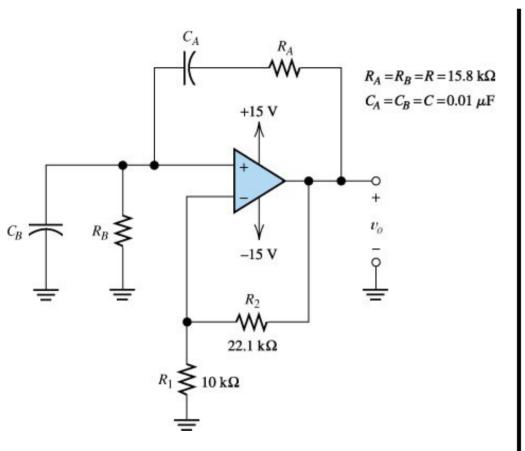

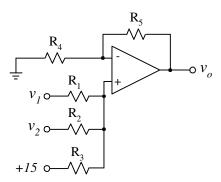

**Figure 9.74** An example of a Wien-bridge oscillator designed on the basis of Example 9.12.

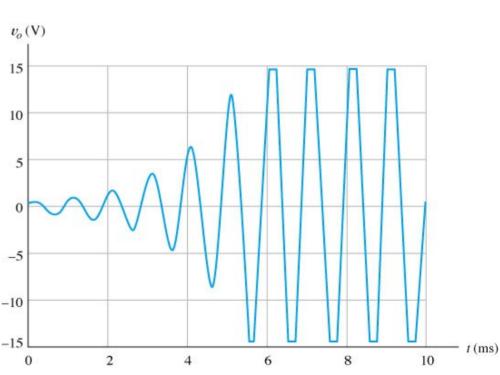

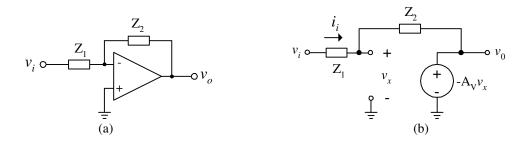

**Figure 9.75** Output voltage of the oscillator in Figure 9.74.

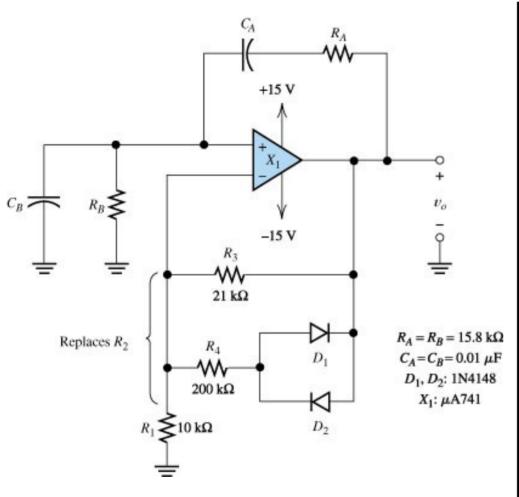

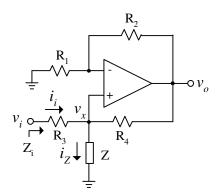

**Figure 9.77** Modification of the circuit of the Wien-bridge oscillator. The diodes and the resistor R<sub>4</sub> limit the amplitude of the output signal. In this way is avoided its clipping.

**Figure 9.78** Output voltage of the oscillator of Figure 9.77.

### Chapter IIIa

## The operational Amplifier and applications.

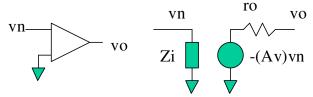

#### III.1. Basic Model for the Operational Amplifier.

The OPerational AMPlifier (OPAMP) is a key building block in analog integrated circuit design. The OPAMP is composed by several transistors and passive elements (resistors and capacitors) and arranged such that its low frequency voltage gain is very high; the dc gain of the OPAMP-741 is around  $10^5$  V/V ( $10~\mu V$  at the input give us 1 V at the output). The design of such complex circuit is discussed in chapter 6; here we will use a simplified linear macromodel to analyze the principles of OPAMP based circuits and their operation. Several circuits are studied such as basic amplifiers, first order and second order filters and some non-conventional applications. The versatility of the OPAMP will be evident at the end of this chapter.

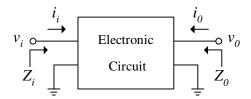

To define the fundamental parameters of a system, let us consider a linear two-port system with two terminals grounded, as the one shown in Figure 3.1. There are 4 variables vi, ii, vo and io to be studied. The interaction between the four variables can be defined in many different ways, depending on the definition of the dependent and independent variables; in real circuits these definitions depend on the input variable (current or voltage) and the most relevant output variable. Usually in voltage amplifiers the input signal is defined as vi while the output is vo.

Fig. 3.1. Electronic circuit represented by a black box.

Since we are assuming that the circuit is linear, among other representations, we can describe the electronic circuit by using the following hybrid matrix representation:

$$\begin{bmatrix} \mathbf{i}_{1} \\ \mathbf{v}_{0} \end{bmatrix} = \begin{bmatrix} \mathbf{g}_{11} & \mathbf{g}_{12} \\ \mathbf{g}_{21} & \mathbf{g}_{22} \end{bmatrix} \begin{bmatrix} \mathbf{v}_{1} \\ \mathbf{i}_{0} \end{bmatrix}$$

g-parameters (3.1a)

or

$$i_{i} = g_{11}v_{i} + g_{12}i_{o}$$

$$v_{o} = g_{21}v_{i} + g_{22}i_{o}$$

(3.1b)

Notice that we are mixing currents and voltages in the matrix, then we call it hybrid representation of the circuit, and the resulting model is termed hybrid model. In many text books you can find at least 4 different set of parameters, but this is one of the most relevant ones for voltage amplifiers. Bipolar and MOS transistors models are based on another model called  $\pi$ -hybrid, to be discussed in the following chapters.

In equations 3.1b, the parameter  $g_{11}$  defines the input conductance, and it relates the input current and the input voltage needed by the circuit without considering the effect of the output current ( $i_0$ =0); the circuit's input conductance is formally defined as follows:

$$g_{11} = \frac{1}{Z_i} = \frac{i_i}{v_i} \bigg|_{i_o = 0} \tag{3.2}$$

This parameter is measured by applying an input voltage source and measuring the input current; the output node is left open such that  $i_0$ =0. Since  $g_{11}$  is the ratio of the input current to the input voltage, while the output is leaved open, its units are amps/volts or  $1/\Omega$ .

The parameter  $g_{12}$  defines the reverse current gain of the topology, and it is defined as

$$g_{12} = \frac{i_i}{i_o}\Big|_{v_i = 0} \tag{3.3}$$

This parameter represents the reverse current gain: current generated at the input due to the output current. In the ideal case this parameter is zero since usually the operational amplifiers are unidirectional; e.g. the input signal applied to the system generates an output signal, but the output signals (current or voltage) should not generate any signal at the input. For measuring this parameter it is required to short circuit the input port such that  $v_i$ =0, then apply a current at the output and measure the current generated at the input port. In practical circuits this parameter is very small and usually it is ignored.

The Forward voltage gain is defined as the ratio of the output voltage and input voltage without any load connected at the output.

$$g_{21} = A_V = \frac{v_o}{v_i} \bigg|_{i_o = 0} \tag{3.4}$$

This is certainly one of the most important parameters of the two-port system; we also refer to  $A_V$  as the open-loop gain of the OPAMP. It represents the circuit's voltage gain without any load impedance attached (output current equal zero).

Another important parameter is the system's output impedance, which relates the output voltage and the output current without taking the effects of the input signal. It is defined by

$$g_{22} = Z_0 = \frac{v_o}{i_o}\Big|_{v_i = 0} \tag{3.5}$$

Thus, the two-port system can be represented by the four aforementioned parameters; the resulting macromodel is shown in Figure 3.2. For sake of clarification we are using impedances instead of admittances in this representation. Notice that a current controlled current source (ICCS) is used for the emulation of parameter  $g_{12}$  since it represents the input current (input port) being generated by the output current (output port). A resistor can not represent this parameter since current is flowing in one port but the voltage at the other port controls it. Similar comments apply to the voltage controlled voltage source represented by  $A_V v_i (g_{21}v_i)$ .

Fig. 3.2. Linear macromodel of a typical voltage amplifier using hybrid parameters.

**Model for the OPAMP.** The ideal OPAMP is a device that can be modeled by using the circuit of Fig. 3.2 with  $A_V=\infty$ ,  $g_{12}=0$ ,  $Z_i=\infty$ , and  $Z_o=0$ . This is of course an unrealistic model, but it is enough for understanding the basic circuits and their operation. We will see that when you connect several circuits in cascade for complex signal

processing, both input and output impedances are important parameters that affect the overall performance of the system. In this section, however these effects are not considered.

Discuss here the main limitations such as input impedance, limited DC gain and DC offsets and input bias current.

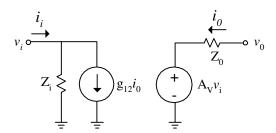

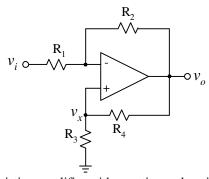

#### III.2. Basic configurations: Inverting and non-inverting amplifier.

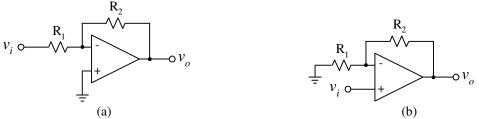

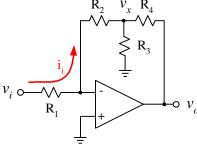

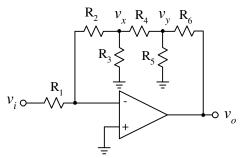

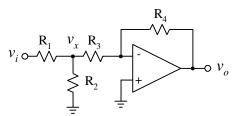

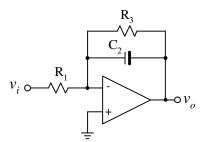

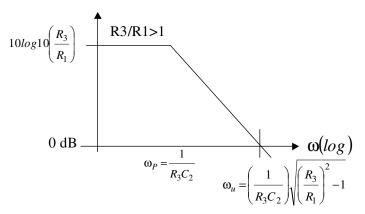

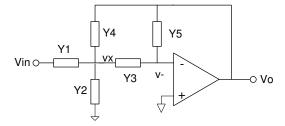

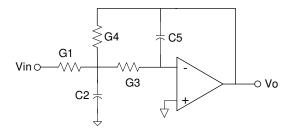

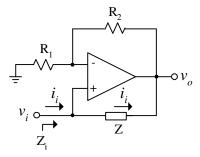

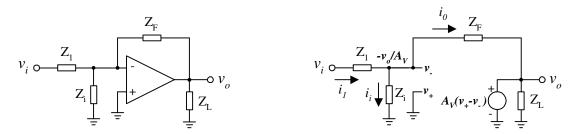

**Inverting configuration.** The first topology to be studied is the inverting amplifier shown in fig. 3.3a. It consists of an impedance connected between the input source and the OPAMP's inverting terminal; the second impedance is connected from the inverting terminal to the output of the OPAMP. Z<sub>2</sub> provides a negative feedback (connecting the OPAMP's output and the negative input); this is the main reason for the excellent properties of this configuration. The simplified linear macromodel of the OPAMP is used for the representation of the inverting amplifier, and the equivalent circuit shown in fig. 3.3b. By using basic circuit analysis techniques it can be easily find that

$$\frac{v_i - v_x}{Z_1} + \frac{v_o - v_x}{Z_2} = 0 \tag{3.5}$$

and

$$\mathbf{v}_{\mathbf{o}} = -\mathbf{A}_{\mathbf{v}} \mathbf{v}_{\mathbf{x}} \tag{3.6}$$

Solving these equations as function of the input and output voltages yields;

$$\frac{v_{o}}{v_{i}} = -\left(\frac{1}{1 + \frac{1 + Z_{2}/Z_{1}}{A_{V}}}\right)\left(\frac{Z_{2}}{Z_{1}}\right)$$

(3.7)

This relationship is also known as closed-loop amplifier's gain since the feedback resistor in combination with the OPAMP form a closed loop. If the open-loop gain of the OPAMP  $A_V$  is very large, then the first factor can be approximated as unity and the closed-loop voltage gain becomes

$$\frac{v_{o}}{v_{i}} = -\frac{Z_{2}}{Z_{1}} \tag{3.8}$$

This result shows that if negative feedback is used and if the open-loop gain of the OPAMP is large enough, the overall amplifier's voltage gain depends on the ratio of the two impedances. Unlike to the gain of the open-loop gain of the OPAMP that can vary by more than 50 % due to transistor's parameters variations and temperature gradients, as will be explained in the following sections, the closed loop gain is quite accurate, especially if same type of impedances are used. Usually ratio of impedances is more precise than the absolute value of components; e.g. ratio of capacitors fabricated in CMOS technologies can be as precise as 99.5 % while the absolute value of the capacitance may change by more than 20%.

Fig. 3.3. Inverting amplifier: a) the circuit and b) the linear macromodel assuming that OPAMP input is infinity and output impedance is zero.

Another important observation is that the differential voltage at the OPAMP input  $v_x$  (see Fig. 3b) is ideally zero. The reasoning behind this observation is as follows: according to 3.8, the output voltage is bounded (not infinity) if  $Z_1$  is not zero or  $Z_2$  is not infinite, hence  $v_i$  is also bounded. Under these conditions and according to expression 3.6 the OPAMP input voltage  $v_x$  is very small if  $A_v$  is large enough; the larger the OPAMP open loop gain the smaller signal at the input of the OPAMP. Therefore the *inputs of the OPAMP can be considered as a virtual short; the voltage difference between the two input terminals*  $(v_+ - v_-)$  is very small but they are not physically connected. The virtual short principle is extremely useful in practice; most of the transfer functions can be easily obtained if this property is used. To illustrate its use, let us consider again the circuit of fig. 3.3b. Due to the virtual ground at the input of the OPAMP,  $v_x=0$  (virtual short) and the input current  $i_i$  is determined by  $v_i/Z_1$ . Since the input impedance of the OPAMP is infinite,  $i_i$  flows throughout  $Z_2$ , leading to an output voltage given by  $-i_iZ_2$ . As a result, the closed-loop voltage gain becomes equal to  $-Z_2/Z_1$ , as stated in equation 3.8.

If the impedances  $Z_1$  and  $Z_2$  are replaced by resistors as shown in Fig. 3.4a, we end up with the basic resistive inverting amplifier. The closed-loop gain is then obtained as

Fig. 3.4. Resistive amplifiers: a) inverting configuration and b) non-inverting configuration.

$$\frac{\mathbf{v}_{0}}{\mathbf{v}_{i}} = -\frac{\mathbf{R}_{2}}{\mathbf{R}_{1}} \tag{3.9}$$

Notice that in the case of the inverting configuration, the amplifier's input impedance is determined by  $R_1$ ; this is a result of the virtual ground present at the inverting terminal of the OPAMP. Hence, if several inverting amplifiers are connected in cascade we have to be aware that the amplifier must be able to drive the input impedance of the next stage.

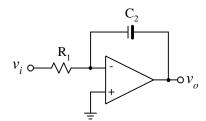

Non-inverting voltage gain configuration. If the input signal is applied at the non-inverting terminal and R1 is grounded, as shown in fig. 3.4b, the non-inverting configuration is obtained. Notice that the *feedback is still negative*. If  $R_2$  is connected to the positive terminal, the circuit becomes unstable and useless for linear applications; this will be evident in the following sections. The closed-loop voltage gain of the non-inverting configuration can be easily obtained if the virtual short principle is used. Due to the high gain of the OPAMP, the voltage difference between the inverting and non-inverting terminals is very small; hence the voltage at the non-inverting terminal of the OPAMP is also  $v_i$ . The current flowing through  $R_1$  and  $R_2$  is then given by  $v_i/R_1$ ; therefore the output voltage is computed as

$$\frac{\mathbf{v}_{o}}{\mathbf{v}_{i}} = \frac{\mathbf{v}_{i} + \mathbf{i}_{1} \mathbf{R}_{2}}{\mathbf{v}_{i}} = \frac{\mathbf{v}_{i} + (\mathbf{v}_{i} / \mathbf{R}_{1}) \mathbf{R}_{2}}{\mathbf{v}_{i}} = 1 + \frac{\mathbf{R}_{2}}{\mathbf{R}_{1}}$$

(3.10)

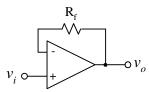

The voltage gain is therefore greater or equal than 1. An important characteristic of this configuration is that ideally its input impedance is infinity; hence several stages can be easily connected in cascade. A special case of the non-inverting configuration is the buffer configuration shown in figure 3.5. If  $R_1 = \infty$ , according to equation 3.10, the voltage gain is unity; in this case the value of  $R_2$  is not critical and can even be short-circuited ( $R_2 = 0$ ). This topology is also known as unity gain amplifier or buffer, and it is very popular for driving small impedances; e.g. speakers, motors, etc.

Fig. 3.5 OPAMP in unity gain buffer configuration

#### Emphasis on loading effects; discuss these issues in class!

#### III.3. Amplifier with multiple inputs and superposition.

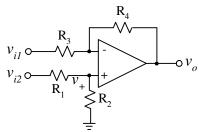

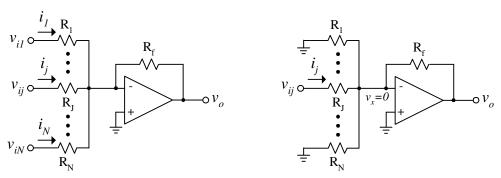

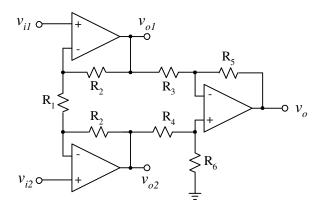

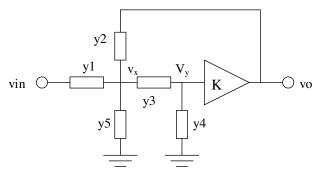

Input signals can be applied to the two inputs of the OPAMP, as shown in Fig. 3.6. R1 and R2 are a voltage divider; the input voltage at the non-inverting  $(v_*)$  terminal is then

Fig. 3.6. Amplifier configuration with two input signals applied to the non-inverting and inverting terminals.

$$\frac{\mathbf{v}_{+}}{\mathbf{v}_{i2}} = \frac{\mathbf{R}_{2}}{\mathbf{R}_{1} + \mathbf{R}_{2}} \tag{3.11}$$

If a virtual short at the OPAMP inputs is assumed, the voltage at the inverting and non-inverting terminals is the same, and determined by  $v_{+}$ . Using KCL at the inverting terminal of the circuit leads to

$$\frac{v_0 - v_+}{R_4} = \frac{v_+ - v_{i1}}{R_3} \tag{3.12}$$

Using equations 3.11 and 3.12, the output voltage is obtained, yielding

$$v_o = -\left(\frac{R_4}{R_3}\right)v_{i1} + \left(\frac{R_2}{R_1 + R_2}\right)\left(1 + \frac{R_4}{R_3}\right)v_{i2} \tag{3.13}$$

Notice that the output voltage is a linear combination of the two input signals: the first component is determined by the  $v_{i1}$  and the other one determined by  $v_{i2}$ . This analysis can always be used, but we can also take advantage of the properties of linear systems.

Superposition principle for a linear system. If the OPAMP is considered as a linear device and only linear impedances are used, then the output voltage is a linear combination of all the inputs applied. If several inputs are applied to the linear circuit, then the output can be obtained considering each input signal at a time; e.g. grounding all other input signals and applying the input signal under study. Therefore, the following property holds: if

$$v_{o}(v_{i1}, v_{i2}, ..., v_{iN}) = \sum_{j=1}^{N} \left(k_{j} v_{ij} \Big|_{v_{ik \, k \neq j} = 0}\right)$$

(3.14a)

then

$$v_{o}(v_{i1}, v_{i2}, ..., v_{iN}) = v_{o}(v_{i1}, 0...0) + v_{o}(0, v_{i2}, ...0) + \dots + v_{o}(0, 0, ... v_{iN})$$

(3.14b)

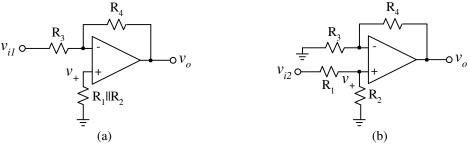

This property is known as the *superposition principle*. Let us apply this principle to the topology shown in Fig. 3.6, where two inputs are applied to the amplifier. The circuit is analyzed by applying one input signal at a time: if  $v_{i1}$  is considered,  $v_{i2}$  is made equal zero. The equivalent circuit is shown in Fig. 3.7a.

Fig. 3.7 Equivalent circuits for the computation of the output voltage: a) for  $v_{i1}$  and b) for  $v_{i2}$ .

Since the input impedance of the OPAMP is infinite, the current flowing through  $R_1||R_2|$  is zero, and  $v_+=0$ . The resulting circuit is the typical inverting amplifier where the output voltage is given by  $-(R_4/R_3)v_{i1}$ ; notice that this output corresponds to the first term in equation 3.13. If the first input is grounded and signal  $v_{i2}$  is considered, the resulting equivalent circuit is depicted in fig. 3.7b. The voltage at the non-inverting terminal is given by equation 3.11, and the output voltage is equal to  $v_0=(1+R_4/R_3)v_+$ ; the final result leads to the second term of equation 3.13.