| Course | O | hi | iec1 | tiv  | es: |

|--------|---|----|------|------|-----|

| Course | V | ν. |      | LI V | CO. |

| $\Box$ | Го | introduce | the  | architecture    | and  | programming | of  | 8085 | microprocessor. |

|--------|----|-----------|------|-----------------|------|-------------|-----|------|-----------------|

|        |    | muco      | CIIC | ai cilicoctai c | ullu | programming | O 1 | 0000 | imeroprocessor. |

- ☐ To introduce the interfacing of peripheral devices with 8085 microprocessor.

- ☐ To introduce the architecture and programming of 8086 microprocessor.

- ☐ To introduce the architecture, programming and interfacing of 8051 micro controller.

# **Learning outcomes:**

This course is designed to introduce the basic concepts of Microprocessor and Microcontroller and provide an understanding of the basic concepts of various Interfacing and Applications. The course also helps the students to develop the ability to designing a programming for various applications.

## **UNIT I Microprocessor-8086**

-Architecture-Signals-Memory Register Organization Organization-Bus Operation-I/O Addressing Minimum Mode-Maximum Mode-Timing Diagram-Interrupts - Service Routines -I/O and Memory Interfacing concepts.

# **UNIT II Programming of 8086**

Addressing Modes-Instruction format-Instruction set-Assembly language programs in 8086. RISC architecture – introduction to ARM Programming-register configuration and instruction set sample program.

# **UNIT III Interfacing Devices**

Programmable Peripheral Interface (8255) - Programmable Interval Timer (8254) - Programmable Interrupt Controller (8259A) - Programmable DMA Controller (8257) - Programmable Communication Interface (8251A) – Programmable Keyboard and Display Controller (8279).

### **UNIT IV Microcontroller-8051**

Register Set-Architecture of 8051 microcontroller- I/O and memory addressing-Interrupts-Instruction set- Addressing modes. .

# **UNIT V Programming And Interfacing Of 8051**

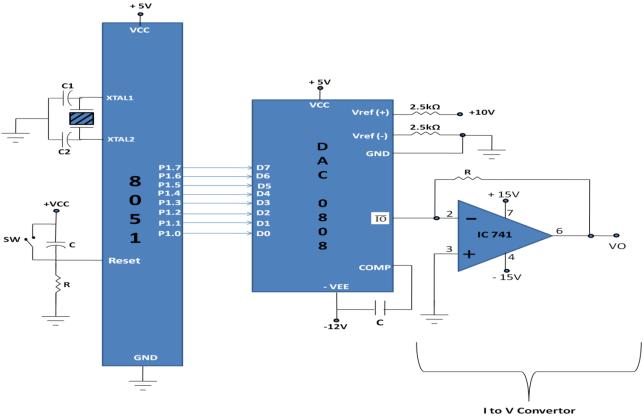

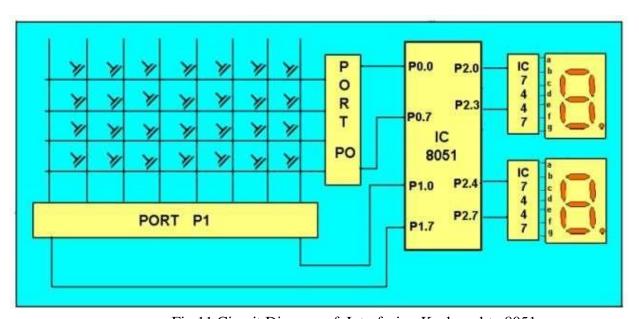

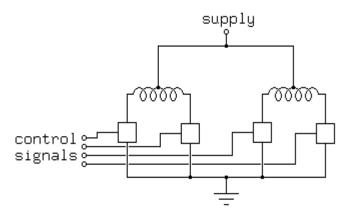

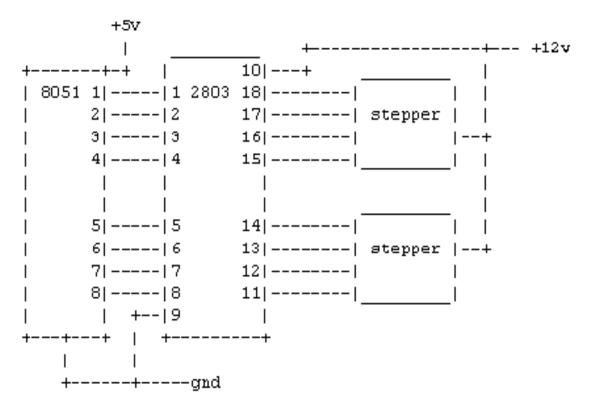

Timer-Serial Communication-Interrupts Programming-Interfacing to External Memory-Interfacing to ADC, LCD, DAC, Keyboard and stepper motor.

### **Total Hours: 45**

#### **Text Books:**

- 1. K. Ray and K. M. Bhurchandi, Advanced Microprocessors and Peripherals. Tata McGraw Hill, New Delhi, 3rd edition, 2013.

- 2. Douglas V.Hall, Microprocessor and Interfacing Programming and Hardware. Tata McGraw Hill, New Delhi 2007

### **References:**

- 1. Muhammad Ali Mazidi, Janice Gillispie Mazidi, Rolin D.MCKinlay The 8051 Microcontroller and Embedded Systems Pearson Education, New Jersy, 2nd edition, 2009

- 2. Krishna Kant, Microprocessor and Microcontroller Architecture, programming and system design using 8085, 8086, 8051 and 8096, PHI, New Delhi, 2008

- 3. Kenneth J.Ayala, The 8051 Microcontroller, Thompson Delmar Learning, New Delhi, 2007

- 4. Barry B.Brey, The Intel Microprocessors Architecture, Programming and Interfacing,

- 5. Pearson Education, New Delhi, 2007

## Websites:

- 1. http://www.8052.com/tut8051http://www.eastaughs.fsnet.co.uk/cpu/index.htm

- 2. http://www.webphysics.davidson.edu/faculty/dmb/py310/8085.pdf

- 3. http://www.aust.edu/cse/moinul/8086\_lectures.pdf

- 4. http://www.cache.com.hk/datasheetC8255ovview.html

# KARPAGAM ACADEMY OF HIGHER EDUCATION

(Established Under Section 3 of UGC Act 1956)

Pollachi Main Road, Eachanari Post, Coimbatore – 641 021. INDIA

Phone: 0422-6471113-5, 6453777 Fax No: 0422 -2980022-3

Email: info@karpagam.com Web: www.kahedu.edu.in

NAME OF THE STAFF : REGI SARAL A

DESIGNATION : ASSISTANT PROFESSOR

SUBJECT : MICROPROCESSORS AND MICROCONTROLLERS

SUBJECT CODE : 16BECS403A

| S.NO | DESCRIPTION OF PORTIONS TO BE<br>COVERED                  | TEACHING AIDS                                        | HOURS |  |

|------|-----------------------------------------------------------|------------------------------------------------------|-------|--|

|      | UNIT I MICROPROCESSOR 8086                                |                                                      |       |  |

| 1    | Register Organization Signals                             | R(1)-page No.130-132                                 | 1     |  |

| 2    | 8086 Architecture                                         | R(1)-page No.128-135                                 | 2     |  |

| 3    | Memory Organization                                       | R(1)-page No.142-146                                 | 1     |  |

| 4    | Bus Operation-I/O Addressing Minimum<br>Mode-Maximum Mode | R(1)-page No.146-149                                 | 1     |  |

| 5    | Timing Diagram-Interrupts                                 | R(1)-page No.169-177                                 | 1     |  |

| 6    | Service Routines – I/O and Memory Interfacing concepts.   | R(1)-page No.164-168                                 | 2     |  |

|      | UNIT II PROGRAMMING OF 8086                               |                                                      |       |  |

| 7    | Addressing Modes of 8086                                  | R(1)-page No.188-197                                 | 2     |  |

| 8    | Instruction format-Instruction set                        | R(1)-page No. 203-240                                | 2     |  |

| 9    | Assembly language programs in 8086. RISC Architecture     | T(1)-page No.3.1-4.35<br>http://youtu.be/dw6fUVJZKL8 | 2     |  |

| 10   | Introduction to ARM Programming                           | http://youtu.be/XojE13qeiTE                          | 1     |  |

| 11   | Register configuration and instruction set                | http://youtu.be/7LqPJGnBPMM                          | 1     |  |

| 12   | Sample program                                            | T(1)-page No.3.1-4.35                                | 1     |  |

|      | UNIT III INTERFACING DEVICES                              |                                                      |       |  |

| 13   | Programmable Peripheral Interface (8255)                  | R(1)-page No.249-253                                 | 2     |  |

| 14   | Programmable Interval Timer (8254)                        | R(1)-page No.313-319                                 | 1     |  |

| 15   | ProgrammableInterrupt Controller (8259A)                  | T(1)-page No.8.30-8.38                               | 2     |  |

| 16 | Programmable DMA Controller (8257)                        | T(1)-page No.11.5-11.10                      | 2 |

|----|-----------------------------------------------------------|----------------------------------------------|---|

| 17 | Programmable CommunicationInterface (8251A)               | http://youtu.be/ODqkBoRvYUU                  | 1 |

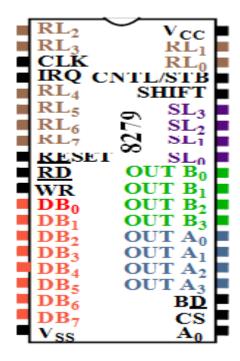

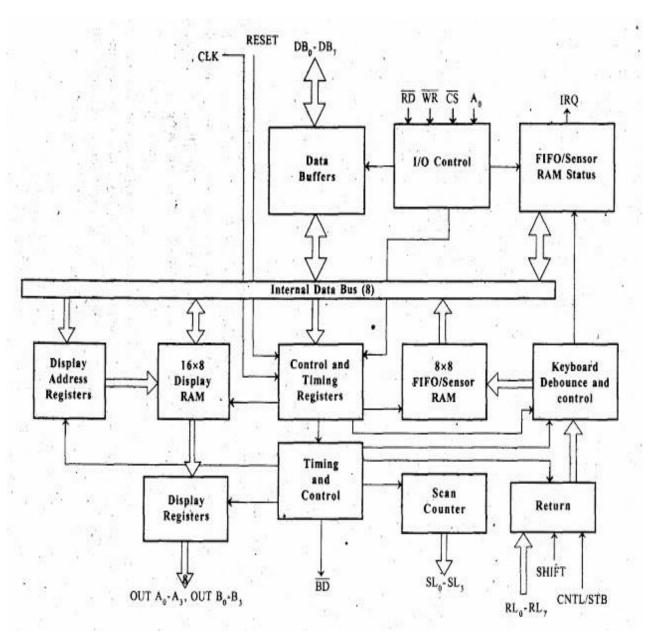

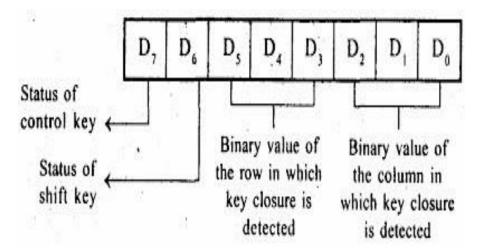

| 18 | Programmable Keyboard and Display Controller (8279).      | R(1)-page No.281-291                         | 2 |

|    | UNIT IV MICROCONTROLLER-8051                              |                                              |   |

| 19 | Register Set of 8051                                      | R(1)-page No.4.24-4.30                       | 1 |

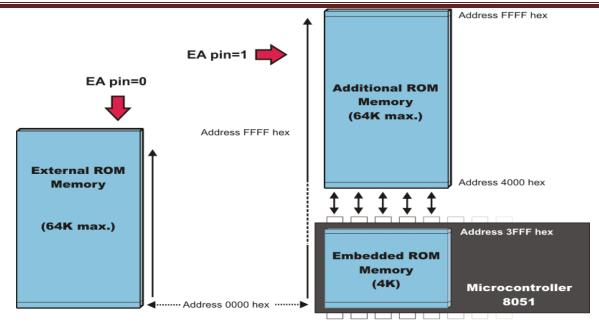

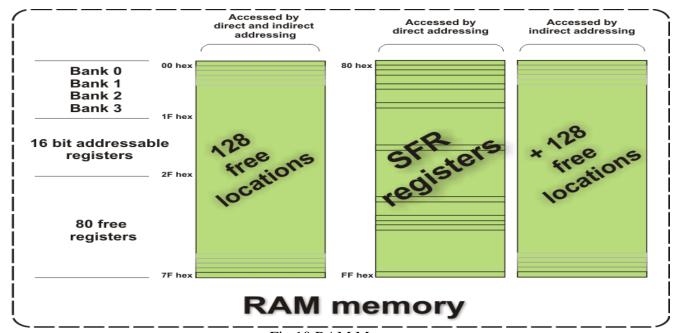

| 20 | Architecture of 8051 microcontroller                      | R(1)-page No.419-423                         | 2 |

| 21 | I/O and memory addressing                                 | R(2)-page No.73-77                           | 1 |

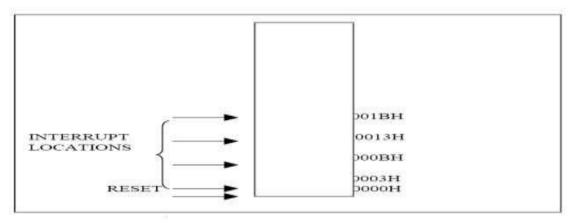

| 22 | Interrupts- Instruction set                               | R(1)-page No.465-470<br>R(1)-page No.494-516 | 2 |

| 23 | Addressing modes                                          | R(1)-page No.488-493                         | 1 |

|    | UNIT V PROGRAMMING AND<br>INTERFACING OF 8051             |                                              |   |

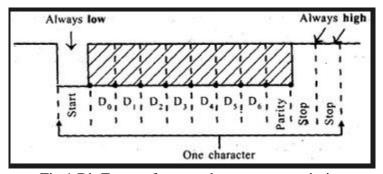

| 24 | Timer-Serial Communication of 8051                        | R(2)-page No.80-91                           | 2 |

| 25 | Interrupts Programming                                    | R(2)-page No.92-96                           | 1 |

| 26 | Interfacing to External Memory of 8051 micro controller   | R(2)-page No.78-80                           | 1 |

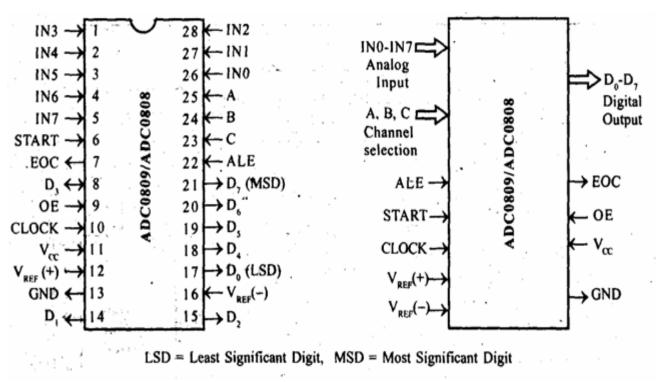

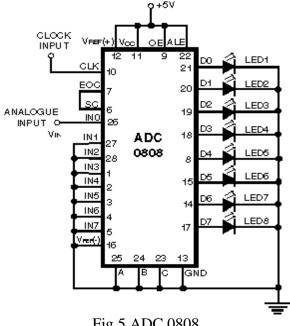

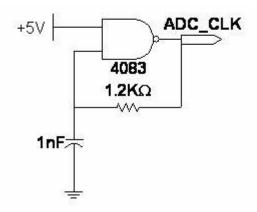

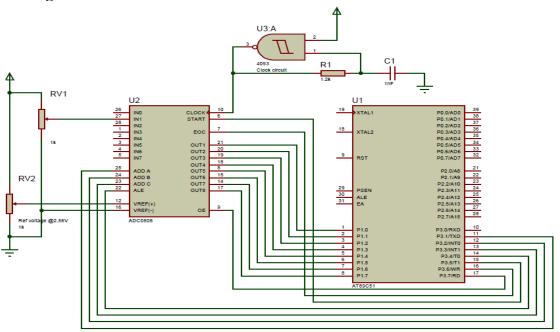

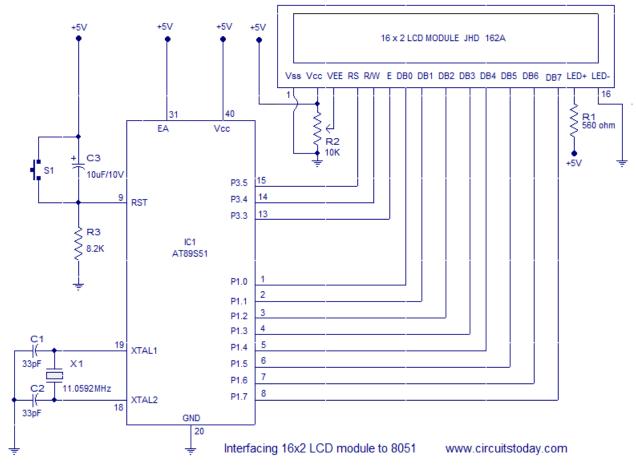

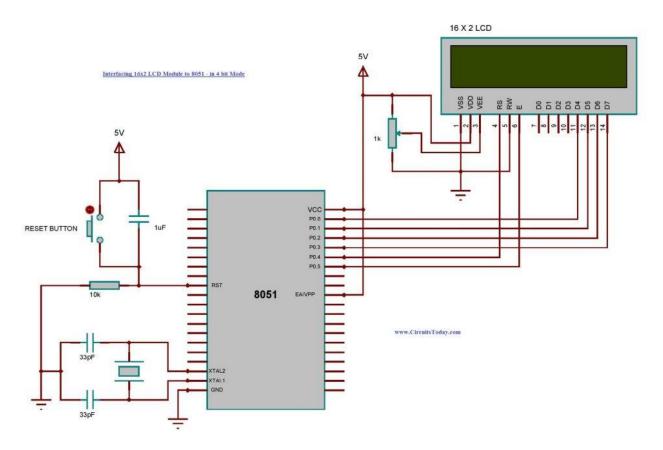

| 27 | Interfacing to ADC, LCD, DAC, Keyboard and stepper motor. | R(2)-page No.261-294<br>R(2)-page No.299-303 | 3 |

# **Text Books:**

1. Douglas V.Hall, Microprocessor and Interfacing: Programming and Hardware. Tata McGraw Hill, New Delhi 2007

# **References:**

- 1. Krishna Kant, Microprocessor and Microcontroller Architecture, programming and system design using 8085, 8086, 8051 and 8096, PHI, New Delhi, 2008

- 2. Kenneth J. Ayala, The 8051 Microcontroller, Thompson Delmar Learning, New Delhi, 2007

# UNIT1

### **MICROPROCESSOR-8086**

### Microprocessor-8086

Register Organization - Architecture-Signals-Memory Organization-Bus Operation-I/O Addressing Minimum Mode-Maximum Mode-Timing Diagram-Interrupts - Service Routines – I/O and Memory Interfacing concepts.

### 1.1 Register organization of 8086

8086 has a powerful set of registers containing general purpose and special purpose registers. All the registers of 8086 are 16-bit registers. The general purpose registers, can be used either 8-bit registers or 16-bit registers. The general purpose registers are either used for holding the data, variables and intermediate results temporarily or for other purpose like counter or for storing offset address for some particular addressing modes etc. The special purpose registers are used as segment registers, pointers, index registers or as offset storage registers for particular addressing modes. We will categorize the register set into four groups as follows:

# General data registers:

The registers AX, BX, CX, and DX are the general 16-bit registers.

## **AX Register:**

Accumulator register consists of two 8-bit registers AL and AH, which can be combined together and used as a 16-bit register AX. AL in this case contains the low-order byte of the word, and AH contains the high-order byte. Accumulator can be used for I/O operations, rotate and string manipulation.

### **BX Register:**

This register is mainly used as a base register. It holds the starting base location of a memory region within a data segment. It is used as offset storage for forming physical address in case of certain addressing mode.

## **CX Register:**

It is used as default counter or count register in case of string and loop instructions.

### **DX Register:**

Data register can be used as a port number in I/O operations and implicit operand or destination in case of few instructions. In integer 32-bit multiply and divide instruction the DX register contains high-order word of the initial or resulting number.

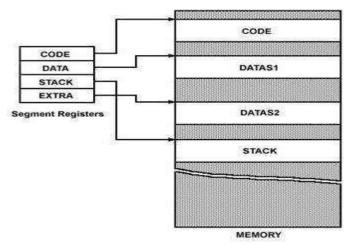

### **Segment registers:**

To complete 1Mbyte memory is divided into 16 logical segments. The complete 1Mbyte memory segmentation. Each segment contains 64Kbyte of memory. There are four segment registers.

### Code segment (CS)

It has 16-bit register containing address of 64 KB segment with processor instructions. The processor uses CS segment for all accesses to instructions referenced by instruction pointer (IP) register. CS register cannot be changed directly. The CS register is automatically updated during far jump, far call and far return instructions. It is used for addressing a memory location in the code segment of the memory, where the executable program is stored.

### **Stack segment (SS)**

is a 16-bit register containing address of 64KB segment with program stack. By default, the processor assumes that all data referenced by the stack pointer (SP) and base pointer (BP) registers is located in the stack segment. SS register can be changed directly using POP instruction. It is used for addressing stack segment of memory. The stack segment is that segment of memory, which is used to store stack data.

## Data segment (DS)

is a 16-bit register containing address of 64KB segment with program data. By default, the processor assumes that all data referenced by general registers (AX, BX, CX, DX) and index register (SI, DI) is located in the data segment. DS register can be changed directly using POP and LDS instructions. It points to the data segment memory where the data is resided.

### Extra segment (ES)

is a 16-bit register containing address of 64KB segment, usually with program data. By default, the processor assumes that the DI register references the ES segment in string manipulation instructions. ES register can be changed directly using POP and LES instructions. It also refers to segment which essentially is another data segment of the memory. It also contains data.

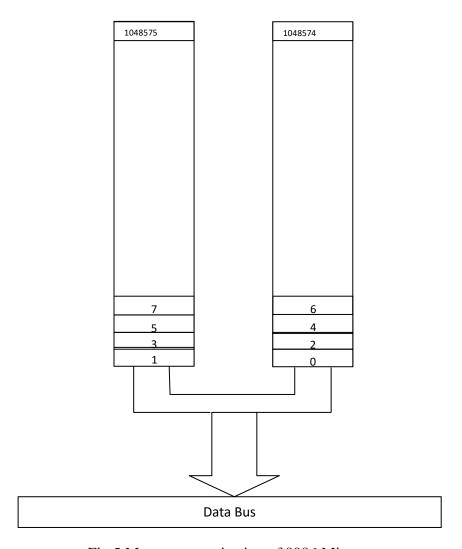

Fig.1 Memory Segmentation

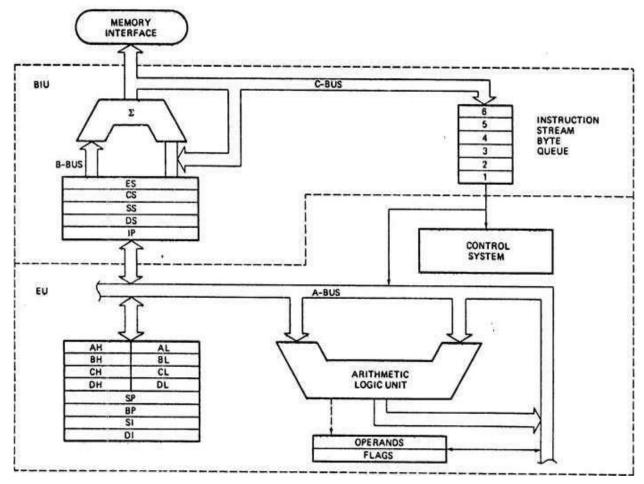

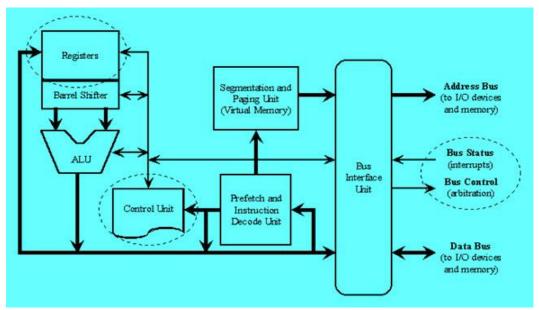

## 1.2 Architecture of 8086Microprocessor

#### **Features:**

- 1. Intel 8086 was launched in 1978.

- 2. It was the first 16-bitmicroprocessor.

- 3. This microprocessor had major improvement over the execution speed of 8085.

- 4. It is available as 40-pin Dual-Inline-Package(DIP).

- 5. It is available in three versions: a.8086 (5MHz)

b. 8086-2 (8 MHz)

c. 8086-1 (10 MHz)

6. It consists of 29,000transistors.

## **Bus Interface Unit (BIU):**

The function of BIU is to

- Fetch the instruction or data from memory.

- Write the data to memory.

- Write the data to the port.

- Read data from the port.

## **Instruction Queue**

- 1. To increase the execution speed, BIU fetches as many as six instruction bytes a head to time from memory.

- 2. All six bytes are then held in first in first out 6 byte register called instruction queue.

- 3. Then all bytes have to be given to EU one by one.

- 4. This pre fetching operation of BIU may be in parallel with execution operation of EU, which improves the speed execution of the instruction.

# **Execution Unit (EU)**

The functions of execution unit are

- ❖ To tell BIU where to fetch the instructions or data from.

- To decode the instructions.

- To execute the instructions.

The EU contains the control circuitry to perform various internal operations. A decoder in EU decodes the instruction fetched memory to generate different internal or external control signals required to perform the operation. EU has 16-bit ALU, which can perform arithmetic and logical operations on 8-bit as well as 16-bit.

# **Architecture of 8086 Microprocessor**

Fig.2 Architecture of 8086 Microprocessor

# **General Purpose Registers of 8086**

These registers can be used as 8-bit registers individually or can be used as 16-bit in pair to have AX,BX, CX, and DX.

**AX Register:** AX register is also known as accumulator register that stores operands for arithmetic operation like divided, rotate.

**BX Register:** This register is mainly used as a base register. It holds the starting base location of a memory region within a data segment.

CX Register: It is defined as a counter. It is primarily used in loop instruction to store loop counter.

**DX Register:** DX register is used to contain I/O port address for I/O instruction.

## **Segment Registers**

Additional registers called segment registers generate memory address when combined with other in the microprocessor. In 8086 microprocessor, memory is divided into 4 segments as follow:

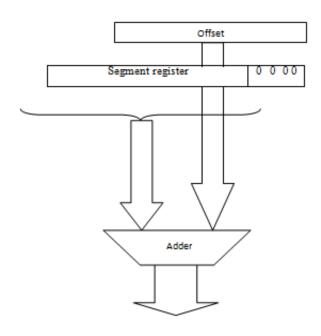

Fig.3 Segment Register of 8086 Microprocessor

**Code Segment (CS):** The CS register is used for addressing a memory location in the Code Segment of the memory, where the executable program is stored.

**Data Segment (DS):** The DS contains most data used by program. Data are accessed in the Data Segment by an offset address or the content of other register that holds the offset address.

**Stack Segment (SS):** SS defined the area of memory used for the stack.

**Extra Segment (ES):** ES is additional data segment that is used by some of the string to hold the destination data.

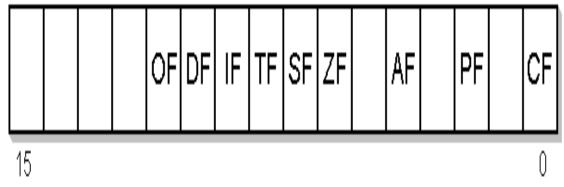

## Flag Registers of 8086

Fig.4 Flag register of 8086 Microprocessor

Flags Register determines the current state of the processor. They are modified automatically by CPU after mathematical operations, this allows to determine the type of the result, and to determine conditions to transfer control to other parts of the program. 8086 has 9 flags and they are divided into two categories:

- 1. Conditional Flags

- 2. Control Flags

# (1) Conditional Flags

Conditional flags represent result of last arithmetic or logical instruction executed. Conditional flags are as follows:

### Carry Flag (CF)

This flag indicates an overflow condition for unsigned integer arithmetic. It is also used in multiple-precision arithmetic.

### **Auxiliary Flag (AF):**

If an operation performed in ALU generates a carry/barrow from lower nibble (i.e.  $D_0$   $D_3$ ) to upper nibble (i.e.  $D_4 - D_7$ ), the AF flag is set i.e. carry given by  $D_3$  bit to  $D_4$  is AF flag. This is not a general-purpose flag, it is used internally by the processor to perform Binary to BCD conversion.

## Parity Flag (PF):

This flag is used to indicate the parity of result. If lower order 8-bits of the result contains even number of 1"s, the Parity Flag is set and for odd number of 1"s, the Parity Flag is reset.

### Zero Flag (ZF):

It is set; if the result of arithmetic or logical operation is zero else it is reset.

#### Sign Flag (SF):

In sign magnitude format the sign of number is indicated by MSB bit. If the result of operation is negative, sign flag is set.

#### Overflow Flag (OF):

It occurs when signed numbers are added or subtracted. An OF indicates that the result has exceeded the capacity of machine.

### 2.Control Flags

Control flags are set or reset deliberately to control the operations of the execution unit.

Control flags are as follows:

## 1.Trap Flag(TP):

a. It is used for single step control.

b. It allows user to execute one instruction of a program at a time for debugging.

c. When trap flag is set, program can be run in single step mode.

## 2.Interrupt Flag(IF):

- a. It is an interrupt enable/disable flag.

- b. If it is set, the maskable interrupt of 8086 is enabled and if it is reset, the interrupt is disabled.

- c. It can be set by executing instruction sit and can be cleared by executing CLI instruction.

### **3.Direction Flag (DF):**

- a. It is used in string operation.

- b. If it is set, string bytes are accessed from higher memory address to lower memory address.

When it is reset, the string bytes are accessed from lower memory address to higher memory address.

## 1.3 Signal Description of 8086 Microprocessor

The 8086 Microprocessor is a 16-bit CPU available in 3 clock rates, i.e. 5, 8 and 10MHz, packaged in a 40 pin CERDIP or plastic package. The 8086 Microprocessor operates in single processor or multiprocessor configurations to achieve high performance. The pin configuration is as shown in fig1. Some of the pins serve a particular function in minimum mode (single processor mode) and others function in maximum mode (multiprocessor mode) configuration.

The 8086 signals can be categorized in three groups. The first are the signals having common functions in minimum as well as maximum mode, the second are the signals which have special functions in minimum mode and third are the signals having special functions for maximum mode. The following signal description are common for both the minimum and maximum modes.

#### **AD15-AD0:**

These are the time multiplexed memory I/O address and data lines. Address remains on the lines during T1 state, while the data is available on the data bus during T2, T3, TW and T4. Here T1, T2, T3, T4 and TW are the clock states of a machine cycle. TW is await state. These lines are active high and float to a tristate during interrupt acknowledge and local bus hold acknowledge cycles.

## A19/S6, A18/S5, A17/S4, A16/S3:

These are the time multiplexed address and status lines. During T1, these are the most significant address lines or memory operations. During I/O operations, these lines are low. During memory or I/O operations, status information is available on those lines for T2, T3, TW and T4. The status of the interrupt enable flag bit(displayed on S5) is updated at the beginning of each clock cycle. The S4 and S3 combined indicate which segment register is presently being used for memory accesses as shown in Table 1

These lines float to tri-state off (tristate) during the local bus hold acknowledge. The status line S6 is always low(logical). The address bits are separated from the status bits using latches controlled by the ALE signal.

KARPAGAM ACADEMY OF HIGHER EDUCATION

Table 1

| S4 | S3 | Indication     |

|----|----|----------------|

| 0  | 0  | Alternate Data |

| 0  | 1  | Stack          |

| 1  | 0  | Code or none   |

| 1  | 1  | Data           |

BHE /S<sub>7</sub> – Bus High Enable /Status:

The bus high enable signal is used to indicate the transfer of data over the higher order (D15-D8) data bus as shown in Table 2. It goes low for the data transfers over D15-D8 and is used to derive chip selects of odd address memory bank or peripherals.  $\overline{BHE}$  is low during T1 for read, write and interrupt acknowledge cycles, when- ever a byte is to be transferred on the higher byte of the data bus. The status information is available during T2, T3 and T4. The signal is active low and is tristated during 'hold'. It is low during T1 for the first pulse of the interrupt acknowledge cycle.

Table 2

| ВНЕ | $\mathbf{A_0}$ | Indication                         |

|-----|----------------|------------------------------------|

| 0   | 0              | Whole Word                         |

| 0   | 1              | Upper byte from or to odd address  |

| 1   | 0              | Upper byte from or to even address |

| 1   | 1              | None                               |

RD - Read: Read signal, when low, indicates the peripherals that the processor is performing a memory or I/O read operation.  $\overline{RD}$  is active low and shows the state for T2, T3, TW of any read cycle. The signal remains tristated during the 'hold acknowledge'.

### **READY:**

This is the acknowledgement from the slow devices or memory that they have completed the data transfer. The signal made available by the devices is synchronized by the 8284A clock generator to provide ready input to the 8086. The signal is active high.

# **INTR-interrupt Request:**

This is a level triggered input. This is sampled during the last clock cycle of each instruction to determine the availability of the request. If any interrupt request is pending, the processor enters the interrupt acknowledge cycle. This can be internally masked by resetting the interrupt enable flag. This signal is active high and internally synchronized.

KARPAGAM ACADEMY OF HIGHER EDUCATION

#### **TEST:**

This input is examined by a 'WAIT' instruction. If the TEST input goes low, execution will continue, else, the processor remains in an idle state. The input is synchronized internally during each clock cycle on leading edge of clock.

## **NMI-Non-maskable Interrupt:**

This is an edge-triggered input which causes a Type2 interrupt. The NMI is not maskable internally by software. A transition from low to high initiates the interrupt response at the end of the current instruction. This input is internally synchronized.

#### **RESET:**

This input causes the processor to terminate the current activity and start execution from FFFF0H. The signal is active high and must be active for at least four clock cycles. It restarts execution when the RESET returns low. RESET is also internally synchronized.

## **CLK-Clock Input:**

The clock input provides the basic timing for processor operation and bus control activity. Its an asymmetric square wave with 33% duty cycle. The range of frequency for different 8086 versions is from 5MHz to 10MHz.

#### VCC:

+5V power supply for the operation of the internal circuit. GND ground for the internal circuit.

#### MN/MX:

The logic level at this pin decides whether the processor is to operate in either minimum (single processor) or maximum (multiprocessor) mode. The following pin functions are for the minimum mode operation of 8086.

## M/IO -Memory/IO:

This is a status line logically equivalent to S2 in maximum mode. When it is low, it indicates the CPU is having an I/O operation, and when it is high, it indicates that the CPU is having a memory operation. This line becomes active in the previous T4 and remains active till final T4 of the current cycle. It is tristated during local bus "hold acknowledge".

# INTA - Interrupt Acknowledge:

This signal is used as a read strobe for interrupt acknowledge cycles. In other words, when it goes low, it means that the processor has accepted the interrupt. It is active low during T2, T3 and TW of each interrupt acknowledge cycle.

#### **ALE-Address latch Enable:**

This output signal indicates the availability of the valid address on the address/data lines, and is connected to latch enable input of latches. This signal is active high and is never tristated.

# $\overline{DT/R}$ -Data Transmit/Receive:

This output is used to decide the direction of data flow through the transreceivers (bidirectional buffers). When the processor sends out data, this signal is high and when the processor is receiving data, this signal is low. Logically, this is equivalent to S1 in maximum mode. Its timing is the same as M/I/O. This is tristated during 'hold acknowledge'.

DEN - Data Enable

This signal indicates the availability of valid data over the address/data lines. It is used to enable the transreceivers (bidirectional buffers) to separate the data from the multiplexed address/data signal. It is active from the middle of T2 until the middle of T4 DEN is tristated during 'hold acknowledge' cycle.

### 1.4 8086 Memory Organization

### **Segmented Memory**

Two types of memory organization are used:

- Linear addressing where the entire memory is available to the processor at all the times (Motorola 68000family).

- Segmented addressing where the memory space is divided into several segments and the processor is limited to access program instructions and data in specific segments.

## 8086 Memory Organization

Each memory location 8086 is a byte while the 8086 is a 16-bits microprocessor? Many of the 8086 's operation codes are single bytes. I/O devices like printers, terminals and modems are designed to transfer ASCII encoded data. The 8086 has a 20-bits address bus, allowing to access a memory of  $2^{20} = 1$  M locations.

Fig.5 Memory organization of 8086 Microprocessor

### **Segment Registers**

Within the 1MB of memory space, the 8086 defines four 64 K memory blocks: The code segment, stack segment, data segment, extra segment.

Each of these blocks of memory is used differently by the processor.

- The code segment holds the program instruction codes.

- The data segment holds the data of the program.

- The extra segment is an extra data segment (often used for shared data).

- The stack segment is used to store interrupt and subroutine return addresses.

There are four segment registers CS, DS, ES and SS and each of them defines the starting address of the corresponding segment. Each segment register is 16 bits wide while the address bus is 20 bits wide. The BIU takes care of this by appending four 0s to the low order bits of the segment register.

# **Logical and Physical Addresses**

Addresses within a segment cab be ranged from address 0 to address FFFh. This correspond to the 64K length of the segment. An address within a segment is called an offset or logical address. For example, logical address 20h in the code segment shown above actually correspond to the real address E0000h+ 20h= E0020h. this real address is called the physical address. Physical address is the 20 bits address that being output bus the BIU on the address bus.

| Types of memory    | Default Segment | Alternate Segment | Offset (Logical   |

|--------------------|-----------------|-------------------|-------------------|

| Reference          |                 |                   | Address)          |

| Instruction fetch  | CS              | None              | IP                |

| Stack operation    | SS              | None              | SP                |

| General data       | DS              | CS, ES, SS        | Effective address |

| String source      | DS              | CS, ES, SS        | SI                |

| String destination | ES              | None              | DI                |

| BX used as pointer | DS              | CS, ES, SS        | Effective address |

| BP used as pointer | SS              | CS, ES, SS        | Effective address |

### 1.9 8086 interrupt

#### Introduction

An interrupt is the method of processing the microprocessor by peripheral device. An interrupt is used to cause a temporary halt in the execution of program. Microprocessor responds to the interrupt with an interrupt service routine, which is short program or subroutine that instructs the microprocessor on how to handle the interrupt.

There are two basic type of interrupt, maskable and non-maskable, non-maskable interrupt requires an immediate response by microprocessor, it usually used for serious circumstances like power failure. A maskable interrupt is an interrupt that the microprocessor can ignore depending upon some predetermined upon some predetermined condition defined by status register.

Interrupt can divide to five group:

- 1. hardware interrupt

- 2. Non-maskable interrupt

- 3. Software interrupt

- 4. Internal interrupt

- 5. Reset

Hardware, software and internal interrupt are service on priority basis. each interrupt is given a different priority level by assign it a type number. Type 0 identifies the highest-priority and type 255 identifies the lowest-priority interrupt.

The 80x86 chips allow up to 256 vectored interrupts. This means that you can have up to 256 different sources for an interrupt and the 80x86 will directly call the service routine for that interrupt without any software processing. This is in contrast to non vectored interrupts that transfer control directly to a single interrupt service routine, regardless of the interrupt source.

The 80x86 provides a 256 entry interrupt vector table beginning at address 0:0 in memory. This is a 1K table containing 256 4-byte entries. Each entry in this table contains a segmented address that points at the interrupt service routine in memory. The lowest five types are dedicated to specific interrupts such as the divide by zero interrupt and thenonmaskableinterrupt. Thenext27 interrupt types, from 50 1 are reserved by Intel for use in future microprocessors. The upper 224 interrupt types, from 32 to 255, are available to use for hardware and software interrupts.

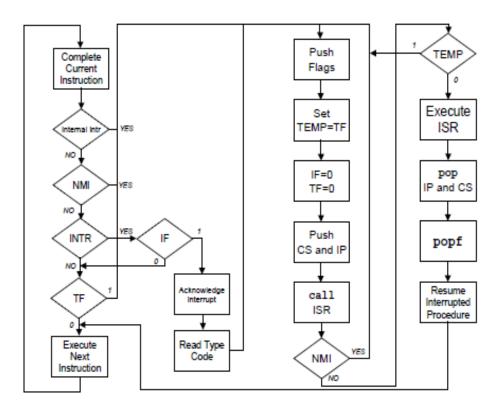

When an interrupt occurs (shown in figure 6), regardless of source, the 80x86 does the following:

- 1. The CPU pushes the flags register onto the stack.

- 2. The CPU pushes a far return address (segment: offset) onto the stack, segment value first.

- 3. The CPU determines the cause of the interrupt (i.e., the interrupt number) and fetches the four byte interrupt vector from address 0:vector\*4.

- 4. The CPU transfers control to the routine specified by the interrupt vector table entry.

Fig.6 block diagram to interrupt handle

When the interrupt service routine wants to return control, it must execute an IRET (interrupt return) instruction. The interrupt return pops the far return address and the flags off the stack. Note that executing a far return is insufficient since that would leave the flags on the stack.

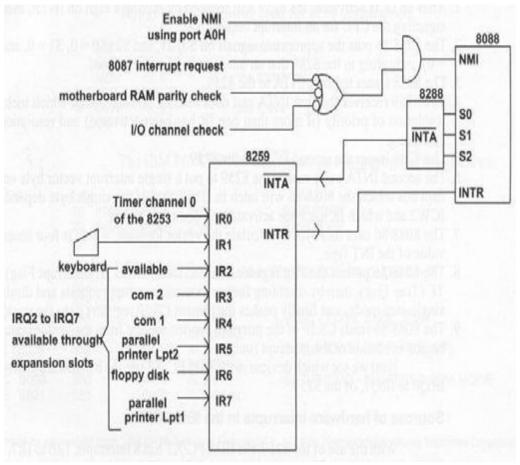

## **Hardware interrupt**

The primary sources of interrupts, however, are the PCs timer chip, keyboard, serial ports, parallel ports, disk drives, CMOS real-time clock, mouse, sound cards, and other peripheral devices. These devices connect to an Intel 8259A programmable interrupt controller (PIC) that prioritizes the interrupts and interfaces with the 80x86 CPU. The 8259A chip adds considerable complexity to the software that processes interrupts.

## programmable interrupt controller

The 8259A programmable interrupt controller chip accepts interrupts from up to eight different devices, which shown in figure (2), If any one of the devices requests service, the 8259 will toggle an interrupt output line (connected to the CPU) and pass a programmable interrupt vector to the CPU. You can cascade ( show in figure(3))the device to support up to 64 devices by connecting nine 8259s together: eight of the devices with eight inputs each whose outputs become the eight inputs of the ninth device. A typical PC uses two of these devices to provide 15 interrupt inputs (seven on the master PIC with the eight input coming from the slave PIC to process its eight inputs)7. The sections following this one will describe the devices connected to each of those inputs, for now we will concentrate on what the 8259 does with those inputs. Nevertheless, for the sake of discussion, the following table lists the interrupt sources on the PC:

Fig.7general block diagram 8086 interrupt

## NON-MASKABLE INTERRUPT(NMI)

The processor provides a single non-maskable interrupt pin (NMI) which has higher priority than the maskable interrupt request pin (INTR). A typical use would be to activate a power failure routine. The NMI is edge- triggered on a LOW-to-HIGH transition. The activation of this pin causes a type 2 interrupt. NMI is required to have a duration in the HIGH state of greater than two CLK cycles, but is not required to be synchronized to the clock. Any high-going transition of NMI is latched on-chip and will be serviced at the end of the current instruction or between whole moves of a block-type instruction. Worst case response to NMI would be for multiply, divide, and variable shift instructions. There is no specification on the occurrence of the low-going edge; it may occur before, during, or after the servicing of NMI. Another

high-going edge triggers another response if it occurs after the start of the NMI procedure. The signal must be free of logical spikes in general and be free of bounces on the low-going edge to avoid triggering extraneous responses.

## **MASKABLEINTERRUPT**

Whenever an external signal activates the INTR pin, the microprocessor will be interrupted only if interrupts are enabled using set interrupt Flag instruction. If the interrupts are disabled using clear interrupt Flag instruction, the microprocessor will not get interrupted even if INTR is activated. That is, INTR can be masked. INTR is a non vectored interrupt, which means, the 8086 does not know where to branch to service the interrupt. The 8086 has to be told by an external device like a Programmable Interrupt controller regarding the branch. Whenever the INTR pin is activated by an

I/O port, if Interrupts are enabled and NMI is not active at that time, the microprocessor finishes the current instruction that is being executed and gives out a '0' on INTA pin twice. When INTA pin goes low for the first time, it asks the external device to get ready. In response to the second INTA the microprocessor receives the 8 bit, say N, from a programmable Interrupt controller. The action taken is as follows.

- 1. Complete the current instruction.

- 2. Activates INTA output, and receives type Number, sayN

- 3. Flag register value, CS value of the return address & IP value of the return address are pushed on to the stack.

- 4. IP value is loaded from contents of word location N x4.

- 5. CS is loaded from contents of the next word location.

- 6. 2Interrupt Flag and trap Flag are reset to 0.

At the end of the ISS, there will be an IRET instruction. This performs popping off from the stack top to IP, CS and Flag registers. Finally, the register values which are also saved on the stack at the start of ISS, are restored from the stack and a return to the interrupted program takes place using the IRET instruction.

Table 1:type of interrupt

| Vector No. | Mnemonic | Description                                   | Source                                                              |

|------------|----------|-----------------------------------------------|---------------------------------------------------------------------|

| 0          | #DE      | Divide Error                                  | DIV and IDIV instructions.                                          |

| 1          | #DB      | Debug                                         | Any code or data reference.                                         |

| 2          |          | NMI Interrupt                                 | Non-maskable external interrupt.                                    |

| 3          | #BP      | Breakpoint                                    | INT 3 instruction.                                                  |

| 4          | #OF      | Overflow                                      | INTO instruction.                                                   |

| 5          | #BR      | BOUND Range Exceeded                          | BOUND instruction.                                                  |

| 6          | #UD      | Invalid Opcode (UnDefined Opcode)             | UD2 instruction or reserved opcode. <sup>1</sup>                    |

| 7          | #NM      | Device Not Available (No Math<br>Coprocessor) | Floating-point or WAIT/FWAIT instruction.                           |

| 8          | #DF      | Double Fault                                  | Any instruction that can generate an exception, an NMI, or an INTR. |

| Vector No. | Mnemonic | Description                            | Source                                                            |

|------------|----------|----------------------------------------|-------------------------------------------------------------------|

| 9          |          | CoProcessor Segment Overrun (reserved) | Floating-point instruction. <sup>2</sup>                          |

| 10         | #TS      | Invalid TSS                            | Task switch or TSS access.                                        |

| 11         | #NP      | Segment Not Present                    | Loading segment registers or accessing system segments.           |

| 12         | #SS      | Stack Segment Fault                    | Stack operations and SS register loads.                           |

| 13         | #GP      | General Protection                     | Any memory reference and other protection checks.                 |

| 14         | #PF      | Page Fault                             | Any memory reference.                                             |

| 15         |          | (Intel reserved. Do not use.)          |                                                                   |

| 16         | #MF      | Floating-Point Error (Math Fault)      | Floating-point or WAIT/FWAIT instruction                          |

| 17         | #AC      | Alignment Check                        | Any data reference in memory. <sup>3</sup>                        |

| 18         | #MC      | Machine Check                          | Error codes (if any) and source are model dependent. <sup>4</sup> |

| 19-31      |          | (Intel reserved. Do not use.)          |                                                                   |

| 32-255     |          | Maskable Interrupts                    | External interrupt from INTR pin or INT <i>n</i> instruction.     |

- 1. The UD2 instruction was introduced in the Pentium® Pro processor.

- Intel Architecture processors after the Intel386™ processor do not generate this exception.

- This exception was introduced in the Intel486<sup>™</sup> processor.

- 4. This exception was introduced in the Pentium processor and enhanced in the Pentium Pro processor.

## **Software interrupt Instructions**

There are instructions in 8086 which cause an interrupt. They are

- INT instructions with type number specified.

- INT 3, Break Point Interrupt instruction.

- INTO, Interrupt on overflow instruction.

These are instructions at the desired places in a program. When one of these instructions is executed a branch to an ISS takes place. Because their execution results in a branch to an ISS, they are called interrupts. Software Interrupt instructions can be used to test the working of the various Interrupt handlers- For example, we can execute INTO instruction to execute type 0 ISS, without really having to divide a number by 0. Similarly, we can execute INT 2 instruction to test NMIISS.

## **INT-Interrupt Instruction with Type number Specified**

The mnemonic for this is INT. It is a 2 byte instruction. The first byte provides the op-code and

the second byte the Interrupt type number. Op-code for this instruction is CDH The execution of an INT instruction, say INTN, when N is the value in the range 00H to FFH, results in the following:

- 1. Flag register value is pushed on to the stack.

- 2. CS value of the Return address and IP value of the Return address are pushed on to the stack.

- 3. IP is loaded from the contents of the word location N x4.

- 4. CS is loaded from the contents of the next word location.

- 5. Interrupt Flag and Trap Flag are reset to 0.

Thus a branch to the ISS take place. During the ISS, interrupt are disabled because the Interrupt flag is reset to 0.At the end of the ISS, there will be an IRET instruction. Thus a return back to the interrupted program takes place with Flag registers unchanged.

## **INT 3-Break Point Interrupt Instruction**

When a break point is inserted, the system executes the instructions up to the breakpoint, and then goes to the break point procedure. Unlike the single-Step feature which stops execution after each instruction, the breakpoint feature executes all the instructions up to the inserted breakpoint and then stops execution. The mnemonic for the instruction is INT3. It is a 1 byte instruction Op-code for this is CCH.

The execution of INT3 instruction results in the following.

- 1. Flag register value is pushed on to the Stack.

- 2. CS value of the return address and IP value of the return address are pushed onto the Stack.

- 3. IP is loaded from the contents of the word location 3x4 = 0000CH.

- 4. CS is loaded from the contents of the next word location.

- 5. Interrupt Flag and Trap Flag are reset to 0.

Thus a branch to the ISS takes place. During the ISS, interrupts are disabled because Interrupt flag is reset to 0. At the end of the ISS, there will be an IRET instruction to return back to the interrupted program. A break point interrupt service procedure usually saves all the register contents on the Stack. Depending upon the system, it may then send the

register contents to the CRTdisplay and wait for the next command from the user.

# INTO - Interrupt on over flow instruction

The 8086 overflow flag, OF, will be set if the signed result of an arithmetic operation on two signed numbers is too large to be represented in the destination register or memory location. For example, if we add the 8-bit signed number 01101100 and the 8- bit signed number 01010001, the signed result will be 10111101. This is correct if we add unsigned binary numbers, but it is not the correct signed result. There are two ways to detect and respond to an overflow error in a program. One way is to put the jump if overflow instruction, JO, immediately after the arithmetic instruction. If the overflow flag is Set, execution will jump to the address specified in the JO instruction. At this address an error routine may be put which respond to the overflow. The second way is to put them INTO instruction immediately after the arithmetic Instruction in the program. The mnemonic for the instruction is INTO. It is a 1 byte instruction. The op-code for this is CEH. It is a conditional interrupt instruction. Only if the overflow flag is Set, a branch takes place to an interrupt handler whose interrupt type

number is 4. If the overflow flag is reset, the execution continues with the next instruction. The execution of INTO results in the following.

- 6.Flag register values are pushed on to the Stack.

- 7.CS value of the return address and IP value of the return address and IP value of the return address are pushed on to the stack.

- 8.IP is loaded from the contents of word location 4x4 = 00010H.

- 9.CS is loaded from the contents of next word location.

- 10. Interrupt flag and Trap flag are reset to 0.

Thus a branch to ISS takes place. During the ISS, interrupts are disabled. At the end of ISS, there will be an IRET instruction, returning back to the interrupted program. Instructions in the ISS procedure perform the desired response to the error condition.

### 11. RESET

Processor initialization or start up is accomplished with activation (HIGH) of the RESET pin which it shows in table (2). The 8086 RESET is required to be HIGH for greater than 4 CLK cycles. The 8086 will terminate operations on the high-going edge of RESET and will remain dormant as long as RESET is HIGH. The low-going transition of RESET triggers an internal reset sequence for approximately 10 CLK cycles. After this interval the 8086 operates normally beginning with the instruction in absolute location FFFF0H.

Table 2:process initialization register content

| CPU Asset         | Content |

|-------------------|---------|

| FLAGS Register    | 0000h   |

| IP                | 0000h   |

| CS                | ffffh   |

| DS                | 0000h   |

| 88                | 0000h   |

| ES                | 0000h   |

| Instruction Queue | Empty   |

### 1.11 I/O Interfacing Techniques

Input/output devices can be interfaced with microprocessor systems in two ways:

- 1. I/O mapped I/O

- 2. Memory mapped I/O

## 1. I/O mapped I/O:

8086 has special instructions IN and OUT to transfer data through the input/output ports in I/O mapped I/O system. The IN instruction copies data from a port to the Accumulator. If an 8-bit port is read data will go to AL and if 16-bit port is read the data will go to AX. The OUT instruction copies a byte from AL or a word from AX to the specified port. The M/IO signal is always low when 8086 is executing these instructions. In this address of I/O device is 8-bit or 16-bit. It is 8-bit for Direct addressing and 16-bit for Indirect addressing.

### 2. Memory mapped I/O

In this type of I/O interfacing, the 8086 uses 20 address lines to identify an I/O device. The I/O device is connected as if it is a memory device. The 8086 uses same control signals and instructions to access I/O as those of memory, here RD and WR signals are activated indicating memory bus cycle.

#### **Problem:**

Interface an input port 74LS245 to read the status of the switches SW1 to SW8. the switches when shorted, input a '1' else input a '0' to the microprocessor system. Store the status in register BL. The address of the port is 0740H

### **Solution:**

The hardware interface circuit is shown in figure. The address, control and data lines are assumed to be readily available at the microprocessor system The ALP is given as follows:

MOV BL, 00H; clear BL for status

MOV DX, 0740H; 16-bit Port address in DX IN AL,DX; Read Port 0740H for switch positions.

MOV BL, AL; Store status of switches from AL into BL

HLT; Stop

### **Problem:**

Design an interface of input port 74LS245 to read the status of switches SW1 to SW8 and output port 74LS373 with 8086. display the number of key that is pressed with the help of output port on 7 segment display.

**Solution**: Status of the switches is first read into the AL. Displaying the shorted switch number in the 7 segment display. Instead of using 16 address lines, one may use only A3– A0.

## **QUESTION BANK**

### PART - B (16 MARKS)

- 1. Explain the internal hardware architecture of 8086 microprocessor with neat diagram?

- 2. Write short note about assembler directives?

- 3. Write a note about stack, procedures and macros?

- 4. Define interrupt and their two classes? Write in detail about interrupt service routine?

- 5. Explain byte and string manipulation with examples?

- 6. Write an ALP to find the largest number and smallest number in the array?

- 7. Explain the Architecture of 8086 microprocessor with neat diagram

- 8. With a neat sketch describe the Minimum and Maximum mode of operation of 8086.

- 9. Discuss in detail the various signals of 8086.

- 10. Write short notes on addressing memory.

- 11. Write notes on addressing input and output devices?

- 12. Explain in detail about 8086 memory banks and associated signals for byte and word operations.

- 13. Explain about System Bus Structure with suitable timing diagram.

- 14. Discuss in detail about Interrupt Priority Management.

- 15. Explain the various Bus Arbitration Schemes.

- 16. Draw the bus cycle timing diagram for I/O read and I/O write in minimum mode for 8086 processor.

- 17. Describe the functional block diagram of 8086 Microprocessor with register Organization.

- 18. Draw the bus cycle timing diagram for I/O read and I/O write in maximum mode for 8086 processor.

- 19. Draw the bus cycle timing diagram for the memory read and memory write in minimum mode for 8086

- 20. i) Explain external memory addressing.

- ii) Draw timing diagram of

- (i) 16 bit Read at odd address 0A2F8H 0BC07H.

- (ii) 8 bit Read at odd address 0A2F7H.

- (iii) 16 bit Read at even address 0A2F7H 0A2F8H.

- 21. Explain in 8086 signals and timing in detail with neat diagram.

- 22. Explain in detail about the minimum and maximum mode configurations of 8086.

- 23. Why 8086 is called a pipelined processor justify.

- 24. Explain external memory addressing.

- 25. Draw the bus cycle timing diagram for the memory read and memory write in maximum mode for 8086

# **UNIT II**

#### PROGRAMMING OF 8086

### **Programming of 8086**

Addressing Modes-Instruction format-Instruction set-Assembly language programs in 8086. RISC architecture – introduction to ARM Programming-register configuration and instruction set – sample program.

#### 2.1 8086 ADDRESSING MODES:

Addressing modes refers to the mechanism by which the operands are specified for an operation. Depending on the type of operands used, there are 7 addressing modes available.

### 1. Immediate Mode:

In this mode, the instruction contains 8-bit or 16-bit immediate data along with the mnemonic. Data can be moved to 8-bit or 16-bit register, or memory location using the address or register.

| Instruction    |  |

|----------------|--|

| Operand (8-    |  |

| bit or 16-bit) |  |

Ex: MOV AX,1234 h, ANDAL,3FH, M

MOV DX,0ABCDH

MOV[2000h],25 MOV AL,3373(invalid), MOV DS, 1234(invalid)

Note: a) Any data must start with a decimal digit (0 to 9). Hex digits A to F are treated as characters. So, Hex nos must be prefixed with a Zero. (Ex: MOV CL, 0A2H)

- b) Immediate data cannot be copied into Segment registers.

- c) Size of the data (byte or word) must match the size of registers (8-bit or 16-bit)

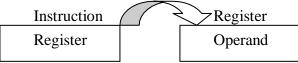

## 2. Register Mode:

In this mode, the operands are available in general purpose registers. Instruction specifies the register name.

$\mbox{Ex:} \quad \mbox{MOVCL,DL} \quad ; \quad \mbox{ADD BL,AL}; \quad \mbox{MOV AX, CL(invalid)}$

XOR CX, DX ; DECBX ;

### **Memory Operands:**

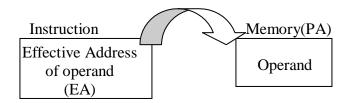

#### 3. Direct Mode:

Here, the instruction contains 16-bit offset (Effective address) (EA) of the memory location.

The Physical Address (PA) is calculated by 8086 using EA and Segment Register; and then the operand will be fetched from memory. Default register is DS.

PA = EA + (DS \* 10H)

Ex: MOVBL,NUM ; MOV[3455H],AL ; MOV CX, ES: 20h, MOV NUM2,CX

#### 4. Indirect Modes

8086 provides many indirect addressing modes (where one operand is in memory) which are extensively used in programming.

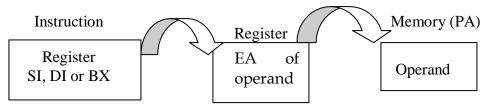

## a) Register Indirect Mode:

In this mode, the instruction contains a 16-bit register name which contains the EA. Using this EA, PA is calculated. Default segment register for memory is DS. Only BX, SI and DI

register can be used to hold the EA.

Ex: MOV AL, BYTE PTR [BX]; INC <u>WORD PTR</u> [DI], **MOV [BX], [SI] (invalid)**MUL <u>BYTE PTR</u> [SI]; AND CX, WORD PTR [BX], MOV BYTE PTR [BX], 50h **ADD CX, [AX](invalid)**

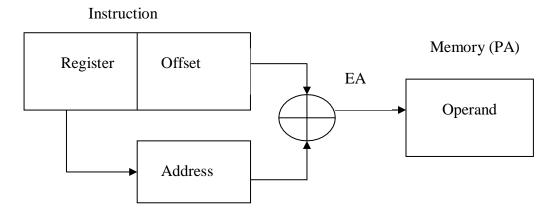

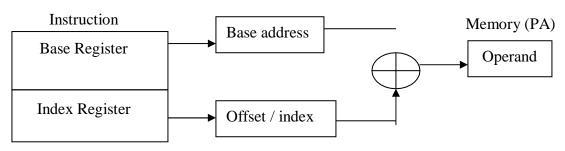

### b) Register Relative Mode or Indexed Mode: (Register Indirect with Displacement)

In this mode, the instruction contains a 16-bit register name (which contains an address) and a signed displacement. Adding the register contents with displacement gives the EA. Using this EA, PA is calculated. Default segment register for memory is DS. Only BX, SI, DI and BP register can be used.

$$PA = EA + (DS * 10H)$$

$$EA = \begin{cases} (BX) \\ (BP) \\ (SI) \\ (DI) \end{cases} + \begin{cases} 8 \text{-bit displacement(sign-extended)} \\ \text{or} \\ 16 \text{- bit signed displacement)} \end{cases}$$

Ex: MOV AL, BYTE PTR 50 [BX]; DEC WORD PTR [DI+30] MOV 100H WORD PTR[BX],1224H; MOV CX, -22H[SI]

## c) Base plus Indexed Mode:

In this mode, the instruction contains a 16-bit Base register name (which contains the base address) and a 16-bit Index register name. Adding the contents of both registers, EA is obtained. Then, PA is calculated. Default segment register for memory is DS. Only BX, BP and SI, DI registers can be used.

$$EA = (BX)or(BP) + (SI) or(DI)$$

$$PA = EA + (DS * 10H)$$

Ex: MOV [BX][SI],1234H, SUB AL, BYTE PTR[BX][DI]

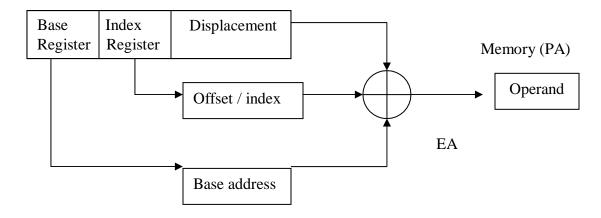

## d) Relative Based ñ Indexed Mode:

In this mode, the instruction contains a 16-bit Base register name (which contains the base address), a 16-bit Index register name and a displacement. Adding the contents of both registers along with the displacement, EA is obtained. Then, PA is calculated. Default segment register for memory is DS. Only BX, BP and SI, DI registers can be used.

### Instruction

$$EA = (BX) or (BP) + \left\{ \begin{array}{cc} (SI) or (DI) \\ \end{array} \right. + \left. \left\{ \begin{array}{cc} 8\text{-bit sign-extended displacement} \\ or 16\text{-bit signed displacement} \end{array} \right. \right.$$

PA = EA + (DS \* 10H)

Ex: MOV 50h [BX] [SI],1234H MOV -30H [BP] [SI],DX

# 2.2 Microprocessor - 8086 Instruction Sets

The 8086 microprocessor supports 8 types of instructions –

- Data Transfer Instructions

- Arithmetic Instructions

- Bit Manipulation Instructions

- String Instructions

- Program Execution Transfer Instructions (Branch & Loop Instructions)

- Processor Control Instructions

- Iteration Control Instructions

- Interrupt Instructions

#### **Data Transfer Instructions**

These instructions are used to transfer the data from the source operand to the destination operand. Following are the list of instructions under this group –

Instruction to transfer a word

• MOV – Used to copy the byte or word from the provided source to the provided destination.

- **PUSH** Used to put a word at the top of the stack.

- **POP** Used to get a word from the top of the stack to the provided location.

- **PUSH** Used to put all the registers into the stack.

- **POP** Used to get words from the stack to all registers.

- **XCHG** Used to exchange the data from two locations.

- **XLAT** Used to translate a byte in AL using a table in the memory.

# Instructions for input and output port transfer

- **IN** Used to read a byte or word from the provided port to the accumulator.

- **OUT** Used to send out a byte or word from the accumulator to the provided port.

### **Instructions to transfer the address**

- **LEA** Used to load the address of operand into the provided register.

- LDS Used to load DS register and other provided register from the memory

- **LES** Used to load ES register and other provided register from the memory.

## **Instructions to transfer flag registers**

- **LAHF** Used to load AH with the low byte of the flag register.

- **SAHF** Used to store AH register to low byte of the flag register.

- **PUSHF** Used to copy the flag register at the top of the stack.

- **POPF** Used to copy a word at the top of the stack to the flag register.

### **Arithmetic Instructions**

These instructions are used to perform arithmetic operations like addition, subtraction, multiplication, division, etc.

Following is the list of instructions under this group –

## **Instructions to perform addition**

- **ADD** Used to add the provided byte to byte/word to word.

- **ADC** Used to add with carry.

- **INC** Used to increment the provided byte/word by 1.

- **AAA** Used to adjust ASCII after addition.

- **DAA** Used to adjust the decimal after the addition/subtraction operation.

### **Instructions to perform subtraction**

- **SUB** Used to subtract the byte from byte/word from word.

- **SBB** Used to perform subtraction with borrow.

- **DEC** Used to decrement the provided byte/word by 1.

- NPG Used to negate each bit of the provided byte/word and add 1/2's complement.

- **CMP** Used to compare 2 provided byte/word.

- AAS Used to adjust ASCII codes after subtraction.

- **DAS** Used to adjust decimal after subtraction.

# **Instruction to perform multiplication**

- **MUL** Used to multiply unsigned byte by byte/word by word.

- **IMUL** Used to multiply signed byte by byte/word by word.

- **AAM** Used to adjust ASCII codes after multiplication.

## Instructions to perform division

- **DIV** Used to divide the unsigned word by byte or unsigned double word by word.

- **IDIV** Used to divide the signed word by byte or signed double word by word.

- **AAD** Used to adjust ASCII codes after division.

- **CBW** Used to fill the upper byte of the word with the copies of sign bit of the lower byte.

- **CWD** Used to fill the upper word of the double word with the sign bit of the lower word.

# **Bit Manipulation Instructions**

These instructions are used to perform operations where data bits are involved, i.e. operations like logical, shift, etc.

Following is the list of instructions under this group –

## **Instructions to perform logical operation**

- **NOT** Used to invert each bit of a byte or word.

- **AND** Used for adding each bit in a byte/word with the corresponding bit in another byte/word.

- **OR** Used to multiply each bit in a byte/word with the corresponding bit in another byte/word.

- **XOR** Used to perform Exclusive-OR operation over each bit in a byte/word with the corresponding bit in another byte/word.

- **TEST** Used to add operands to update flags, without affecting operands.

### **Instructions to perform shift operations**

- SHL/SAL Used to shift bits of a byte/word towards left and put zero(S) in LSBs.

- SHR Used to shift bits of a byte/word towards the right and put zero(S) in MSBs.

- **SAR** Used to shift bits of a byte/word towards the right and copy the old MSB into the new MSB.

# Instructions to perform rotate operations

- **ROL** Used to rotate bits of byte/word towards the left, i.e. MSB to LSB and to Carry Flag [CF].

- **ROR** Used to rotate bits of byte/word towards the right, i.e. LSB to MSB and to Carry Flag [CF].

- **RCR** Used to rotate bits of byte/word towards the right, i.e. LSB to CF and CF to MSB.

- **RCL** Used to rotate bits of byte/word towards the left, i.e. MSB to CF and CF to LSB.

## **String Instructions**

String is a group of bytes/words and their memory is always allocated in a sequential order.

Following is the list of instructions under this group –

- **REP** Used to repeat the given instruction till  $CX \neq 0$ .

- **REPE/REPZ** Used to repeat the given instruction until CX = 0 or zero flag ZF = 1.

- **REPNE/REPNZ** Used to repeat the given instruction until CX = 0 or zero flag ZF = 1.

- MOVS/MOVSB/MOVSW Used to move the byte/word from one string to another.

- **COMS/COMPSB/COMPSW** Used to compare two string bytes/words.

- **INS/INSB/INSW** Used as an input string/byte/word from the I/O port to the provided memory location.

- **OUTS/OUTSB/OUTSW** Used as an output string/byte/word from the provided memory location to the I/O port.

- SCAS/SCASB/SCASW Used to scan a string and compare its byte with a byte in AL or string word with a word in AX.

- **LODS/LODSB/LODSW** Used to store the string byte into AL or string word into AX.

## Program Execution Transfer Instructions (Branch and Loop Instructions)

These instructions are used to transfer/branch the instructions during an execution. It includes the following instructions –

## Instructions to transfer the instruction during an execution without any condition –

- CALL Used to call a procedure and save their return address to the stack.

- **RET** Used to return from the procedure to the main program.

- **JMP** Used to jump to the provided address to proceed to the next instruction.

## Instructions to transfer the instruction during an execution with some conditions –

- **JA/JNBE** Used to jump if above/not below/equal instruction satisfies.

- **JAE/JNB** Used to jump if above/not below instruction satisfies.

- **JBE/JNA** Used to jump if below/equal/ not above instruction satisfies.

- **JC** Used to jump if carry flag CF = 1

- **JE/JZ** Used to jump if equal/zero flag ZF = 1

- **JG/JNLE** Used to jump if greater/not less than/equal instruction satisfies.

- **JGE/JNL** Used to jump if greater than/equal/not less than instruction satisfies.

- **JL/JNGE** Used to jump if less than/not greater than/equal instruction satisfies.

- **JLE/JNG** Used to jump if less than/equal/if not greater than instruction satisfies.

- **JNC** Used to jump if no carry flag (CF = 0)

- **JNE/JNZ** Used to jump if not equal/zero flag ZF = 0

- **JNO** Used to jump if no overflow flag OF = 0

- **JNP/JPO** Used to jump if not parity/parity odd PF = 0

- **JNS** Used to jump if not sign SF = 0

- **JO** Used to jump if overflow flag OF = 1

- **JP/JPE** Used to jump if parity/parity even PF = 1

- **JS** Used to jump if sign flag SF = 1

### **Processor Control Instructions**

These instructions are used to control the processor action by setting/resetting the flag values.

Following are the instructions under this group –

- STC Used to set carry flag CF to 1

- **CLC** Used to clear/reset carry flag CF to 0

- **CMC** Used to put complement at the state of carry flag CF.

- **STD** Used to set the direction flag DF to 1

- **CLD** Used to clear/reset the direction flag DF to 0

- **STI** Used to set the interrupt enable flag to 1, i.e., enable INTR input.

- **CLI** Used to clear the interrupt enable flag to 0, i.e., disable INTR input.

#### **Iteration Control Instructions**

These instructions are used to execute the given instructions for number of times. Following is the list of instructions under this group –

- **LOOP** Used to loop a group of instructions until the condition satisfies, i.e., CX = 0

- **LOOPE/LOOPZ** Used to loop a group of instructions till it satisfies ZF = 1 & CX = 0

- **LOOPNE/LOOPNZ** Used to loop a group of instructions till it satisfies ZF = 0 & CX = 0

- **JCXZ** Used to jump to the provided address if CX = 0

#### **Interrupt Instructions**

These instructions are used to call the interrupt during program execution.

• **INT** – Used to interrupt the program during execution and calling service specified.

- **INTO** Used to interrupt the program during execution if OF = 1

- **IRET** Used to return from interrupt service to the main program

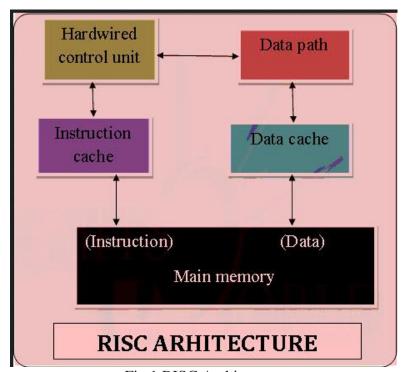

#### 2.4 RISC Architecture

RISC (Reduced Instruction Set Computer) is used in portable devices due to its power efficiency. RISC is a type of microprocessor architecture that uses highly-optimized set of instructions. RISC does the opposite, reducing the cycles per instruction at the cost of the number of instructions per program Pipelining is one of the unique feature of RISC. It is performed by overlapping the execution of several instructions in a pipeline fashion. It has a high performance advantage over CISC.

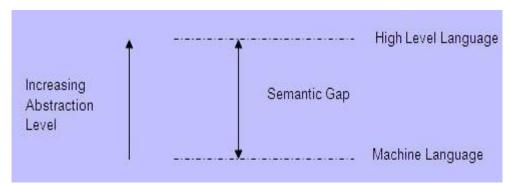

Fig 1 RISC Architecture

RISC processors take simple instructions and are executed within a clock cycle

# RISC ARCHITECTURE CHARACTERISTICS

- Simple Instructions are used in RISC architecture.

- RISC helps and supports few simple data types and synthesize complex data types.

- RISC utilizes simple addressing modes and fixed length instructions for pipelining.

- RISC permits any register to use in any context.

- One Cycle Execution Time

- The amount of work that a computer can perform is reduced by separating "LOAD" and "STORE" instructions.

- RISC contains Large Number of Registers in order to prevent various number of interactions with memory.

- In RISC, Pipelining is easy as the execution of all instructions will be done in a uniform interval of time i.e. one click.

- In RISC, more RAM is required to store assembly level instructions.

- Reduced instructions need a less number of transistors in RISC.

- RISC uses Harvard memory model means it is Harvard Architecture.

- A compiler is used to perform the conversion operation means to convert a high-level language statement into the code of its form.

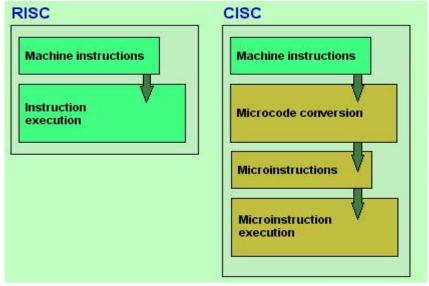

# **RISC & CISC Comparison**

| CISC                                                               | RISC                                             |

|--------------------------------------------------------------------|--------------------------------------------------|

| It is prominent on Hardware                                        | It is prominent on the Software                  |

| It has high cycles per second                                      | It has low cycles per second                     |

| It has transistors used for storing Instructions which are complex | More transistors are used for storing memory     |

| LOAD and STORE memory-to-memory is induced in instructions         | LOAD and STORE register-register are independent |

| It has multi-clock                                                 | It has a single - clock                          |

MUL instruction is divided into three instructions

"LOAD" – moves data from the memory bank to a register

"PROD" – finds product of two operands located within the registers

"STORE" – moves data from a register to the memory banks

The main difference between RISC and CISC is the number of instructions and its complexity.

Fig 2 RISC Vs CISC

#### **SEMANTIC GAP**

Both RISC and CISC architectures have been developed as an attempt to cover the semantic gap.

Fig 3 Semantic Gap

With an objective of improving efficiency of software development, several powerful programming languages have come up, viz., Ada, C, C++, Java, etc. They provide a high level of abstraction, conciseness and power. By this evolution the semantic gap grows. To enable efficient compilation of high level language programs, CISC and RISC designs are the two options.

CISC designs involve very complex architectures, including a large number of instructions and addressing modes, whereas RISC designs involve simplified instruction set and adapt it to the real requirements of user programs.

Fig 4 CISC and RISC Design

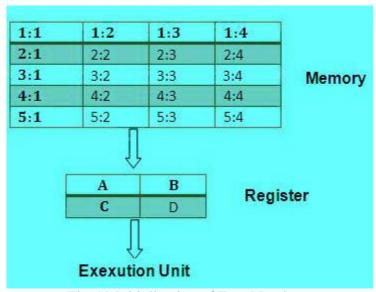

### **Multiplication of two Numbers in Memory**

If the main memory is divided into areas that are numbered from row1:column 1 to row 5 :column 4. The data is loaded into one of four registers (A, B, C, or D). To find multiplication of two numbers- One stored in location 1:3 and other stored in location 4:2 and store back result in 1:3.

Fig 5 Multiplication of Two Numbers

## The Advantages and Disadvantages of RISC and CISC

### The Advantages of RISC architecture

- RISC architecture has a set of instructions, so high-level language compilers can produce more efficient code

- It allows freedom of using the space on microprocessors because of its simplicity.

- Many RISC processors use the registers for passing arguments and holding the local variables.

- RISC functions use only a few parameters, and the RISC processors cannot use the call instructions, and therefore, use a fixed length instruction which is easy to pipeline.

- The speed of the operation can be maximized and the execution time can be minimized. Very less number of instructional formats, a few numbers of instructions and a few addressing modes are needed.

# The Disadvantages of RISC architecture

- Mostly, the performance of the RISC processors depends on the programmer or compiler as the knowledge of the compiler plays a vital role while changing the CISC code to a RISC code

- While rearranging the CISC code to a RISC code, termed as a code expansion, will increase the size. And, the quality of this code expansion will again depend on the compiler, and also on the machine's instruction set.

• The first level cache of the RISC processors is also a disadvantage of the RISC, in which these processors have large memory caches on the chip itself. For feeding the instructions, they require very fast memory systems.

## **Advantages of CISC architecture**

- Microprogramming is easy assembly language to implement, and less expensive than hard wiring a control unit.

- The ease of micro coding new instructions allowed designers to make CISC machines upwardly compatible:

- As each instruction became more accomplished, fewer instructions could be used to implement a given task.

## **Disadvantages of CISC architecture**

- The performance of the machine slows down due to the amount of clock time taken by different instructions will be dissimilar

- Only 20% of the existing instructions is used in a typical programming event, even though there are various specialized instructions in reality which are not even used frequently.

- The conditional codes are set by the CISC instructions as a side effect of each instruction which takes time for this setting and, as the subsequent instruction changes the condition code bits so, the compiler has to examine the condition code bits before this happens.

#### **TEXT BOOK:**

1. Douglas V.Hall, Microprocessor and Interfacing Programming and Hardware. Tata McGraw

Hill, New Delhi 2007.

### **REFERENCES BOOK:**

1. Krishna Kant, Microprocessor and Microcontroller Architecture, programming and system

design using 8085, 8086, 8051 and 8096, PHI, New Delhi, 2008

### **QUESTION BANK**

#### PART-B (16 MARKS)

- 1. Explain the various addressing modes of 8086 microprocessor with examples?

- 2. Explain Data transfer, arithmetic and branch instructions?

- 3. Write an 8086 ALP to find the sum of numbers in the array of 10 elements?

- 4. Write in detail about instruction formats and instruction execution timing?

- 5. Write an ALP to find the largest number and smallest number in the array? 6. Write a short note about Loop, NOP and HLT instructions

- 7. Write a short note about Flag manipulation, logical and shift& rotate instructions?

- 8. Explain the direct addressing modes and indirect addressing modes of 8086 with example.

- 9. Assume that the accumulator contents data bytes 88 hand instruction MOV C, A 4FH is fetched. List the steps decoding and executing the instruction

- 10. Write a Program to Perform the following functions and verify the output steps: a. Load the number 5CH in register D b. Load the number 9E H in register C. Increment the Contents of register C by one. d. Add the contents of register C and D and Display the sum at output port1.

- 11. Write an assembly language program to find out the largest number from a given unordered array of 8 bit numbers, stored in the locations starting from a known address.

- 12. With suitable examples explain 8086 addressing modes in detail.

- 13. Write 8086 assembly language program to SORT an array of 10 bytes in Descending order.

- 14. Write an 8086 ALP to perform 32 bit binary addition?

- 15. Write an 8085 ALP to convert the hexadecimal value to decimal value

- 16. List the addressing modes in 8086 and explain with suitable examples.

- 17. Describe the Different types of instruction in 8086.

- 18. Explain in detail about the Logical and Arithmetic group of 8086 instruction set with suitable examples.

- 19. Explain the various assembler directives

- 20. Write a program for 8 bit addition and subtraction

- 21. Write a program for 8 bit addition, subtraction, multiplication and division

- 22. Explain the assembler directives and procedures with examples.

- 23. Write a Program for 8 bit addition and subtraction and find largest number using 8086.

- 24. Explain the various ways by which the operand can be addressed with examples.

- 25. Describe the Instruction Set of ARM with examples.

- 26. Explain the internal hardware architecture of RISC with neat diagram?

### **UNIT III**

#### **INTERFACING DEVICES**

## **Interfacing Devices**

Programmable Peripheral Interface (8255) - Programmable Interval Timer (8254) - Programmable Interrupt Controller (8259A) - Programmable DMA Controller (8257) - Programmable Communication Interface (8251A) - Programmable Keyboard and Display Controller (8279).

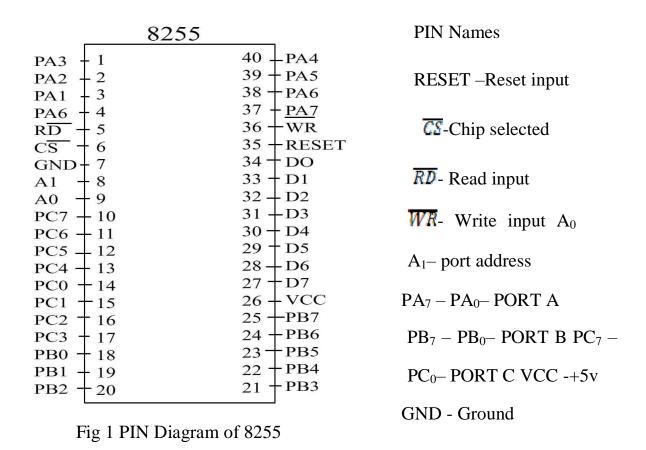

# 3.1 INTEL 8255:(Programmable Peripheral Interface)

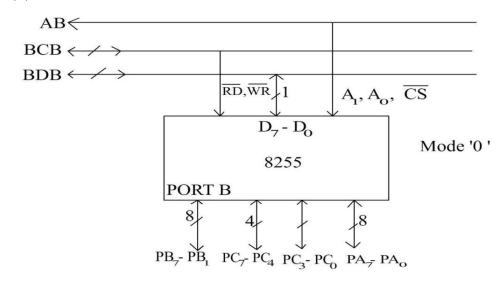

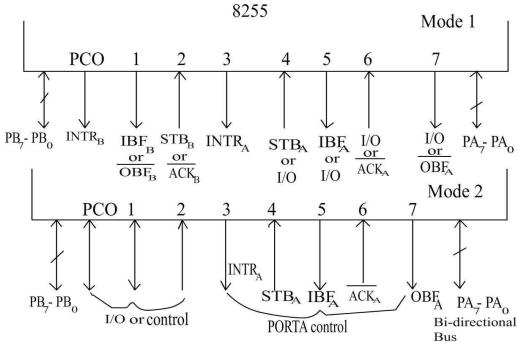

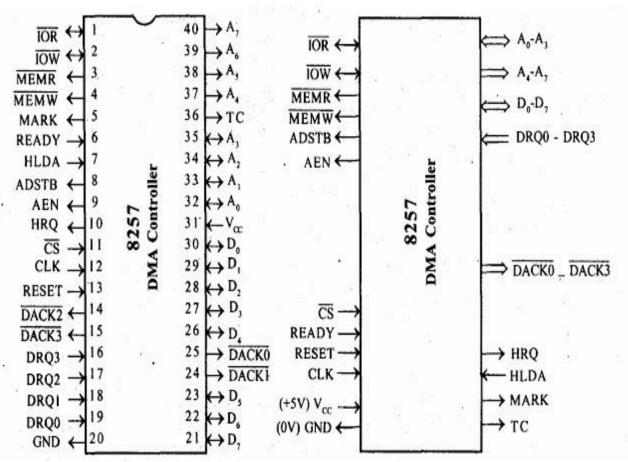

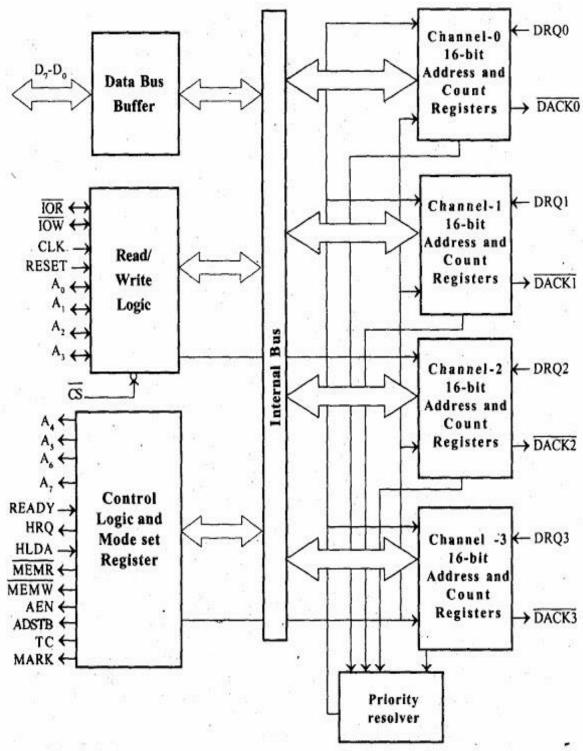

The 8255A is a general purpose programmable I/O device designed for use with Intel microprocessors. It consists of three 8-bit bidirectional I/O ports (24I/O lines) that can be configured to meet different system I/O needs. The three ports are PORT A, PORT B & PORT C. Port A contains one 8-bit output latch/buffer and one 8-bit input buffer. Port B is same as PORT A or PORT B. However, PORT C can be split into two parts PORT C lower (PC<sub>0</sub>-PC<sub>3</sub>) and PORT C upper (PC<sub>7</sub>-PC<sub>4</sub>) by the control word. The three ports are divided in two groups Group A (PORT A and upper PORT C) Group B (PORT B and lower PORT C). The two groups can be programmed in three different modes. In the first mode (mode 0), each group may be programmed in either input mode or output mode (PORT A, PORT B, PORT C lower, PORT C upper). In mode 1, the second's mode, each group may be programmed to have 8-lines of input or output (PORT A or PORT B) of the remaining 4-lines (PORT C lower or PORT C upper) 3lines are used for hand shaking and interrupt control signals. The third mode of operation (mode 2) is a bidirectional bus mode which uses 8-line (PORT A only for a bidirectional bus and five lines (PORT C upper 4 lines and borrowing one from other group) for handshaking.

The 8255 is contained in a 40-pin package, whose pin out is shown below:

Group A Group A control PORT A Group A PORT C PC-PC PC<sub>3</sub>- PC<sub>0</sub> GroupA PORT C  $\overline{RD}$ Read Group B WR-Write control  $A_1$ Control Group B  $\overrightarrow{PB}_{o}$ Logic PORT B RESET CS-

Fig 2 Block Diagram of 8255

# **Functional Description:**

This support chip is a general purpose I/O component to interface peripheral equipment to the microcomputer system bus. It is programmed by the system software so that normally no external logic is necessary to interface peripheral devices or structures.

#### **Data Bus Buffer:**

It is a tri-state 8-bit buffer used to interface the chip to the system data bus. Data is transmitted or received by the buffer upon execution of input or output instructions by the CPU. Control words and status information are also transferred through the data bus buffer. The data lines are connected to BDB of p.

Read/Write and logic control:

The function of this block is to control the internal operation of the device and to control the transfer of data and control or status words. It accepts inputs from the CPU address and control buses and in turn issues command to both the control groups.

# **Chip Select:** $\overline{CS}$

A low on this input selects the chip and enables the communication between the 8255 A& the CPU. It is connected to the output of address decode circuitry to select the device when it  $\overline{RD}$  (Read). A low on this input enables the 8255 to send the data or status information to the CPU on the data bus.

(Write):  $\overline{WR}$

A low on this input pin enables the CPU to write data or control words into the 8255

# A<sub>1</sub>, A<sub>0</sub> port select:

These input signals, in conjunction with the  $\overline{RD}$  and  $\overline{WR}$  inputs, control the selection of one of the three ports or the control word registers. They are normally connected to the least significant bits of the address bus (A<sub>0</sub> and A<sub>1</sub>).

| 1 0110 | , wing 1 a | ioic gives | the busic ( | operation, |                  |

|--------|------------|------------|-------------|------------|------------------|

| $A_1$  | $A_0$      | RD         | WR          | CS         | Input operation  |

| 0      | 0          | 0          | 1           | 0          | PORT A Data bus  |

| 0      | 1          | 0          | 1           | 0          | PORT B Data bus  |