Semester-III

### 19BEEC303

### **DIGITAL SYSTEM DESIGN**

3H-3C

**Instruction Hours/week: L: 3 T:0 P: 0**Marks: Internal:40 External:60 Total:100

**End Semester Exam:**3 Hours

### **Course Objective**

• To introduce the theoretical and circuit aspects of digital electronics, which is the back bone for the basics of the hardware aspect of digital computers

### **Course Outcomes**

At the end of this course students will demonstrate the ability to

- Design and analyze combinational logic circuits

- Design & analyze modular combinational circuits with MUX/DEMUX, Decoder, Encoder

- Design & analyze synchronous sequential logic circuits

- Differentiate different logical families

- Gain knowledge about various memory devices and implement using PLDs

- Use HDL & appropriate EDA tools for digital logic design and simulation

### UNIT I BOOLEAN ALGEBRA

Number system, Logic Simplification and Combinational Logic Design: Review of Boolean Algebra and De-Morgan's Theorem, SOP & POS forms, Canonical forms, Karnaugh maps up to 6 variables, Binary codes, Code Conversion.

### UNIT II COMBINATIONAL CIRCUITS

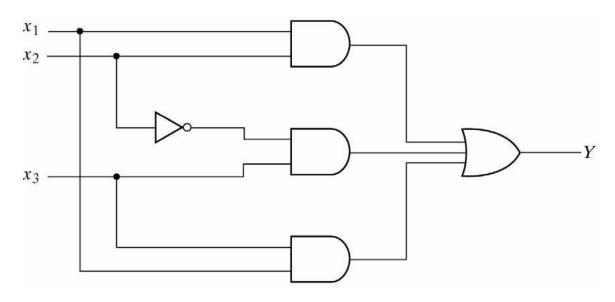

Logic gates, AND & NOR implementation, MSI devices - Comparators, Multiplexers, Encoder, Decoder, Driver & Multiplexed Display, Half and Full Adders, Subtractors, Serial and Parallel Adders, BCD Adder, Barrel shifter and ALU.

### UNIT III SEQUENTIAL LOGIC DESIGN

D,S-R, JK FF and Master-Slave JK FF, Edge triggered FF, Ripple and Synchronous counters, Shift registers, Finite state machines, Design of synchronous FSM, Algorithmic State Machines charts. Designing synchronous circuits like Pulse train generator, Pseudorandom Binary Sequence generator, Clock generation

### UNIT IV LOGIC FAMILIES AND SEMICONDUCTOR MEMORIES

TTL NAND gate, Specifications, Noise margin, Propagation delay, fan-in, fan-out, Tristate TTL, ECL, CMOS families and their interfacing, Memory elements, Concept of Programmable logic devices like FPGA. Logic implementation using Programmable Devices.

### UNIT V INTRODUCTION TO VHDL

VLSI Design flow: Design entry: Schematic, FSM & HDL, different modeling styles in VHDL, Data types and objects, Dataflow, Behavioral and Structural Modeling, Synthesis and Simulation VHDL constructs and codes for combinational and sequential circuits.

### **Suggested Readings**

- 1. R.P. Jain, "Modern digital Electronics", Tata McGraw Hill, 4th edition, 2009.

- 2. Douglas Perry, "VHDL", Tata McGraw Hill, 4th edition, 2002.

- 3. W.H. Gothmann, "Digital Electronics- An introduction to theory and practice", PHI, 2nd edition ,2006.

- 4. D.V. Hall, "Digital Circuits and Systems", Tata McGraw Hill, 2004

- 5. Charles Roth, "Digital System Design using VHDL", Tata McGraw Hill 2nd edition 2012.

# Karpagam Academy of Higher Education

(Established under Section 3 of UGC Act 1956)

Eachanari, Coimbatore-641 021. INDIA

# Department of Electronics and Communication Engineering Faculty of Engineering

# **DIGITAL ELECTRONICS**

Lecture Notes -Unit I

PREPARED BY Dr.S.Bhavani,HOD/ECE

### UNIT-I NUMBER SYSTEMS

Binary, Octal, Decimal, Hexadecimal-Number base conversions – complements – signed Binary numbers. Binary Arithmetic- Binary codes: Weighted –BCD-2421-Gray code-Excess 3 code-ASCII –Error detecting code – conversion from one code to another-Boolean postulates and laws –De-Morgan's Theorem- Principle of Duality- Boolean expression – Boolean function-Minimization of Boolean expressions – Sum of Products (SOP) –Product of Sums (POS)-Minterm- Maxterm- Canonical forms – Conversion between canonical forms –Karnaugh map Minimization – Don't care conditions.

### UNIT-I NUMBER SYSTEMS

### 1. Introduction to Digital System

Any system has input, output and processing unit. What processing it does depend on the type of the system For example if it is an adder system, we will have inputs, the outputs will be sum and carry and the processing unit will have units to perform addition operation on inputs to generate the required output. The term digital refers to any process that is accomplished in discrete manner. A best example of a digital system is Digital computer.

The Electronic circuits are basically classified into two types namely

- i) Analog

- ii) Digital

Almost all digital circuits are logical circuits because

- 1. It is easier to manipulate logical values (i.e., 0/1 or low/high values) than to manipulate and process multiple (Discrete) voltage levels.

- 2. Everyone can use the formal laws of Boolean logic to design logic circuits easily and systematically. Hence these laws which are used to formulate digital logic are called as Boolean algebra or Switching algebra

### 1.1Types of Number Systems

- i) Decimal Number system

- ii) Binary Number system

- iii) Octal Number system

- iv) Hexadecimal Number system

### Complements

Complements are used in digital computers for simplifying the subtraction operation and for logical manipulation. For any numbering system, there are two types of complements available, which are

- i) r's complement

- ii) (r-1)'s complement.

In general complements are used to have reduction in computation time and complexity. When we go for arithmetic operations we will find the subtraction operation in simple way with less computation in 2's complement compared to I's complement.

For Binary numbering system we have 2's complement and 1's complement.

For Decimal numbering system we have 10's complement and 9's complement

For Octal numbering system we have 8's complement and 7's complement

For Hexadecimal numbering system we have 16's complement and 15's complement

## **Binary Codes**

| ec | Hex | Oct Bin      | Dec | Hex        | Oct Bin      |

|----|-----|--------------|-----|------------|--------------|

| _  | 0   | 000 00000000 | 16  | 10         | 020 00010000 |

|    | 1   | 001 00000001 | 17  | 11         | 021 00010001 |

|    | 2   | 002 00000010 | 18  | 12         | 022 00010010 |

|    | 3   | 003 00000011 | 19  | 13         | 023 00010011 |

| 4  | 4   | 004 00000100 | 20  | 14         | 024 00010100 |

| 5  | 5   | 005 00000101 | 21  | 15         | 025 00010101 |

| 6  | 6   | 006 00000110 | 22  | 16         | 026 00010110 |

| 7  | 7   | 007 00000111 | 23  | 17         | 027 00010111 |

| 8  | 8   | 010 00001000 | 24  | 18         | 030 00011000 |

| 9  | 9   | 011 00001001 | 25  | 19         | 031 00011001 |

| 10 | A   | 012 00001010 | 26  | 1 <b>A</b> | 032 00011010 |

| 11 | В   | 013 00001011 | 27  | 1B         | 033 00011011 |

| 12 | C   | 014 00001100 | 28  | 1C         | 034 00011100 |

| 13 | D   | 015 00001101 | 29  | 1D         | 035 00011101 |

| 14 | E   | 016 00001110 | 30  | 1E         | 036 00011110 |

| 15 | F   | 017 00001111 | 31  | 1F         | 037 00011111 |

Conversion of codes from one form to another:

# 1. Binary to Decimal

| Binary                                               | Decimal     |

|------------------------------------------------------|-------------|

| 110112                                               |             |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | =16+8+0+2+1 |

| Result                                               | 2710        |

## 2. Decimal to binary

| Division | Remainder            | Binary                    |

|----------|----------------------|---------------------------|

| 25/2     | = 12+ remainder of 1 | 1 (Least Significant Bit) |

| 12/2     | = 6 + remainder of 0 | 0                         |

| 6/2      | = 3 + remainder of 0 | 0                         |

| 3/2      | = 1 + remainder of 1 | 1                         |

| 1/2      | = 0 + remainder of 1 | 1 (Most Significant Bit)  |

| Result   | 10                   | = 110012                  |

## 3.Binary to Octal

### $100\ 111\ 0102 = (100)\ (111)\ (010)2 = 4\ 7\ 28$

### Decimal to octal

| Division | Result               | Binary                    |

|----------|----------------------|---------------------------|

| 177/8    | = 22+ remainder of 1 | 1 (Least Significant Bit) |

| 22/8     | = 2 + remainder of 6 | 6                         |

| 2/8      | = 0 + remainder of 2 | 2 (Most Significant Bit)  |

| Result   | 177 <sub>10</sub>    | = 2618                    |

| Binary   |                      | = 0101100012              |

### 4. Decimal to Hexadecimal

| Division | Result                | Hexadecimal                 |

|----------|-----------------------|-----------------------------|

| 378/16   | = 23+ remainder of 10 | A (Least Significant Bit)23 |

| 23/16    | = 1 + remainder of 7  | 7                           |

| 1/16     | = 0 + remainder of 1  | 1 (Most Significant Bit)    |

| Result   | 378 <sub>10</sub>     | = 17A <sub>16</sub>         |

| Binary   |                       | = 0001 0111 10102           |

### 5. Hexadecimal to binary

$$1011\ 0010\ 11112 = (1011)\ (0010)\ (1111)2 = B\ 2\ F_{16}$$

### 6. Hexadecimal to octal

| Hexadecimal | Binary/Octal                             |

|-------------|------------------------------------------|

| 5A816       | = <b>0101</b> 1010 <b>1000</b> (Binary)  |

|             | = <b>010</b> 110 <b>101</b> 000 (Binary) |

| Result      | = 2 6 5 0 (Octal)                        |

### 1.2 Binary Arithmetic Operations:

### 1.2.1 Rules of Binary Addition

0 + 0 = 0

0 + 1 = 1

1 + 0 = 1

1 + 1 = 0, and carry 1 to the next more significant bit

### For example,

### 1.2.2 Rules of Binary Subtraction

0 - 0 = 0

0 - 1 = 1, and borrow 1 from the next more significant bit

1 - 0 = 1

1 - 1 = 0

### For example,

### 1.2.3 Rules of Binary Multiplication

$0 \times 0 = 0$

$0 \times 1 = 0$

$1 \times 0 = 0$

$1 \times 1 = 1$ , and no carry or borrow bits

For example,

**Another Method:** Binary multiplication is the same as repeated binary addition; add the multicand to itself the multiplier number of times.

For example,

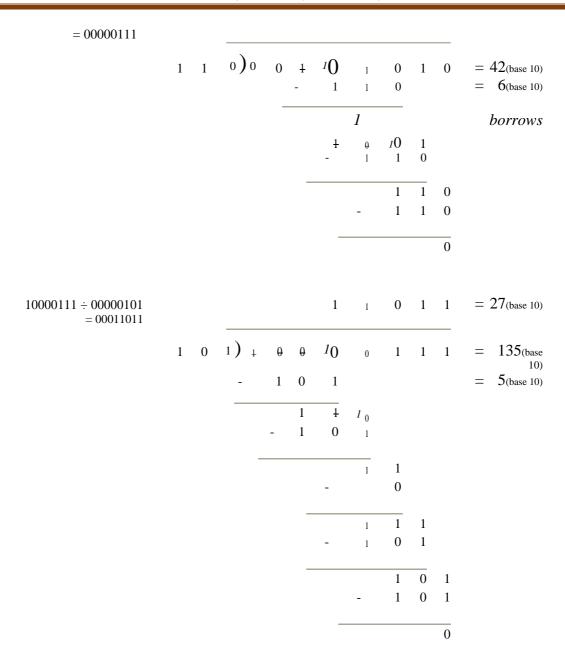

### **Binary Division**

Binary division is the repeated process of subtraction, just as in decimal division.

### 1.2.4 Rules of Binary Divison

$$1/1 = 1$$

$0/0 = 0$

For example,

### 1.3 Types of binary codes

Binary codes are codes which are represented in binary system with modification from the original ones. Below we will be seeing the following: Weighted codes and Non-Weighted codes

### 1.3.1 Weighted binary codes

Weighted binary codes are those which obey the positional weighting principles, each position of the number represents a specific weight. The binary counting sequence is an example.

| 0 | 0000 | 0000 | 0000 | 0011 |

|---|------|------|------|------|

| 1 | 0001 | 0001 | 0001 | 0100 |

| 2 | 0010 | 0010 | 0011 | 0101 |

| 3 | 0011 | 0011 | 0101 | 0110 |

| 4 | 0100 | 0100 | 0111 | 0111 |

| 5 | 0101 | 1011 | 1000 | 1000 |

| 6 | 0110 | 1100 | 1010 | 1001 |

| 7 | 0111 | 1101 | 1100 | 1010 |

|---|------|------|------|------|

| 8 | 1000 | 1110 | 1110 | 1011 |

| 9 | 1001 | 1111 | 1111 | 1100 |

### 1. 8421 code/BCD code

The BCD (Binary Coded Decimal) is a straight assignment of the binary equivalent. It is possible to assign weights to the binary bits according to their positions. The weights in the BCD code are 8,4,2,1.

**Example:** The bit assignment 1001, can be seen by its weights to represent the decimal 9 because 1x8+0x4+0x2+1x1=9

### 2. 2421 code

This is a weighted code; its weights are 2, 4, 2 and 1. A decimal number is represented in 4-bit form and the total four bits weight is 2 + 4 + 2 + 1 = 9. Hence the 2421 code represents the decimal numbers from 0 to 9.

#### 3. 5211 code

This is a weighted code; its weights are 5, 2, 1 and 1. A decimal number is represented in 4-bit form and the total four bits weight is 5 + 2 + 1 + 1 = 9. Hence the 5211 code represents the decimal numbers from 0 to 9.

#### Reflective code

A code is said to be reflective when code for 9 is complement for the code for 0, and so is for 8 and 1 codes, 7 and 2, 6 and 3, 5 and 4. Codes 2421, 5211, and excess-3 are reflective, whereas the 8421 code is not.

### **Sequential code**

A code is said to be sequential when two subsequent codes, seen as numbers in binary representation, differ by one. This greatly aids mathematical manipulation of data. The 8421 and Excess-3 codes are sequential, whereas the 2421 and 5211 codes are not.

#### 1.3.2. Non-Weighted code

Non weighted codes are codes that are not positionally weighted. That is, each position within the binary number is not assigned a fixed value.

### 1. Excess-3 code

Excess-3 is a non weighted code used to express decimal numbers. The code derives its name from the fact that each binary code is the corresponding 8421 code plus 0011(3).

**Example:** 1000 of 8421 = 1011 in Excess-3

### 2. Gray code

The gray code belongs to a class of codes called minimum change codes, in which only one bit in the code changes when moving from one code to the next. The Gray code is non-weighted code, as the position of bit does not contain any weight. The gray code is a reflective digital code which has the special property that any two subsequent numbers codes differ by only one bit. This is also called a unit-distance code. In digital Gray code has got a special place.

| <b>Decimal Number</b> | Binary Code | Gray Code |

|-----------------------|-------------|-----------|

| 0                     | 0000        | 0000      |

| 1                     | 0001        | 0001      |

| 2                     | 0010        | 0011      |

| 3                     | 0011        | 0010      |

| 4                     | 0100        | 0110      |

| 5                     | 0101        | 0111      |

| 6                     | 0110        | 0101      |

| 7                     | 0111        | 0100      |

| 8                     | 1000        | 1100      |

| 9                     | 1001        | 1101      |

| 10                    | 1010        | 1111      |

| 11                    | 1011        | 1110      |

| 12                    | 1100        | 1010      |

| 13                    | 1101        | 1011      |

| 14                    | 1110        | 1001      |

| 15                    | 1111        | 1000      |

### 3. Error detecting and correcting codes

For reliable transmission and storage of digital data, error detection and correction is required. Below are a few examples of codes which permit error detection and error correction after detection.

### **Error detecting codes:**

When data is transmitted from one point to another, like in wireless transmission, or it is just stored, like in hard disks and memories, there are chances that data may get corrupted. To detect these data errors, we use special codes, which are error detection codes.

### Parity bit:

In parity codes, every data byte, or nibble (according to how user wants to use it) is checked if they have even number of ones or even number of zeros. Based on this information an additional bit is appended to the original data. Thus if we consider 8-bit data, adding the parity bit will make it 9 bit long. At the receiver side, once again parity is calculated and matched with the received parity (bit 9), and if they match, data is ok, otherwise data is corrupt.

### Two types of parity

**Even parity:** Checks if there is an even number of ones; if so, parity bit is zero. When the number of ones is odd then parity bit is set to 1.

**Odd Parity:** Checks if there is an odd number of ones; if so, parity bit is zero. When number of ones is even then parity bit is set to 1.

### **Error correcting codes:**

Error-correcting codes not only detect errors, but also correct them. This is used normally in Satellite communication, where turn-around delay is very high as is the probability of data getting corrupt.

### 1. Hamming codes

Hamming code adds a minimum number of bits to the data transmitted in a noisy channel, to be able to correct every possible one-bit error. It can detect (not correct) two-bit errors and cannot distinguish between 1-bit and 2-bits inconsistencies. It can't - in general - detect 3(or more)-bits errors.

### 1.3.3. Alphanumeric codes

The binary codes that can be used to represent all the letters of the alphabet, numbers and mathematical symbols, punctuation marks, are known as alphanumeric codes or character codes. These codes enable us to interface the input-output devices like the keyboard, printers, video displays with the computer.

### 1. ASCII codes

ASCII stands for American Standard Code for Information Interchange. It has become a world standard alphanumeric code for microcomputers and computers. It is a 7-bit code representing 2 = 128 different characters. These characters represent 26 upper case letters (A to Z), 26 lowercase letters (a to z), 10 numbers (0 to 9), 33 special characters and symbols and 33 control characters.

### 2. EBCDIC codes

EBCDIC stands for Extended Binary Coded Decimal Interchange. It is mainly used with large computer systems like mainframes. EBCDIC is an 8-bit code and thus accommodates up to 256 characters. An EBCDIC code is divided into two portions: 4 zone bits (on the left) and 4 numeric bits (on the right).

Simplification of Boolean functions can be done by using

- i) Boolean theorems and postulates.

- ii) Karnaugh Map(K-Map)

- iii) Prime Implicant Method or Tabulation methods or Quine Mc-Cluskey Method

### 1.4 Boolean Algebra theorems and postulates.

### **Principle of duality**

Principle of duality states that a dual expression can be obtained by Interchanging the OR and AND operatio expression, Interchanging the 0 and 1 elements of the expression and Not changing the form of the variables.

### **T1:** Commutative Law

(a)

$$A + B = B + A$$

(b)

$$A B = B A$$

### T2: Associative Law

(a)

$$(A + B) + C = A + (B + C)$$

(b)

$$(A \ B) \ C = A \ (B \ C)$$

### T3: Distributive Law

(a)

$$A(B + C) = AB + AC$$

(b)

$$A + (B C) = (A + B) (A + C)$$

### **T4: Idempotent Law for Addition**

(a)

$$A + A = A$$

(b)

$$A A = A$$

### **T5: Negation Law**

(a)

$$(\overline{A}) = \overline{A}$$

(b)

$$(A)$$

''= A

**T6: Redundance Law**

(a)

$$A + A B = A$$

(b)

$$A (A + B) = A$$

T7: Law of Identity

(a)

$$0 + A = A$$

(b)

$$1 A = A$$

(c)

$$1 + A = 1$$

(d)

$$0A = 0$$

**T8**: Idempotent law for Multiplication

(a)

$$\overline{A} + A = I$$

(b)

$$\overline{A} A = 0$$

**T9: Absorption Law**

(a)

$$A + \overline{A} B = A + B$$

(b)

$$A(\overline{A} + B) = AB$$

**T10: De Morgan's Theorem**

(a)

$$(A+B)'=A' \cdot B'$$

(b)

$$(A.B)' = A' + B'$$

### 1.5 Canonical Form of Boolean Expressions

An expanded form of Boolean expression, where each term contains all Boolean variables in their true or complemented form, is also known as the canonical form of the expression. As an illustration,  $f(A.B, C) = \overline{A.B.C} + \overline{A.B.C} + \overline{A.B.C}$  is a Boolean function of three variables expressed in canonical form. This function after simplification reduces to  $\overline{A.B} + A.B.C$  and loses its canonical form

#### 1.5.1 MIN TERMS AND MAX TERMS

Any boolean expression may be expressed in terms of either minterms or maxterms. To do this we must first define the concept of a literal. A literal is a single variable within a term which may or may not be complemented. For an expression with N variables, minterms and maxterms are defined as follows:

- A minterm is the product of N distinct literals where each literal occurs exactly once.

- A maxterm is the sum of N distinct literals where each literal occurs exactly once.

### **Product-of-Sums Expressions**

### 1.5.2 Standard Forms

A product-of-sums expression contains the product of different terms, with each term being either a single literal or a sum of more than one literal. It can be obtained from the truth table by considering those input combinations that produce a logic \_0' at the output. Each such input combination gives a term, and the product of all such terms gives the expression.

Different terms are obtained by taking the sum of the corresponding literals. Here, \_0' and \_1' respectively mean the un complemented and complemented variables, unlike sum-of-products expressions where \_0' and \_1' respectively mean complemented and un complemented variables.

Since each term in the case of the product-of-sums expression is going to be the sum of literals, this implies that it is going to be implemented using an OR operation. Now, an OR gate produces a logic \_0' only when all its inputs are in the logic \_0' state, which means that the first term corresponding to the second row of the truth table will be A+B+C. The product-of-sums Boolean expression for this truth table is given by Transforming the given product-of-sums expression into an equivalent sum-of-products expression is a straightforward process. Multiplying out the given expression and carrying out the obvious simplification provides the equivalent sum-of-products expression:A given sum-of-products expression can be transformed into an equivalent product-of-sums expression by (a) taking the dual of the given expression, (b) multiplying out different terms to get the sum-of products form, (c) removing redundancy and (d) taking a dual to get the equivalent product-of-sums expression. As an illustration, let us find the equivalent product-of-sums expression of the sum-of products expression

$$A.B + \overline{A}.\overline{B}$$

The dual of the given expression =  $(A + B).(\overline{A} + \overline{B})$ :

$(A + B).(\overline{A} + \overline{B}) = A.\overline{A} + A.\overline{B} + B.\overline{A} + B.\overline{B} = 0 + A.\overline{B} + B.\overline{A} + 0 = A.\overline{B} + \overline{A}.B$

The dual of  $(A.\overline{B} + \overline{A}.B) = (A + \overline{B}).(\overline{A} + B)$ . Therefore

$$A.B + \overline{A}.\overline{B} = (A + \overline{B}).(\overline{A} + B)$$

### 1.6 Minimization Technique

The primary objective of all simplification procedures is to obtain an expression that has the minimum number of terms. Obtaining an expression with the minimum number of literals is usually the secondary objective. If there is more than one possible solution with the same number of terms, the one having the minimum number of literals is the choice.

There are several methods for simplification of Boolean logic expressions. The process is usually called logic minimization and the goal is to form a result which is efficient. Two methods we will discuss are algebraic minimization and Karnaugh maps. For very complicated problems the former method can be done using special software analysis programs. Karnaugh maps are also limited to problems with up to 4 binary inputs. The Quine–McCluskey tabular method is used for more than 4 binary inputs.

### 1.6.1 Karnaugh Map Method

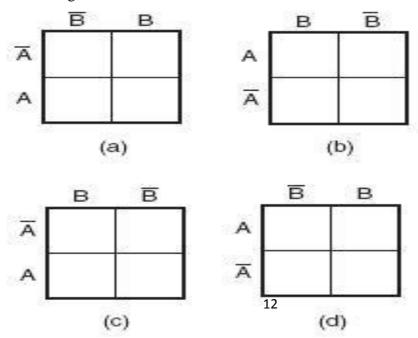

Maurice Karnaugh, a telecommunications engineer, developed the Karnaugh map at Bell Labs in 1953 while designing digital logic based telephone switching circuits. Karnaugh maps reduce logic functions more quickly and easily compared to Boolean algebra. By reduce we mean simplify, reducing the number of gates and inputs. We like to simplify logic to a lowest cost form to save costs by elimination of components. We define lowest cost as being the lowest number of gates with the lowest number of inputs per gate. A Karnaugh map is a graphical representation of the logic system. It can be drawn directly from either minterm (sum-of-products) or maxterm (product-of-sums) Boolean expressions. Drawing a Karnaugh map from the truth table involves an additional step of writing the minterm or maxterm expression depending upon whether it is desired to have a minimized sum-of-products or a minimized product of-sums expression

### **Construction of a Karnaugh Map**

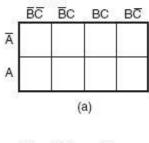

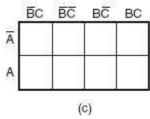

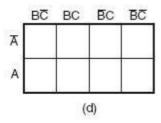

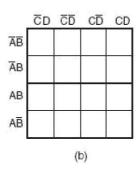

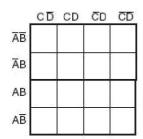

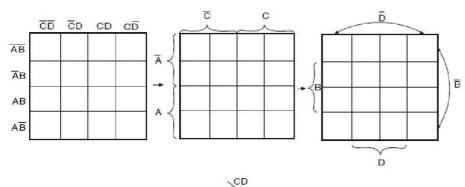

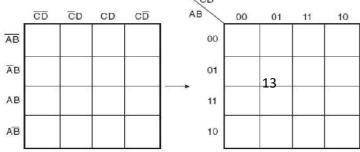

An n-variable Karnaugh map has 2n squares, and each possible input is allotted a square. In the case of a minterm Karnaugh map, \_1' is placed in all those squares for which the output is \_1', and \_0' is placed in all those squares for which the output is \_0'. Os are omitted for simplicity. An \_X' is placed in squares corresponding to \_don't care' conditions. In the case of a maxterm Karnaugh map, a \_1' is placed in all those squares for which the output is \_0', and a \_0' is placed for input entries corresponding to a \_1' output. Again, Os are omitted for simplicity, and an \_X' is placed in squares corresponding to \_don't care' conditions. The choice of terms identifying different rows and columns of a Karnaugh map is not unique for a given number of variables. The only condition to be satisfied is that the designation of adjacent rows and adjacent columns should be the same except for one of the literals being complemented. Also, the extreme rows and extreme columns are considered adjacent. Some of the possible designation styles for two-, three- and four-variable minterm Karnaugh maps are shown in the figure below.

The style of row identification need not be the same as that of column identification as long as it meets the basic requirement with respect to adjacent terms. It is, however, accepted practice to adopt a uniform style of row and column identification. Also, the style shown in the figure below is more commonly used. A similar discussion applies for maxterm Karnaugh maps. Having drawn the Karnaugh map, the next step is to form groups of 1s as per the following guidelines:

Each square containing a 1' must be considered at least once, although it can be considered as often as desired.

The objective should be to account for all the marked squares in the minimum number of groups.

The number of squares in a group must always be a power of 2, i.e. groups can have 1,2, 4\_8, 16, squares.

Each group should be as large as possible, which means that a square should not be accounted for by itself if it can be accounted for by a group of two squares; a group of two squares should not be made if the involved squares can be included in a group of four squares and so on.

\_Don't care' entries can be used in accounting for all of 1-squares to make optimum groups. They are marked \_X' in the corresponding squares. It is, however, not necessary to account for all \_don't care' entries. Only such entries that can be used to advantage should be used.

### Two variable K Map

### Three variable K Map

(d)

## Four variable K Map

### Different Styles of row and column identification

Having accounted for groups with all 1s, the minimum \_sum-of-products' or \_product-of-sums' expressions can be written directly from the Karnaugh map. Minterm Karnaugh map and Maxterm Karnaugh map of the Boolean function of a two-input OR gate. The Minterm and Maxterm Boolean expressions for the two-input OR gate are as follows:

$$Y = A + B$$

(maxterm or product-of-sums)

$Y = \overline{A}.B + A.\overline{B} + A.B$  (minterm or sum-of-products)

| 1        |       | Ā       |   |   |   |

|----------|-------|---------|---|---|---|

| 1        | 1     | A·      | Y | В | A |

| ucts K-r | produ | Sum-of- | 0 | 0 | 0 |

| _        | _     |         | 1 | 1 | 0 |

| В        | В     |         | 1 | 0 | 1 |

|          | -     | A       | 1 | 1 | 1 |

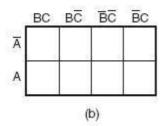

Minterm Karnaugh map and Maxterm Karnaugh map of the three variable Boolean function

$$Y = \overline{A}.\overline{B}.\overline{C} + \overline{A}.B.\overline{C} + A.\overline{B}.\overline{C} + A.B.\overline{C}$$

$$Y = (\overline{A} + \overline{B} + \overline{C}).(\overline{A} + B + \overline{C}).(A + \overline{B} + \overline{C}).(A + B + \overline{C})$$

| Α | В | С | Y |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

|   | BC    | BC      | вс      | ВŒ   |

|---|-------|---------|---------|------|

| A | 1     |         |         | 1    |

| Α | 1     |         |         | 1    |

|   | Sum-c | of-prod | lucts K | -map |

|   | B+C   | B+C      | B+C    | B+Շ  |

|---|-------|----------|--------|------|

| Ā | 1     |          |        | 1    |

| Α | 1     |          |        | 1    |

|   | Produ | uct-of-s | sums K | -map |

The truth table, Minterm Karnaugh map and Maxterm Karnaugh map of the four variable Boolean function

$$Y = \overline{A.B.C.D} + \overline{A.B.C.D} +$$

To illustrate the process of forming groups and then writing the corresponding minimized Boolean expression, The below figures respectively show minterm and maxterm Karnaugh maps for the Boolean functions expressed by the below equations. The minimized

## Number systems (2016-17)

expressions as deduced from Karnaugh maps in the two cases are given by Equation in the case of the minterm Karnaugh map and Equation in the case of the maxterm Karnaugh map:

### 1.6.2 Quine-McCluskey Tabular Method

The Quine–McCluskey tabular method of simplification is based on the complementation theorem, which says that XY +XY' =X. where X represents either a variable or a term or an expression and Y is a variable. This theorem implies that, if a Boolean expression contains two terms that differ only in one variable, then they can be combined together and replaced with a term that is smaller by one literal.Let us consider an example. Consider the following sum-of-products expression:

$$\overline{A}.B.C + \overline{A}.\overline{B}.D + A.\overline{C}.D + B.\overline{C}.\overline{D} + \overline{A}.B.\overline{C}.D$$

In the first step, we write the expanded version of the given expression. It can be written as follows:

$$\overline{A}.B.C.D + \overline{A}.B.C.\overline{D} + \overline{A}.\overline{B}.C.D + \overline{A}.\overline{B}.\overline{C}.D + A.B.\overline{C}.D + A.B.\overline{C}.D + A.B.\overline{C}.D + A.B.\overline{C}.D + A.B.\overline{C}.D + A.B.\overline{C}.D$$

$$+ \overline{A}.B.\overline{C}.\overline{D} + \overline{A}.B.\overline{C}.D$$

The formation of groups, the placement of terms in different groups and the first-round matching are shown as follows:

| 0  | 0   | 0                 | 1              |                                                      | -                                                    | 7                                                    |                                                       |                                                       | _                                                    |

|----|-----|-------------------|----------------|------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|------------------------------------------------------|

| 0  | 1   |                   |                | V                                                    | .0                                                   | 0                                                    | <del>, , , ,</del> ) ,                                | 1                                                     | 1                                                    |

|    |     | 0                 | 0              | ✓                                                    | 0                                                    | -                                                    | 0                                                     | 1                                                     | 1                                                    |

|    |     |                   |                |                                                      | <del></del>                                          | 0                                                    | 0                                                     | 1                                                     | 1                                                    |

| 0. | 0   | 1                 | 1              | ✓                                                    | 0                                                    | 1                                                    | 0                                                     | E                                                     | 1                                                    |

| 0  |     | 0                 | 1              | ✓                                                    | 0                                                    | 1                                                    | _                                                     | 0                                                     | 1                                                    |

| 0  | 1   | 1                 | 0              | ✓-                                                   | <del>=</del> 1                                       | 1                                                    | 0                                                     | 0                                                     | 1                                                    |

| 1. | 0   | 0                 | 1              | √                                                    |                                                      |                                                      |                                                       |                                                       |                                                      |

| 1  | 1   | 0                 | 0              | <b>√</b>                                             | 0                                                    | 4                                                    | 1                                                     | 1                                                     | 1                                                    |

| 0  | 1   | 1                 | 1              | ✓                                                    | 0                                                    | 1                                                    | <del>, </del>                                         | 1                                                     | 1                                                    |

| 1  | 1   | 0                 | 1              | ✓                                                    | -                                                    | i                                                    | 0                                                     | 1                                                     | V                                                    |

|    |     |                   |                |                                                      | 0                                                    | 1                                                    | 1                                                     | -                                                     | 1                                                    |

|    |     |                   |                |                                                      | 1                                                    | <u></u>                                              | 0                                                     | 1                                                     | 1                                                    |

|    |     |                   |                |                                                      | 1                                                    | 1                                                    | 0                                                     | -                                                     | 1                                                    |

|    | 1 0 | 1 0<br>1 1<br>0 1 | 1 1 0<br>0 1 1 | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |

The second round of matching begins with the table shown on the previous page. Each term in the first group is compared with every term in the second group. For instance, the first term in the first group 00–1 matches with the second term in the second group 01–1 to yield 0—1, which is recorded in the table shown below. The process continues until all terms have been compared for a possible match. Since this new table has only one group, the terms contained therein are all prime implicants. In the present example, the terms in the first and second tables have all found a match. But that is not always the case.

| A    | В                 | C               | D           |   |

|------|-------------------|-----------------|-------------|---|

| 0    | \$ <del></del>    | <del>5.</del> 3 | 1           | * |

| 7    | 82 <del>-11</del> | 0               | 1           | * |

| 0    | 1                 | -               | <del></del> | * |

| 1075 | 1                 | 0               | -           | * |

The next table is what is known as the prime implicant table. The prime implicant table contains all the original terms in different columns and all the prime implicants recorded in different rows as shown below:

| 0001 | 0011 | 0100 | 0101 | 0110 | 0111 | 1001 | 1100 | 1101 |      |                                |

|------|------|------|------|------|------|------|------|------|------|--------------------------------|

| ✓    | 1    |      | 1    |      | 1    |      |      |      | 01   | $P \rightarrow \overline{A}.D$ |

| 1    |      |      | 1    |      |      | ✓    |      | 1    | 01   | $Q \rightarrow \overline{C}.D$ |

|      |      | 1    | 1    | 1    | 1    |      |      |      | 01   | $R \rightarrow \overline{A}.B$ |

|      |      | 1    | 1    |      |      |      | 1    | 1    | -10- | $S \to B.\overline{C}$         |

Each prime implicant is identified by a letter. Each prime implicant is then examined one by one and the terms it can account for are ticked as shown. The next step is to write a product-of-sums expression using the prime implicants to account for all the terms. In the present illustration, it is given as follows.

$$(P+Q).(P).(R+S).(P+Q+R+S).(R).(P+R).(Q).(S).(Q+S)$$

Obvious simplification reduces this expression to PQRS which can be interpreted to mean that all prime implicants, that is, P, Q, R and S, are needed to account for all the original terms. Therefore, the minimized expression =  $\overline{A}.D + \overline{C}.D + \overline{A}.B + B.\overline{C}$ .

What has been described above is the formal method of determining the optimum set of prime implicants. In most of the cases where the prime implicant table is not too complex, the exercise can be done even intuitively. The exercise begins with identification of those terms that can be accounted for by only a single prime implicant. In the present example, 0011, 0110, 1001 and 1100 are such terms. As a result, P, Q, R and S become the essential prime implicants. The next step is to find out if any terms have not been covered by the essential prime implicants. In the

present case, all terms have been covered by essential prime implicants. In fact, all prime implicants are essential prime implicants in the present example. As another illustration, let us consider a product-of-sums expression given by

The procedure is similar to that described for the case of simplification of sum-of-products expressions. The resulting tables leading to identification of prime implicants are as follows:

| A | В | С | D | A   | В   | С   | D  |          | A | В    | С   | D |   | A | В | С   | D |   |

|---|---|---|---|-----|-----|-----|----|----------|---|------|-----|---|---|---|---|-----|---|---|

| 0 | 1 | 0 | 1 | 0   | 1   | 0   | 1  | ✓        | 0 | 1    | 100 | 1 | ✓ | _ | 1 | 750 | 1 | * |

| 0 | 1 | 1 | 1 | -   | 911 | 0.1 |    |          |   | 1    | 0   | 1 | 1 | - |   |     |   | _ |

| 1 | 1 | 0 | 1 | 0   | 1   | 1   | 1  | <b>V</b> |   |      |     |   |   |   |   |     |   |   |

| 1 | 1 | 1 | 0 | 1   | 1   | 0   | 1  | ✓        |   | 1    | 1   | 1 | 7 |   |   |     |   |   |

| 1 | 1 | 1 | 1 | 1   | 1   | 1   | 0  | 1        | 1 | 1    |     | 1 | 1 |   |   |     |   |   |

|   |   |   |   | 107 | 10  | 107 | 01 | 50       | 1 | 1    | 1   | 4 | * |   |   |     |   |   |

|   |   |   |   | 1   | 1   | 1   | 1  | 1        | 2 | - 17 |     |   | _ |   |   |     |   |   |

The prime implicant table is constructed after all prime implicants have been identified to look for the optimum set of prime implicants needed to account for all the original terms. The prime implicant table shows that both the prime implicants are the essential ones:

| 0101 | 0111     | 1101     | 1110       | 1111 | Prime implicants |

|------|----------|----------|------------|------|------------------|

|      |          |          | . <b>√</b> | 7    | 111-             |

| √    | <b>V</b> | <b>V</b> |            | ✓    | -1-1             |

The minimized expression =  $(\overline{A} + \overline{B} + \overline{C}) \cdot (\overline{B} + \overline{D})$ .

### **Possible Part B Questions:**

- 1. Convert  $(237)_{10}$  to Hexadecimal  $(?)_{16}$  and Octal  $(?)_8$

- 2. Convert (1011011) binary to (?)gray

- 3. State De-Morgans Law

- 4. Write Associative and Distributive Laws

- 5. List the binary codes.

- 6. Convert (43)<sub>10</sub> to (?)<sub>16 and</sub> (?)<sub>8</sub>

- 7. Convert (2567)<sub>8</sub> to (?)<sub>16 and</sub> (?)<sub>2</sub>

- 8. Convert (110010)<sub>2</sub> to (?)<sub>16 and</sub> (?)<sub>8</sub>

- 9. What are canonical forms

- 10. Convert (10010)<sub>2</sub> to (?)gray

- 11. Differentiate between POS and SOP.

- 12. Convert  $(10001)_{gray}$  to  $(?)_2$

- 13. Give the applications of K map

- 14. Convert (10010110)<sub>10</sub> to (?)<sub>16 and</sub> (?)<sub>8</sub>

- 15. What are don't care terms?

- 16. What is commutative law?

- 17. Define absorption law

- 18. Write Consensus theorem

- 19. Define principle of duality

- 20. What are weighted codes? Give one example

- 21. Classify binary codes.

- 22. Define non-weighted codes

- 23. Give the advantages of numbering system

- 24. List out the commonly used numbering systems

- 25. Why hexadecimal is preferred over octal numbering system

### **Possible Part C Questions:**

- 1. Explain in detail about numbering systems in detail

- 2. Write short notes on Binary, Octal, Decimal and Hexadecimal numbering systems

- 3. Describe in detail about binary codes

- 4. Write short notes on weighted and non-weighted codes

- 5. Explain numbering system conversions with an example

- 6. Describe Boolean postulates with examples

- 7. Write short notes on Alphanumeric codes and error detecting and correcting codes

- 8. Explain in detail about signed arithmetic with examples

- 9. State and prove Demorgans theorems

- 10. State and prove Boolean laws

- 11. Write short notes on Minterms, Maxterms, SOP and POS functions

- 12. Simplify the Boolean Function F(X,Y,Z) = XY + X'Z + YZ and implement using gates.

- 13. Simplify the Boolean Function F(X,Y)=XY+X'Y+X'Y'+Y'X and implement using universal gates

- 14. Using a K-map, find the POS form of  $F=\prod M$  (0,4,8,12,3,7,11,15) and implement

- 15. Minimize the following Boolean function using K-Map and draw the combinational circuit  $F(A,B,C,D) = \sum m (0,1,4,7,11,13,14,15) + \sum d(2,9)$

- 16. Minimize the following Boolean function using K-Map and draw the combinational circuit  $F(A,B,C,D) = \sum_{m} (0,1,2,4,6,8,10,13,14,15)$

- 17. Minimize the following Boolean function using K-Map and draw the combinational circuit  $F(A,B,C,D) = \prod M (0,1,4,7,11,13,14,15) + \sum d(2,9)$ 18. Find MSP for the function  $F(A,B,C,D) = \sum m (0,2,4,6,8,10,12,14)$

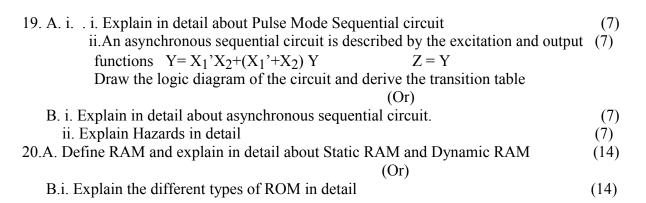

- 19.

# Karpagam Academy of Higher Education

(Established under Section 3 of UGC Act 1956)

Eachanari, Coimbatore-641 021. INDIA

# Department of Electronics and Communication Engineering Faculty of Engineering

# **DIGITAL ELECTRONICS**

LECTURE NOTES-UNIT II

**PREPARED BY** Dr.S.Bhavani,HOD/ECE

### 14BEEC403 DIGITAL ELECTRONICS

3003100

### **INTENDED OUTCOMES:**

- To introduce number systems and codes

- To introduce basic postulates of Boolean algebra and shows the correlation between Boolean expressions

- To introduce the methods for simplifying Boolean expressions

- To outline the formal procedures for the analysis and design of combinational circuits and sequential circuits

- To introduce the concept of memories and programmable logic devices.

### UNIT-I NUMBER SYSTEMS

Binary, Octal, Decimal, Hexadecimal-Number base conversions – complements – signed Binary numbers. Binary Arithmetic- Binary codes: Weighted –BCD-2421-Gray code-Excess 3 code-ASCII –Error detecting code – conversion from one code to another-Boolean postulates and laws –De-Morgan's Theorem- Principle of Duality- Boolean expression – Boolean function-Minimization of Boolean expressions – Sum of Products (SOP) –Product of Sums (POS)-Minterm- Maxterm- Canonical forms – Conversion between canonical forms –Karnaugh map Minimization – Don't care conditions.

### UNIT-II LOGIC GATES AND COMBINATIONAL CIRCUITS LOGIC GATES

AND, OR, NOT, NAND, NOR, Exclusive – OR and Exclusive – NOR- Implementations of Logic Functions using gates, NAND –NOR implementations –Multi level gate implementations. Multi output gate implementations. TTL and CMOS Logic and their characteristics –Tristate gates.

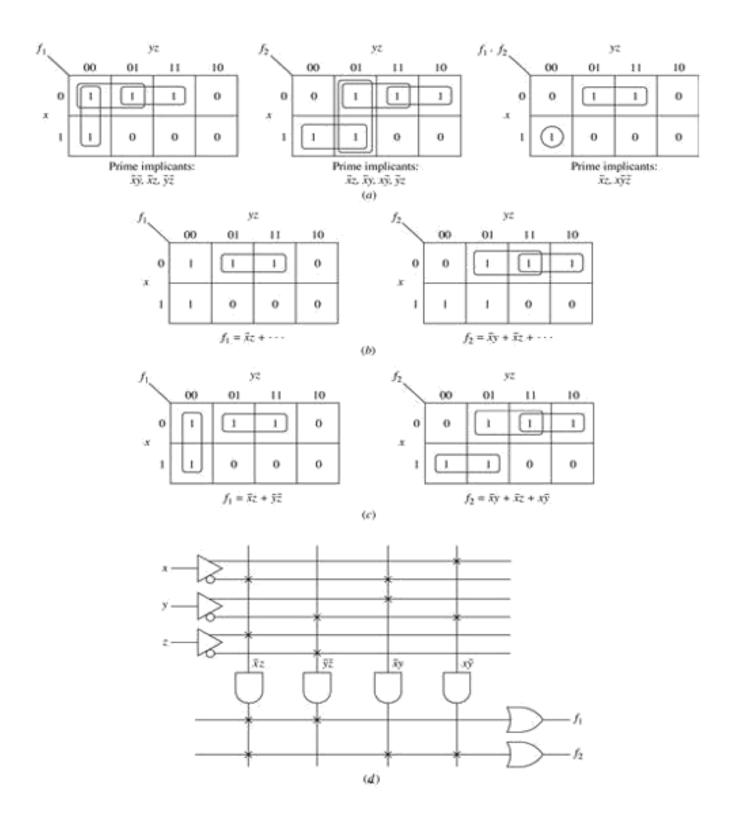

COMBINATIONAL CIRCUITS: Design procedure – Adders-Subtractors – Serial adder/Subtractor - Parallel adder/Subtractor- Carry look ahead adder- BCD adder- Magnitude Comparator- Multiplexer/ Demultiplexer- encoder / decoder – parity checker – code converters. Implementation of combinational logic using MUX, ROM, PAL and PLA.

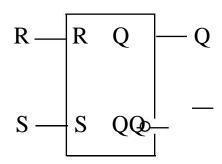

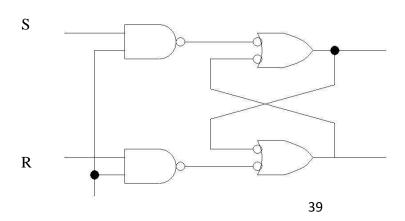

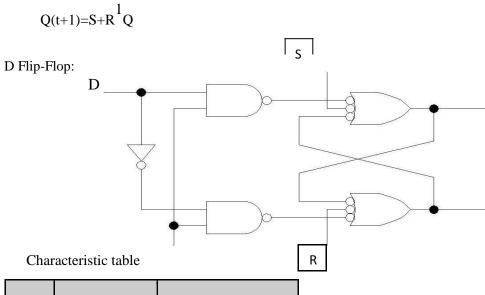

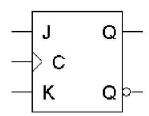

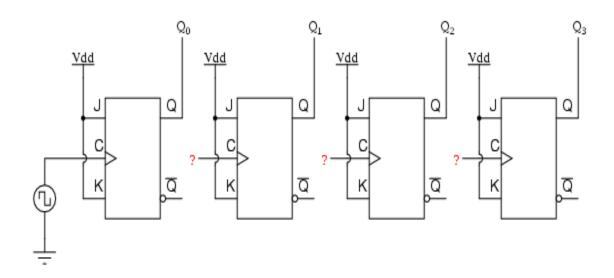

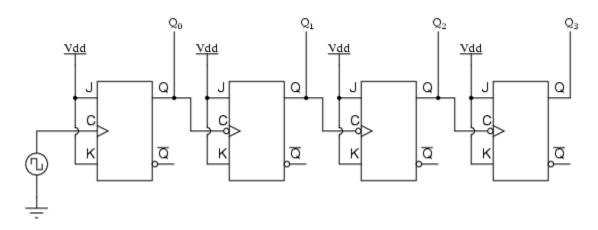

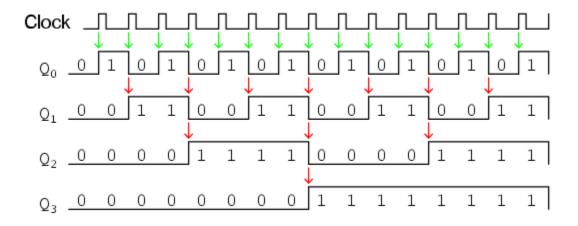

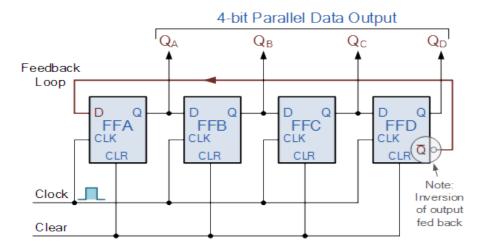

#### UNIT-III SEQUENTIAL CIRCUIT

Flip flops SR, JK, T, D and Master slave – Characteristic table and equation –Application table – Edge triggering –Level Triggering –Realization of one flip flop using other flip flops – Asynchronous / Ripple counters – Synchronous counters –Modulo – n counter –Classification of sequential circuits – Moore and Mealy -Design of Synchronous counters: state diagram- State table –State minimization –State assignment- ASM-Excitation table and maps-Circuit implementation - Register – shift registers- Universal shift register – Shift counters – Ring counters.

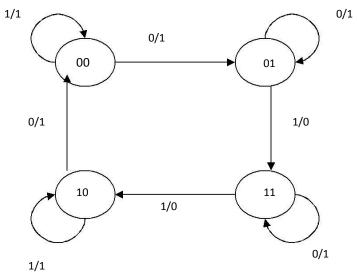

#### UNIT-IV ASYNCHRONOUS SEOUENTIAL CIRCUITS

Design of fundamental mode and pulse mode circuits – primitive state / flow table – Minimization of primitive state table –state assignment – Excitation table – Excitation map-cycles – Races –Hazards: Static –Dynamic –Essential –Hazards elimination.

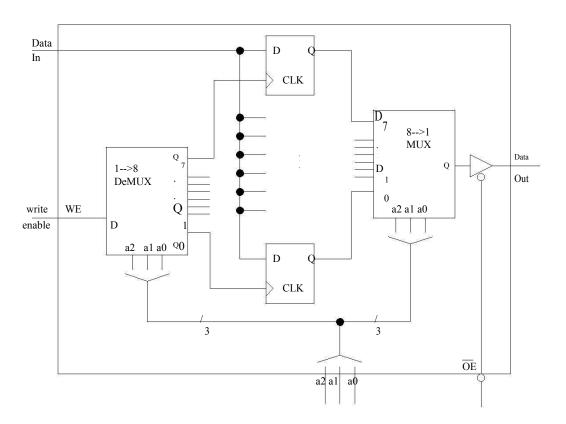

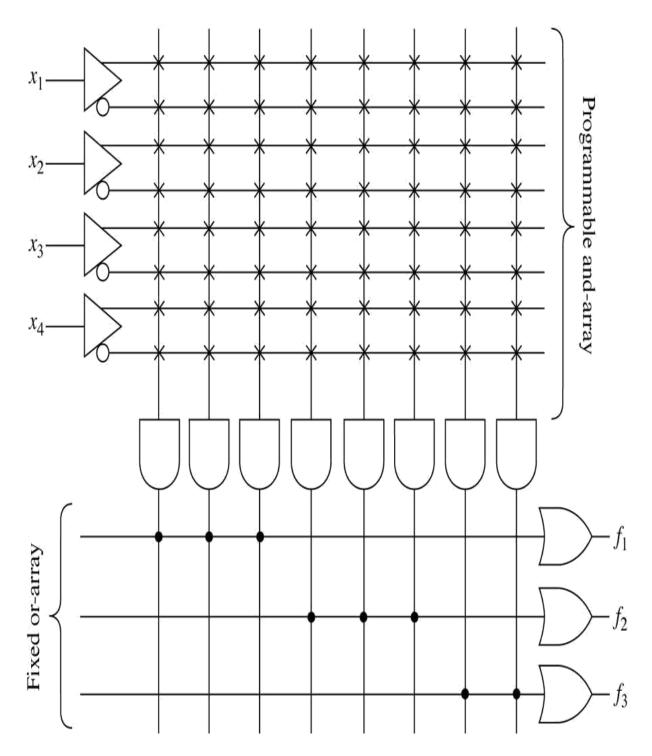

### UNIT-V MEMORY DEVICES

Classification of memories –RAM organization – Write operation –Read operation – Memory cycle - Timing wave forms – Memory decoding – memory expansion – Static RAM Cell-Bipolar RAM cell – MOSFET RAM cell –Dynamic RAM cell –ROM organization - PROM –EPROM – EEPROM –EAPROM –Programmable Logic Devices –Programmable Logic Array (PLA)-Programmable Array Logic (PAL)-Field Programmable Gate Arrays (FPGA).

### **TEXT BOOKS:**

| S.NO. | Author(s) Name    | Title of the book                           | Publisher                                   | Year of publication |

|-------|-------------------|---------------------------------------------|---------------------------------------------|---------------------|

| 1     | Morris Mano.M     | Digital Design                              | Prentice Hall of India Pvt. Ltd., New Delhi | 2003                |

| 2     | John M .Yarbrough | Digital Logic<br>Applications and<br>Design | Thomson- Vikas publishing house, New Delhi  | 2002                |

### **REFERENCES:**

| S.NO. | Author(s) Name                            | Title of the book                   | Publisher                                              | Year of publication |

|-------|-------------------------------------------|-------------------------------------|--------------------------------------------------------|---------------------|

| 1     | Salivahanan.S and<br>Arivazhagan.S        | Digital Circuits and Design         | Vikas Publishing House Pvt. Ltd, New Delhi             | 2004                |

| 2     | Charles H.Roth                            | Fundamentals of Logic Design        | Thomson Publication Company, New Delhi.                | 2003                |

| 3     | Donald P.Leach and<br>Albert Paul Malvino | Digital Principles and Applications | Tata McGraw Hill Publishing Company Limited, New Delhi | 2003                |

| 4     | Jain.R.P                                  | Modern Digital<br>Electronics       | Tata McGraw–Hill publishing company limited, New Delhi | 2003                |

| 5     | Thomas L. Floyd                           | Digital<br>Fundamentals             | Pearson Education, New<br>Delhi                        | 2003                |

### **WEBSITES:**

http://www.allaboutcircuits.com/vol\_2/chpt\_9/2.html http://www.educypedia.be/electronics/digital.html

# UNIT-II LOGIC GATES AND COMBINATIONAL CIRCUITS LOGIC GATES

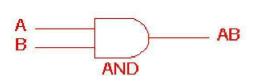

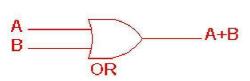

### 2.Logic gates

Digital systems are constructed using logic gates. Logic gates are digital circuits which has one or more inputs and a single output and which performs arithmetic and logical operations like addition, multiplication and inversion. There are three basic gates, which are called as AND, OR and NOT gates. The derived gates are gates which are derived using basic gates. Examples of derived gates are NAND, NOR, EXOR and EXNOR gates. The basic operations of all the gates are described below along with truth tables.

| 2 | Inpu | it AND | gate |

|---|------|--------|------|

|   | А    | В      | A.B  |

|   | 0    | 0      | 0    |

|   | 0    | 1      | 0    |

|   | 1    | 0      | 0    |

|   | 1    | 1      | 4    |

The AND gate is an electronic circuit that gives a **high** output (1) only if **all** its inputs are high. A dot (.) is used to show the AND operation i.e. A.B. Bear in mind that this dot is sometimes omitted i.e. AB

### OR gate

| 2 Inpu | ut OR g | ate |

|--------|---------|-----|

| Α      | В       | A+B |

| 0      | 0       | 0   |

| 0      | 1       | 1   |

| 1      | 0       | 1   |

| 1      | 1       | 1   |

The OR gate is an electronic circuit that gives a high output (1) if **one or more** of its inputs are high. A plus (+) is used to show the OR operation.

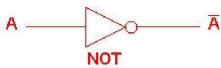

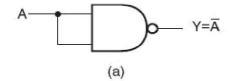

### **NOT** gate

| NOT g | jate      |

|-------|-----------|

| Α     | $\forall$ |

| 0     | 1         |

| 1     | 0         |

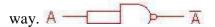

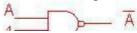

The NOT gate is an electronic circuit that produces an inverted version of the input at its output. It is also known as an *inverter*. If the input variable is A, then the inverted output is complement or inversion of A. This is also shown as A', or A with a bar over the top, as shown at the outputs. The diagrams below show two ways that the NAND logic gate can be configured to produce a NOT gate. It can also be done using NOR logic gates in the same

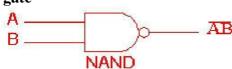

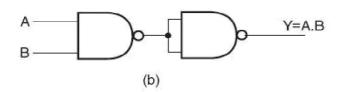

NAND gate

| 2 Inpu | it NAN | ID gate |

|--------|--------|---------|

| Α      | В      | A.B     |

| 0      | 0      | 1       |

| 0      | 1      | 1       |

| 1      | O      | 1       |

| 1      | 1      | 0       |

This is a NOT-AND gate which is equal to an AND gate followed by a NOT gate. The outputs of all NAND gates are high if **any** of the inputs are low. The symbol is an AND gate with a small circle on the output. The small circle represents inversion.

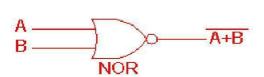

### **NOR** gate

| 2 Input NOR gate |   |                |  |

|------------------|---|----------------|--|

| Α                | В | <del>A+B</del> |  |

| 0                | 0 | 1              |  |

| 0                | 1 | 0              |  |

| 1                | 0 | 0              |  |

| _1_              | 1 | 0              |  |

This is a NOT-OR gate which is equal to an OR gate followed by a NOT gate. The outputs of all NOR gates are low if **any** of the inputs are high. The symbol is an OR gate with a small circle on the output. The small circle represents inversion.

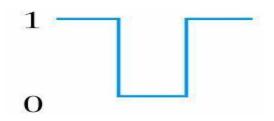

### **EXOR** gate

| 2 Input EXOR gate |   |     |  |

|-------------------|---|-----|--|

| Α                 | В | A⊕B |  |

| 0                 | 0 | 0   |  |

| 0                 | 1 | 1   |  |

| 1                 | 0 | 1   |  |

| 1                 | 1 | 0   |  |

The Excusive OR gate is a circuit which will give high output if both the inputs are high or low. An encircled plus sign( ①), is used to show the EX-OR operation.

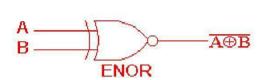

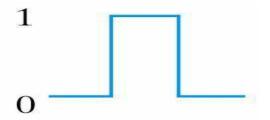

### **EXNOR** gate

| 2 Input EXNOR gate |   |     |  |

|--------------------|---|-----|--|

| Α                  | В | A⊕B |  |

| 0                  | 0 | 1   |  |

| 0                  | 1 | 0   |  |

| 1                  | 0 | 0   |  |

| 1                  | 1 | 9   |  |

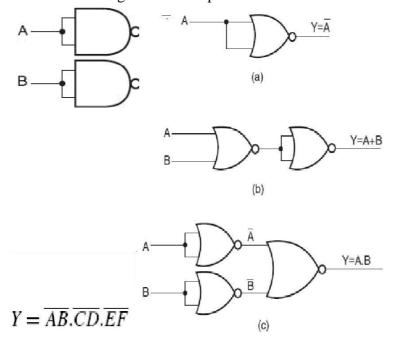

The 'Exclusive-NOR' gate circuit does the opposite to the EOR gate. It will give a low output if either, but not both, of its two inputs are high. The symbol is an EXOR gate with a small circle on the output. The small circle represents inversion. The NAND and NOR gates are called *universal functions* since with either one the AND and OR functions and NOT can be generated.

### Note:

A function in *sum of products* form can be implemented using NAND gates by replacing all AND and OR gates by NAND gates.A function in *product of sums* form can be implemented using NOR gates by replacing all AND and OR gates by NOR gates.

#### 2.1 Universal Gates

NAND, & NOR are called as Universal gates as all the other gates can be constructed using NAND and NOR

Implementation of basic logic gates using only NAND gates. a connection for open collector NAND gates. The output in this case would be

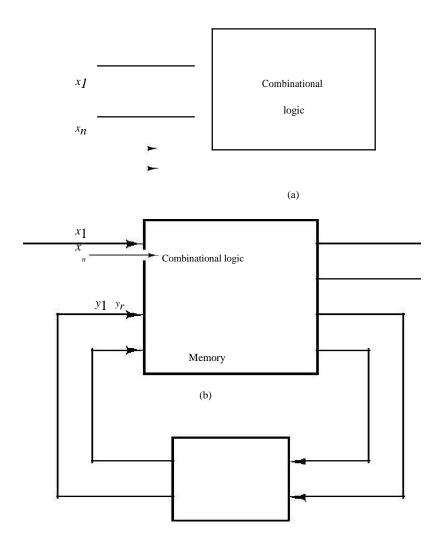

### 2.2 Combinational Circuits

A combinational circuit neither contains a periodic clock signal nor has any provisions for storage. There are no feedbacks involved and the output at all time is dependent on the inputs provided. The name combinational is derived from the combinations of logic gates used for such circuits. A sequential circuit involves feedback and has memory (so it is employed for designing RAM). It also has a periodic clock signal and hence the output is also a function of time in addition to being a function of inputs and previous outputs. The name sequential is derived as the output is produced in sequences as the clock circuit enables and disables the functioning. (A latch is also a sequential circuit but has no clock signal and hence is a special case. It is also the basic building block of any sequential circuit.)

### **Designing Combinational Circuits**

In general we have to do the following steps:

- 1. Problem description

- 2. Input/output of the circuit

- 3. Define truth table

- 4. Simplification for each output

- 5. Draw the circuit

### 2.3 ADDERS

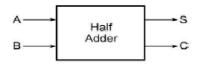

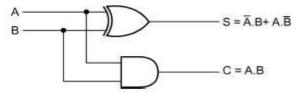

#### 2.3.1 Half-Adder

A half-adder is an arithmetic circuit block that can be used to add two bits. Such a circuit thus has two inputs that represent the two bits to be added and two outputs, with one producing the SUM output and the other producing the CARRY. Figure 3.2 shows the truth table of a half-adder, showing all possible input combinations and the corresponding outputs.

The Boolean expressions for the SUM and CARRY outputs are given by the equations below

SUM

$$S = A.\overline{B} + \overline{A}.B$$

CARRY  $C = A.B$

| Α | В | s | С |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

#### **Truth Table of Half Adder**

An examination of the two expressions tells that there is no scope for further simplification. While the first one representing the SUM output is that of an EX-OR gate, the second one representing the CARRY output is that of an AND gate. However, these two expressions can certainly be represented in different forms using various laws and theorems of Boolean algebra to illustrate the flexibility that the designer has in hardware-implementing as simple a combinational function as that of a half-adder.

**Logic Implementation of Half Adder**

Although the simplest way to hardware-implement a half-adder would be to use a two-input EX-OR gate for the SUM output and a two-input AND gate for the CARRY output, as shown in Fig. 3.3, it could also be implemented by using an appropriate arrangement of either NAND or NOR gates.

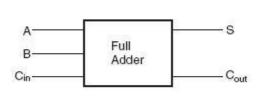

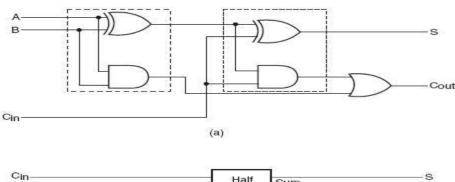

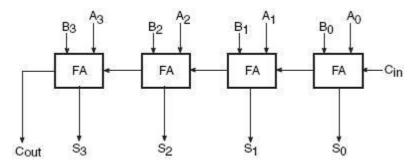

### 2.3.2 Full Adder

A full adder circuit is an arithmetic circuit block that can be used to add three bits to produce a SUM and a CARRY output. Such a building block becomes a necessity when it comes to adding binary numbers with a large number of bits. The full adder circuit overcomes the limitation of the half-adder, which can be used to add two bits only. Let us recall the procedure for adding larger binary numbers. We begin with the addition of LSBs of the two numbers. We record the sum under the LSB column and take the carry, if any, forward to the next higher column bits. As a result, when we add the next adjacent higher column bits, we would be required to add three bits if there were a carry from the previous addition. We have a similar situation for the other higher column bits. Also until we reach the MSB. A full adder is therefore essential for the hardware implementation of an adder circuit capable of adding larger binary numbers. A half-adder can be used for addition of LSBs only.

| Α | В | Cin | SUM (S) | Court |

|---|---|-----|---------|-------|

| 0 | 0 | 0   | 0       | 0     |

| 0 | 0 | 1   | 1       | 0     |

| 0 | 1 | 0   | 1       | 0     |

| 0 | 1 | 1   | 0       | 1.    |

| 1 | 0 | 0   | 1       | 0     |

| 1 | 0 | 1   | 0       | 1     |

| 1 | 1 | 0   | 0       | 1     |

| 1 | 1 | 1   | 1       | 1     |

**Truth Table of Full Adder**

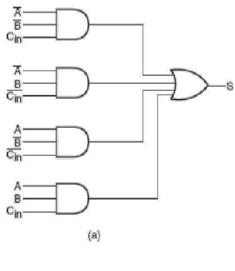

Figure shows the truth table of a full adder circuit showing all possible input combinations and corresponding outputs. In order to arrive at the logic circuit for hardware implementation of a full adder, we will firstly write the Boolean expressions for the two output variables, that is, the SUM and CARRY outputs, in terms of input variables. The Boolean expressions for the two output variables are given in Equation below for the SUM output (S) and in above Equation for the CARRY output (Cout):

$$\begin{split} S &= \overline{A}.\overline{B}.C_{\text{in}} + \overline{A}.B.\overline{C}_{\text{in}} + A.\overline{B}.\overline{C}_{\text{in}} + A.B.C_{\text{in}} \\ C_{\text{out}} &= \overline{A}.B.C_{\text{in}} + A.\overline{B}.C_{\text{in}} + A.B.\overline{C}_{\text{in}} + A.B.C_{\text{in}} \end{split}$$

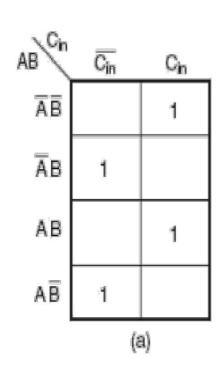

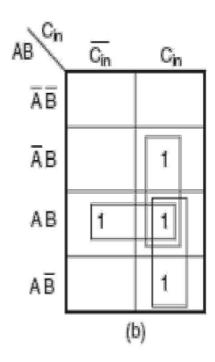

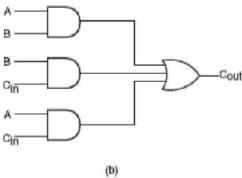

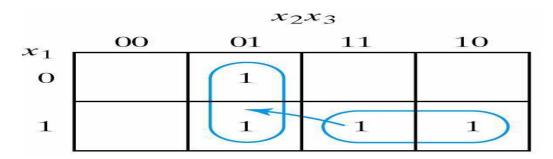

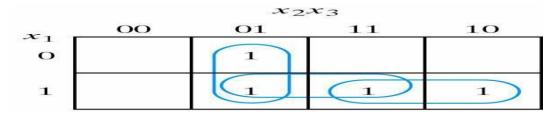

The next step is to simplify the two expressions. We will do so with the help of the Karnaugh mapping technique. Karnaugh maps for the two expressions are given in Fig. 3.5(a) for the SUM output and Fig. 3.5(b) for the CARRY output.

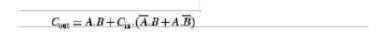

$$C_{\text{out}} = B.C_{\text{in}} + A.B + A.C_{\text{in}}$$

Figure shows the logic circuit diagram of the full adder. A full adder can also be seen to comprise two half-adders and an OR gate. The expressions for SUM and CARRY outputs can be rewritten as follows:

$$S = \overline{C}_{\text{in}} \cdot (\overline{A} \cdot B + A \cdot \overline{B}) + C_{\text{in}} \cdot (A \cdot B + \overline{A} \cdot \overline{B})$$

$$S = \overline{C}_{\text{in}} \cdot (\overline{A} \cdot B + A \cdot \overline{B}) + C_{\text{in}} \cdot (\overline{\overline{A} \cdot B + A \cdot \overline{B}})$$

Similarly, the expression for CARRY output can be rewritten as follows:

$$\begin{split} C_{\text{out}} &= B.C_{\text{in}} \cdot (A + \overline{A}) + A.B + A.C_{\text{in}} \cdot (B + \overline{B}) \\ &= A.B + A.B.C_{\text{in}} + \overline{A}.B.C_{\text{in}} + A.B.C_{\text{in}} + A.\overline{B}.C_{\text{in}} = A.B + A.B.C_{\text{in}} + \overline{A}.B.C_{\text{in}} + A.\overline{B}.C_{\text{in}} \\ &= A.B.(1 + C_{\text{in}}) + C_{\text{in}} \cdot (\overline{A}.B + A.\overline{B}) \end{split}$$

Karnaugh Map for the sum and carry out of a full adder

### Logic circuit diagram of full adder

Logic Implementation of a full adder with Half Adders

### 2.3.3 Half-Subtractor

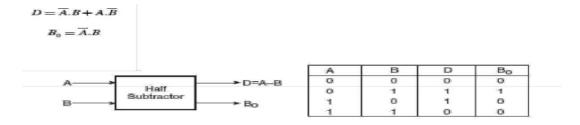

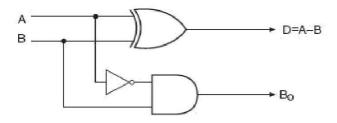

We will study the use of adder circuits for subtraction operations in the following pages. Before we do that, we will briefly look at the counterparts of half-adder and full adder circuits in the half-subtractor and full subtractor for direct implementation of subtraction operations using logic gates. A half-subtractor is a combinational circuit that can be used to subtract one binary digit from another to produce a DIFFERENCE output and a BORROW output. The BORROW output here specifies whether a 1' has been borrowed to perform the subtraction. The truth table of a half-subtractor, as shown in Fig. 3.9, explains this further. The Boolean expressions for the two outputs are given by the equations

Logic Diagram of a Half Subtractor

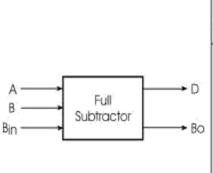

### 2.3.4 Full Subtractor

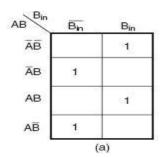

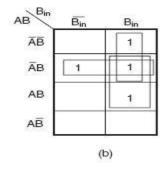

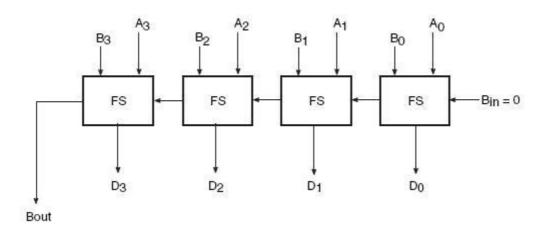

A full subtractor performs subtraction operation on two bits, a minuend and a subtrahend, and also takes into consideration whether a \_1' has already been borrowed by the previous adjacent lower minuend bit or not. As a result, there are three bits to be handled at the input of a full subtractor, namely the two bits to be subtracted and a borrow bit designated as Bin . There are two outputs, namely the DIFFERENCE output D and the BORROW output Bo The Boolean expressions for the two output variables are given by the equations

$$\begin{split} D &= \overline{A}.\overline{B}.B_{\text{in}} + \overline{A}.B.\overline{B}_{\text{in}} + A.\overline{B}.\overline{B}_{\text{in}} + A.B.B_{\text{in}} \\ B_{\text{o}} &= \overline{A}.\overline{B}.B_{\text{in}} + \overline{A}.B.\overline{B}_{\text{in}} + \overline{A}.B.B_{\text{in}} + A.B.B_{\text{in}} \end{split}$$

| Minuend<br>(A) | Subtrahend<br>(B) | Borrow<br>In (Bin) | Difference<br>(D) | Borrow<br>Out (B <sub>0</sub> ) |

|----------------|-------------------|--------------------|-------------------|---------------------------------|

| 0              | 0                 | 0                  | 0                 | 0                               |

| 0              | 0                 | 1                  | - 1               | - 1                             |

| 0              | 1                 | 0                  | প                 | 1                               |

| 0              | -1                | 1                  | 0                 | 1                               |

| 1              | 0.                | 0                  | 1                 | 0                               |

| 4              | 0                 | 1                  | 0                 | 0                               |

| 1 1            | 1                 | 0                  | 0                 | 0                               |

| 1              | 1                 | 1                  | 81                | 1 .                             |

### Truth Table of Full Subtractor

### K Maps for Difference and Borrow outputs.

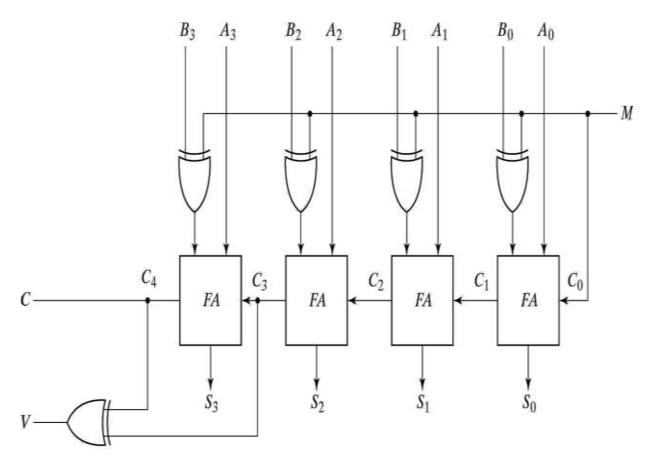

### 2.3.5 Adder- Subtractor

- The addition and subtraction can be combined into one circuit with one common binary adder (see next slide).

- The mode M controls the operation. When M=0 the circuit is an adder when M=1 the circuit is subtractor. It can be don by using exclusive-OR for each Bi and M. Note that  $1 \oplus x = x''$  and  $0 \oplus x = x$

Fig. 4-13 4-Bit Adder Subtractor

# 2.4 BINARY TO GRAY CONVERTER

In this circuit we'll convert BINARY numbers to GRAY numbers. Following is the truth table for it:

|            | В3 | B2 | B1 | В0 | G3 | G2 | G1 | G0 |

|------------|----|----|----|----|----|----|----|----|

| 0.         | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| 1.         | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 1  |

| 2.         | 0  | 0  | 1  | 0  | 0  | 0  | 1  | 1  |

| 3.         | 0  | 0  | 1  | 1  | 0  | 0  | 1  | 0  |

| 4.         | 0  | 1  | 0  | 0  | 0  | 1  | 1  | 0  |

| 5.         | 0  | 1  | 0  | 1  | 0  | 1  | 1  | 1  |

| 6.         | 0  | 1  | 1  | 1  | 0  | 1  | 0  | 0  |

| 8.         | 1  | 0  | 0  | 0  | 1  | 1  | 0  | 0  |

| 9.         | 1  | 0  | 0  | 1  | 1  | 1  | 0  | 1  |

| 10.        | 1  | 0  | 1  | 0  | 1  | 1  | 1  | 1  |

| 11.        | 1  | 0  | 1  | 1  | 1  | 1  | 1  | 0  |

| 12.        | 1  | 1  | 0  | 0  | 1  | 0  | 1  | 0  |

| 13.        | 1  | 1  | 0  | 1  | 1  | 0  | 1  | 1  |

| 14.        | 1  | 1  | 1  | 0  | 1  | 0  | 0  | 1  |

| <u>15.</u> | 1  | 1  | 1  | 1  | 1  | 0  | 0  | 0  |

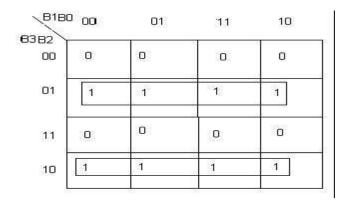

## K-MAP FOR G3:

| B1B0       | 00 | 01 | 11 | 10 |

|------------|----|----|----|----|

| 63B2<br>00 | 0  | 0  | 0  | 0  |

| 01         | 0  | 0  | 0  | 0  |

| 11         | 1  | 1  | 1  | 1  |

| 10         | 1  | 1  | 1  | 1  |

**Equation for G3=B3**

## K-MAP FOR G2:

Equation for G2= B3' B2 + B3 B2'= B3 XOR B2

## K-MAP FOR G1:

**Equation for G1= B1' B2 + B1 B2'= B1 XOR B2**

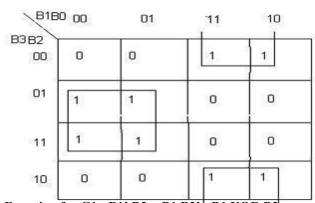

#### K-MAP FOR G0:

| B1E | 30 00 | 01 | 11 | 10 |

|-----|-------|----|----|----|

| 00  | О     | 1  | 0  | 1  |

| 01  | 0     | .1 | 0  | 1  |

| 11  | 0     | 1  |    | 1  |

| 10  | 0     | 1  | 0  | 1  |

**Equation for G0= B1' B0 + B1 B0'= B1 XOR B0**

#### 2.5 COMPARATORS

- It is a combinational circuit that compares to numbers and determines their relative magnitude .

- For example to design a comparator for 2 bit binary numbers A (A1A0) and B (B1B0) we do the following steps:

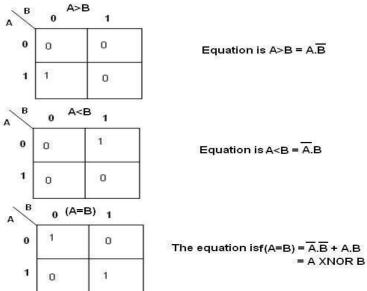

**1-bit comparator:** Let's begin with 1 bit comparator and from the name we can easily make out that this circuit would be used to compare 1 bit binary numbers.f we list all the input combinations at the input then we get the following table describing the corresponding outputs.

| A | В | <b>f</b> ( <b>A</b> > <b>B</b> ) | f (A=B) f | ( <b>A<b< b="">)</b<></b> |

|---|---|----------------------------------|-----------|---------------------------|

| 0 | 0 | 0                                | 1         | 0                         |

| 1 | 0 | 1                                | 0         | 0                         |

| 0 | 1 | 0                                | 0         | 1                         |

| 1 | 1 | 0                                | 1         | 0                         |

And now we find the equations using K-maps each for f (A>B), f (A=B) and f (A<B) as follow:

or we can write the equation for f(A=B) as  $\overline{A.B} + \overline{A.B} = \overline{f(A>B) + f(A<B)}$

## 2.6 BCD ADDER

| Number | С | S8 | S4 | S2 | S1 |

|--------|---|----|----|----|----|

| 0      | 0 | 0  | 0  | 0  | 0  |

| 1      | 0 | 0  | 0  | 0  | 1  |

| 2      | 0 | 0  | 0  | 1  | 0  |

| 3      | 0 | 0  | 0  | 1  | 1  |

| 4      | 0 | 0  | 1  | 0  | 0  |

| 5      | 0 | 0  | 1  | 0  | 1  |

| 6      | 0 | 0  | 1  | 1  | 0  |

| 7      | 0 | 0  | 1  | 1  | 1  |

| 8      | 0 | 1  | 0  | 0  | 0  |

| 9      | 0 | 1  | 0  | 0  | 1  |

| Number | С | S8 | S4 | S2 | S1 |

| 10     | 1 | 0  | 0  | 0  | 0  |

| 11     | 1 | 0  | 0  | 0  | 1  |

| 12     | 1 | 0  | 0  | 1  | 0  |

| 13     | 1 | 0  | 0  | 1  | 1  |

| 14     | 1 | 0  | 1  | 0  | 0  |

| 15     | 1 | 0  | 1  | 0  | 1  |

| 16     | 1 | 0  | 1  | 1  | 0  |

| 17     | 1 | 0  | 1  | 1  | 1  |

| 18     | 1 | 1  | 0  | 0  | 0  |

| 19     | 1 | 1  | 0  | 0  | 1  |

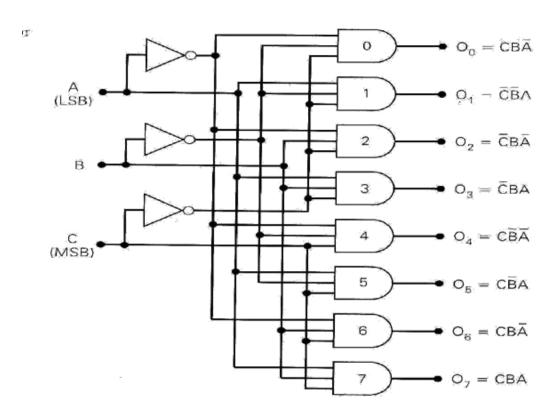

## 2.7 DECODERS

Accepts a value and decodes it

Output corresponds to value of *n* inputs

It Consists of:

Inputs (n)

Outputs (2n, numbered from 0 to 2n - 1)

Selectors / Enable (active high or active low)

| С  | В  | Α     | 07  | 06 | 05 | 04 | О3 | $O_2$ | $O_1$ | Oo |  |

|----|----|-------|-----|----|----|----|----|-------|-------|----|--|

| 0  | O  | 0     | 0   | 0  | 0  | O  | 0  | Ô     | 0     | 1  |  |

| 0  | 0  | 7     | 0   | 0  | 0  | 0  | 0  | 0     | 1     | 0  |  |

| 0  | 1  | 0     | 0   | 0  | 0  | 0  | 0  | า     | O     | 0  |  |

| 0  | 7  | 1     | 0   | 0  | 0  | 0  | 1  | Ó     | 0     | 0  |  |

| 1  | 0  | 0     | 0   | 0  | 0  | वे | 0  | O     | O     | 0  |  |

| 1  | 0  | 1     | 0   | Ö  | 7  | 0  | 0  | 0     | 0     | Ô  |  |

| 1. | 1. | 0     | 0   | 7  | 0  | O  | 0  | 0     | O     | 0  |  |

| 1  | 1. | - n - | 1 1 | 0  | 0  | 0  | Ö  | Ó     | Õ     | Ō  |  |

| Octai<br>Numbar | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | _ a | b | ç |

|-----------------|----|----|----|----|----|----|----|----|-----|---|---|

| .0              | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0 | 0 |

| 1               | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0 | 1 |

| 2               | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0   | 1 | 0 |

| 3               | -0 | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0   | 1 | 1 |

| 4               | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 1   | 0 | 0 |

| 5               | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 1   | 0 | 1 |

| 6               | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 1   | 1 | 0 |

| 7               | 0  | 0  | ũ  | 0  | 0  | 0  | 0  | 1  | 1   | 1 | 1 |

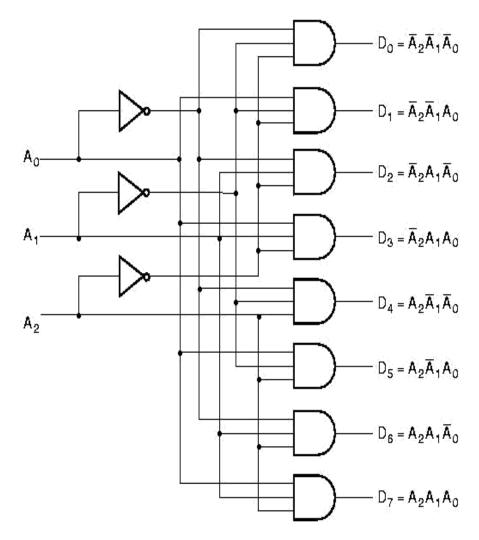

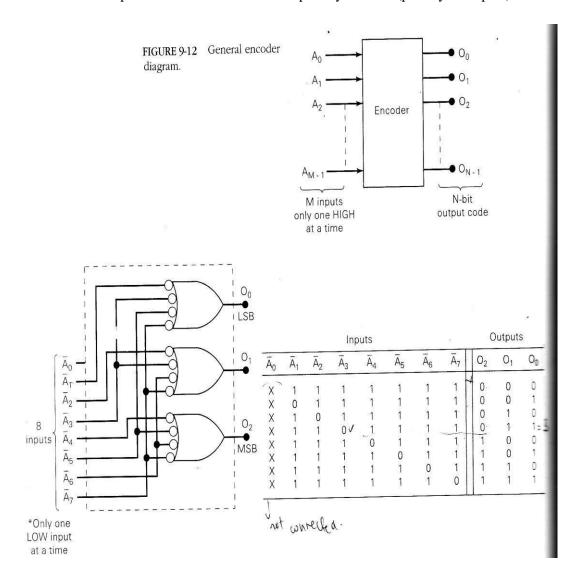

## 2.8 ENCODER

Perform the inverse operation of a decoder. It has 2n (or less) input lines and n output lines

| D <sub>7</sub> | $D_6$ | $D_5$ | $D_4$ | $\mathbf{D}_3$ | $D_2$ | $\mathbf{D_1}$ | D <sub>0</sub> | $A_2$ | $\mathbf{A}_1$ | $\mathbf{A}_0$ |

|----------------|-------|-------|-------|----------------|-------|----------------|----------------|-------|----------------|----------------|

| 0              | 0     | 0     | ۵     | 0              | 0     | 0              | 1              | 0     | 0              | 0              |

| 0              | O     | o     | 0     | 0              | 0     | 1              | 0              | 0     | 0              | 1              |

| 0              | 0     | 0     | 0     | 0              | 1     | 0              | 0              | 0     | 1              | 0              |

| 0              | 0     | o     | 0     | 1              | 0     | 0              | 0              | 0     | 1              | 1              |

| 0              | 0     | 0     | 1     | 0              | 0     | 0              | 0              | 1     | 0              | 0              |

| 0              | o     | 1     | 0     | 0              | 0     | 0              | 0              | 1     | 0              | 1              |

| 0              | 1     | o     | O     | O              | 0     | 0              | 0              | 1     | 1              | 0              |

| 1              | 0     | 0     | 0     | 0              | 0     | 0              | 0              | 1     | i              | 1              |

Can be implemented with 3 OR gates A0 = D1 + D3 + D5 + D7;

$$A1 = D2 + D3 + D6 + D7;$$

$$A2 = D4 + D5 + D6 + D7;$$

If more than 2 inputs are active we need to use priority encoder (priority for inputs)

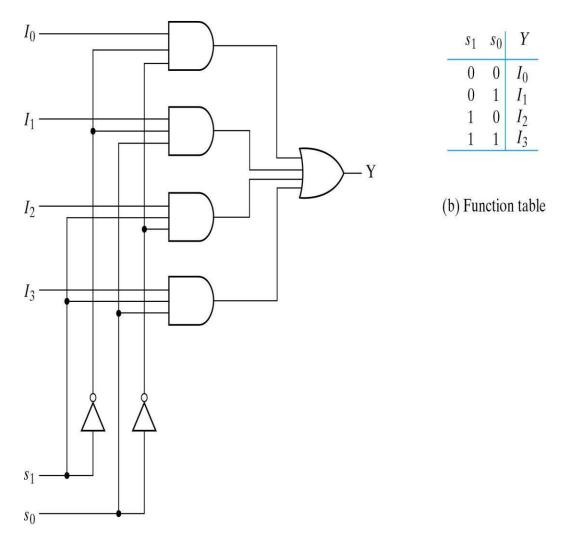

#### 2.9 MULTIPLEXER

- It is a combinational circuit that selects binary information from one of the input lines and directs it to a single output line

- Usually there are 2n input lines and n selection lines whose bit combinations determine which input line is selected

- For example for 2-to-1 multiplexer if selection S is zero then IO has the path to output and if S is one I1 has the path to output

(a) Logic diagram

Fig. 4-25 4-to-1-Line Multiplexer

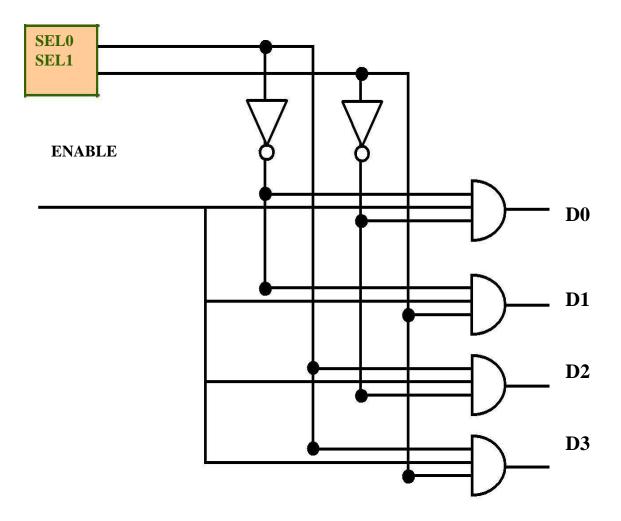

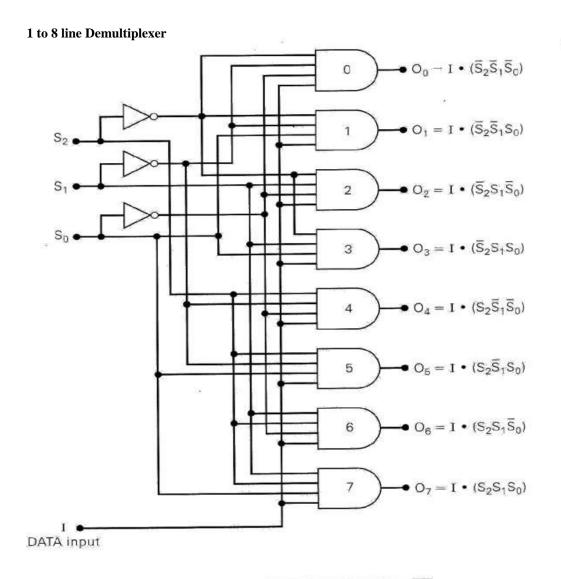

# 2.10 DEMULTIPLEXER

| ENABLE | SEL1 | SEL2 | D0 | D1 | D2 | D3 |

|--------|------|------|----|----|----|----|

| 0      | X    | X    | 0  | 0  | 0  | 0  |

| 1      | 0    | 0    | 1  | 0  | 0  | 0  |

| 1      | 0    | 1    | 0  | 1  | 0  | 0  |

| 1      | 1    | 0    | 0  | 0  | 1  | 0  |

| 1      | 1    | 1    | 0  | 0  | 0  | 1  |

| SELE  | CT c | ode |   |    |    | (     | TUC   | PUTS  |       |    | 22 |

|-------|------|-----|---|----|----|-------|-------|-------|-------|----|----|

| $S_2$ | Si   | So  |   | 07 | 06 | $O_5$ | $O_4$ | $O_3$ | $O_2$ | 01 | 00 |

| 0     | 0    | О   |   | 0  | 0  | 0     | O     | 0     | 0     | 0  | 1  |

| 0     | 0    | 1   |   | 0  | 0  | 0     | 0     | 0     | 0     | 1  | 0  |

| 0     | -1   | 0   |   | 0  | 0  | 0     | 0     | 0     | 1     | 0  | 0  |

| 0     | 1    | 1   |   | 0  | 0  | 0     | 0     | 1     | 0     | 0  | 0  |

| 1     | 0    | 0   |   | 0  | 0  | 0     | 1     | 0     | 0     | 0  | 0  |

| 1     | 0    | 1   |   | 0  | 0  | 1     | 0     | 0     | 0     | 0  | 0  |

| 1     | 1    | 0   |   | 0  | I  | 0     | 0     | 0     | 0     | 0  | 0  |

| 1     | 1    | 1   | 4 | 1  | 0  | 0     | 0     | 0     | 0     | 0  | 0  |

Note: I is the data input

# Karpagam Academy of Higher Education

(Established under Section 3 of UGC Act 1956)

Eachanari, Coimbatore-641 021. INDIA

# Department of Electronics and Communication Engineering Faculty of Engineering

# **DIGITAL ELECTRONICS**

**LECTURE NOTES**

PREPARED BY Dr.S.Bhavani,HOD/ECE

#### 14BEEC403 DIGITAL ELECTRONICS

3003100

#### **INTENDED OUTCOMES:**

- To introduce number systems and codes

- To introduce basic postulates of Boolean algebra and shows the correlation between Boolean expressions

- To introduce the methods for simplifying Boolean expressions

- To outline the formal procedures for the analysis and design of combinational circuits and sequential circuits

- To introduce the concept of memories and programmable logic devices.

#### UNIT-I NUMBER SYSTEMS

Binary, Octal, Decimal, Hexadecimal-Number base conversions – complements – signed Binary numbers. Binary Arithmetic- Binary codes: Weighted –BCD-2421-Gray code-Excess 3 code-ASCII –Error detecting code – conversion from one code to another-Boolean postulates and laws –De-Morgan's Theorem- Principle of Duality- Boolean expression – Boolean function-Minimization of Boolean expressions – Sum of Products (SOP) –Product of Sums (POS)-Minterm- Maxterm- Canonical forms – Conversion between canonical forms –Karnaugh map Minimization – Don't care conditions.

#### UNIT-II LOGIC GATES AND COMBINATIONAL CIRCUITS LOGIC GATES

AND, OR, NOT, NAND, NOR, Exclusive – OR and Exclusive – NOR- Implementations of Logic Functions using gates, NAND –NOR implementations –Multi level gate implementations—Multi output gate implementations. TTL and CMOS Logic and their characteristics –Tristate gates.

COMBINATIONAL CIRCUITS: Design procedure – Adders-Subtractors – Serial adder/Subtractor - Parallel adder/Subtractor- Carry look ahead adder- BCD adder- Magnitude Comparator- Multiplexer/ Demultiplexer- encoder / decoder – parity checker – code converters. Implementation of combinational logic using MUX, ROM, PAL and PLA.

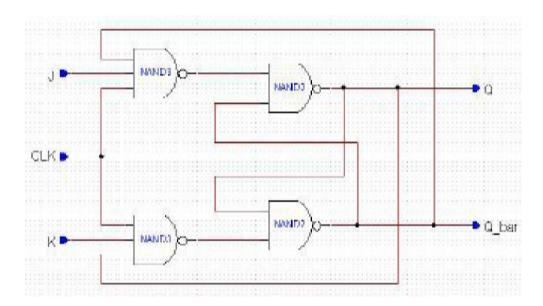

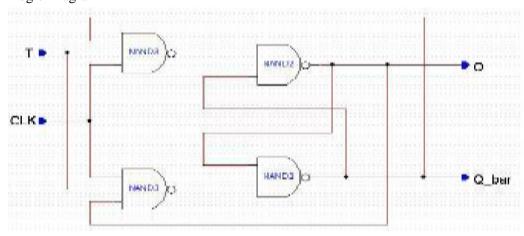

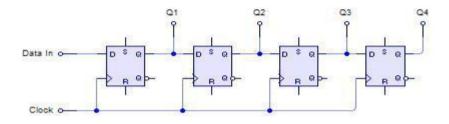

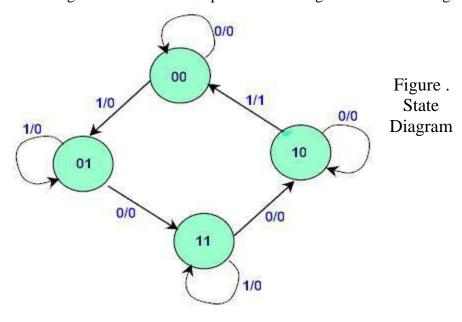

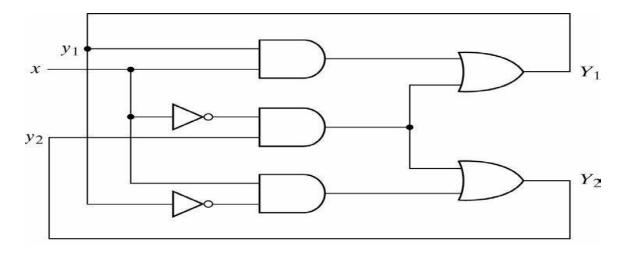

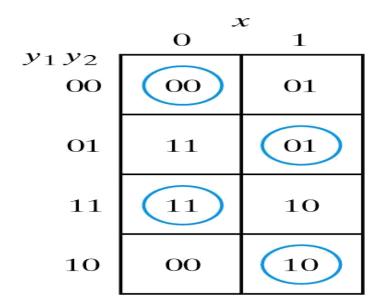

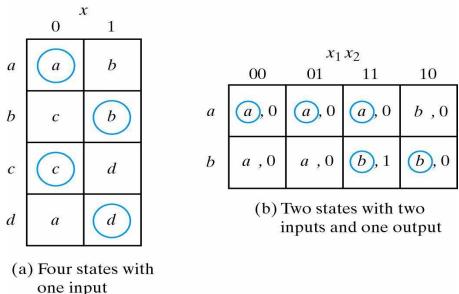

#### UNIT-III SEQUENTIAL CIRCUIT

Flip flops SR, JK, T, D and Master slave – Characteristic table and equation –Application table – Edge triggering –Level Triggering –Realization of one flip flop using other flip flops – Asynchronous / Ripple counters – Synchronous counters –Modulo – n counter –Classification of sequential circuits – Moore and Mealy -Design of Synchronous counters: state diagram- State table –State minimization –State assignment- ASM-Excitation table and maps-Circuit implementation - Register – shift registers- Universal shift register – Shift counters – Ring counters.

#### UNIT-IV ASYNCHRONOUS SEOUENTIAL CIRCUITS

Design of fundamental mode and pulse mode circuits – primitive state / flow table – Minimization of primitive state table –state assignment – Excitation table – Excitation map-cycles – Races –Hazards: Static –Dynamic –Essential –Hazards elimination.

## UNIT-V MEMORY DEVICES

Classification of memories –RAM organization – Write operation –Read operation – Memory cycle - Timing wave forms – Memory decoding – memory expansion – Static RAM Cell-Bipolar RAM cell – MOSFET RAM cell –Dynamic RAM cell –ROM organization - PROM –EPROM – EEPROM –EAPROM –Programmable Logic Devices –Programmable Logic Array (PLA)-Programmable Array Logic (PAL)-Field Programmable Gate Arrays (FPGA).

## **TEXT BOOKS:**

| S.NO. | Author(s) Name    | Title of the book                           | Publisher                                   | Year of publication |

|-------|-------------------|---------------------------------------------|---------------------------------------------|---------------------|