KARPAGAM ACADEMY OF HIGHER EDUCATION (Deemed to be University) (Established Under Section 3 of UGC Act 1956) Coimbatore – 641 021. (For the candidates admitted from 2018 onwards) DEPARTMENT OF PHYSICS

## SUBJECT: PHYSICS OF ELECTRONIC DEVICES AND CIRUITS SEMESTER : IV SUBJECT CODE: 18PHU302

**Objective:** This paper is intended to give an idea about the physics of different electronic devices and physics of communication electronics.

### UNIT-I

**Devices:** Characteristic and small signal equivalent circuits of UJT and JFET. Metal semiconductor Junction. Metal oxide semiconductor (MOS) device. Ideal MOS and Flat Band voltage. SiO2-Si based MOS. MOSFET– their frequency limits. Enhancement and Depletion Mode MOSFETS, CMOS. Charge coupled devices. Tunnel diode.

### UNIT -II

**Power supply and Filters:** Block Diagram of a Power Supply, Qualitative idea of C and L Filters. IC Regulators, Line and load regulation, Short circuit protection. Active and Passive Filters, Low Pass, High Pass, Band Pass and band Reject Filters.

#### **UNIT-III**

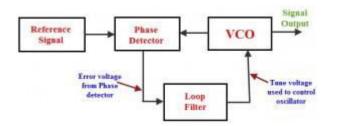

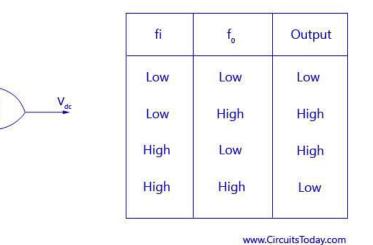

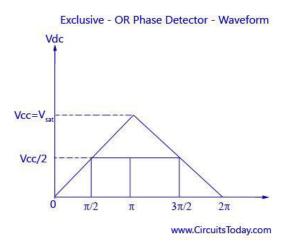

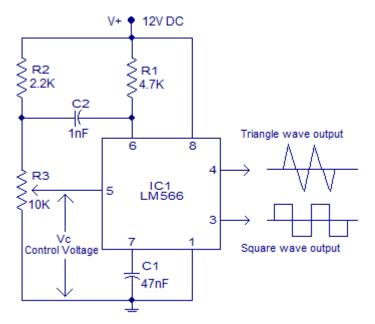

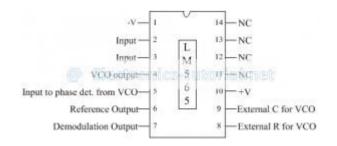

**Phase Locked Loop(PLL):** Basic Principles, Phase detector(XOR & edge triggered), Voltage Controlled Oscillator (Basics, varactor). Loop Filter– Function, Loop Filter Circuits, transient response, lock and capture. Basic idea of PLL IC (565 or 4046).

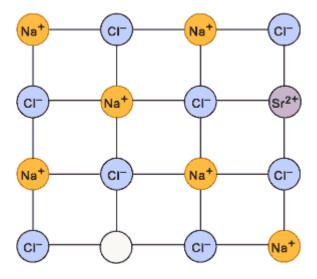

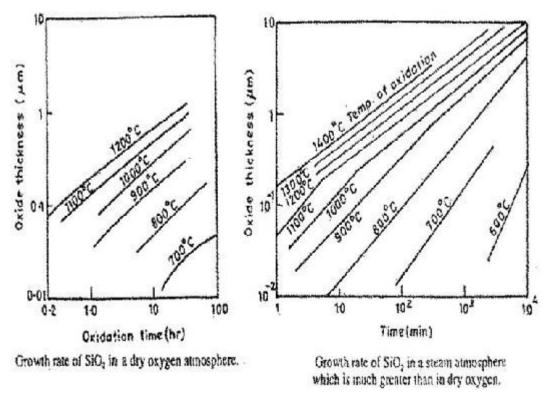

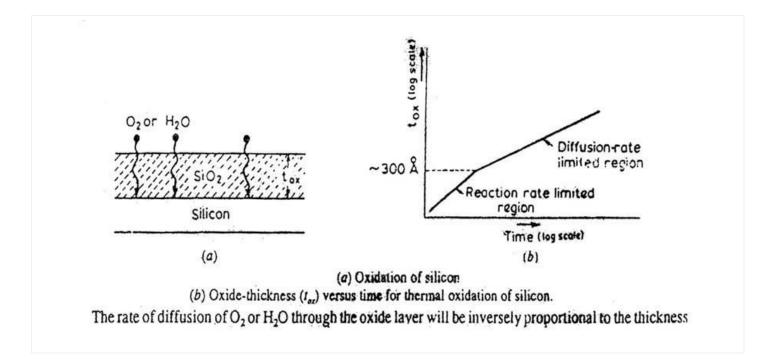

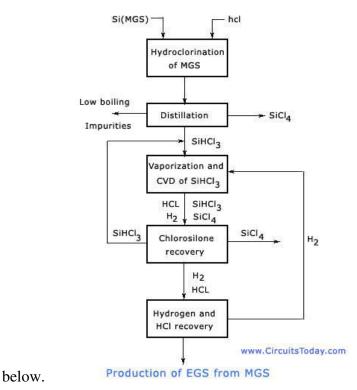

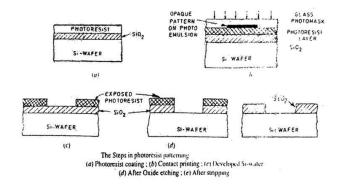

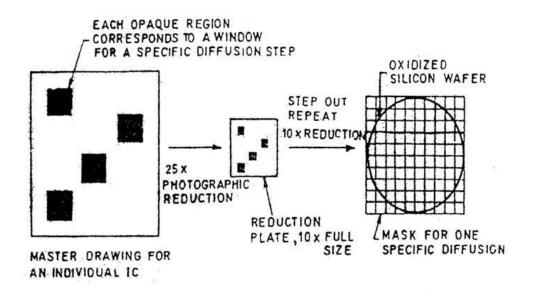

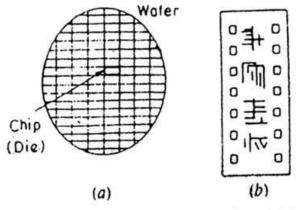

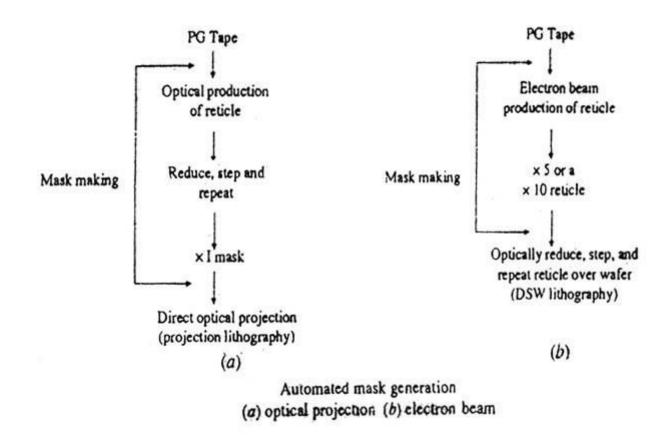

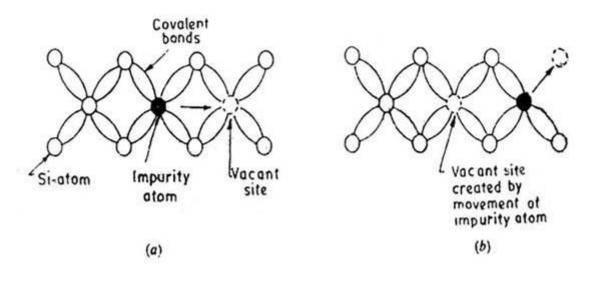

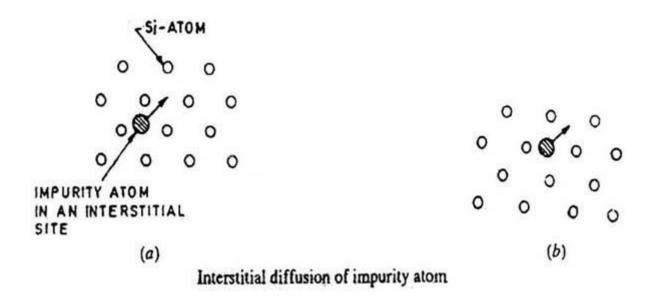

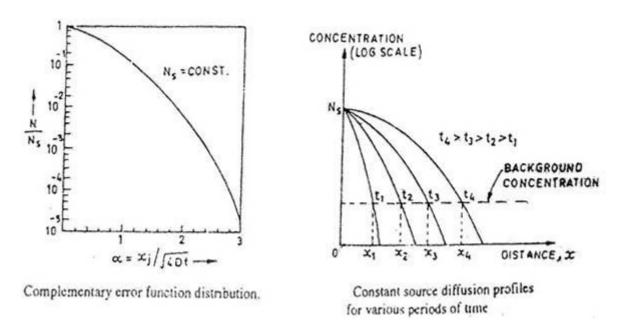

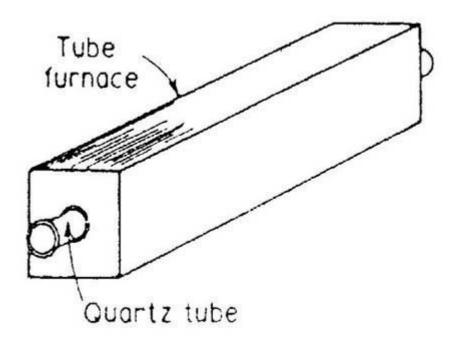

**Processing of Devices:** Basic process flow for IC fabrication, Electronic grade silicon. Crystal plane and orientation. Defects in the lattice. Oxide layer. Oxidation Technique for Si.

Metallization technique. Positive and Negative Masks. Optical lithography. Electron lithography. Feature size control and wet anisotropic etching. Lift off Technique. Diffusion and implantation.

#### UNIT-IV

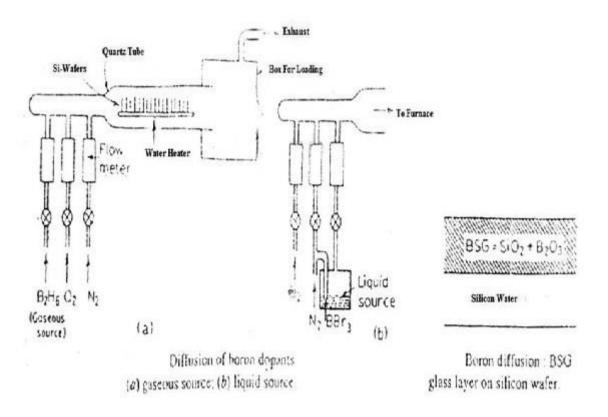

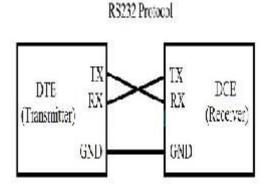

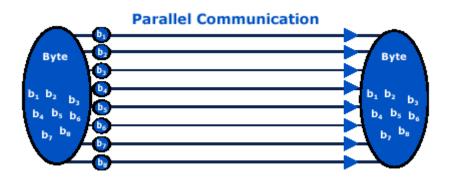

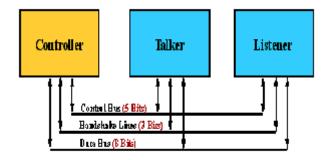

**Digital Data Communication Standards:** Serial Communications: RS232, Handshaking, Implementation of RS232 on PC. Universal Serial Bus (USB): USB standards, Types and elements of USB transfers. Devices (Basic idea of UART). Parallel Communications: General Purpose Interface Bus (GPIB), GPIB signals and lines, Handshaking and interface management, Implementation of a GPIB on a PC. Basic idea of sending data through a COM port.

#### **UNIT-V**

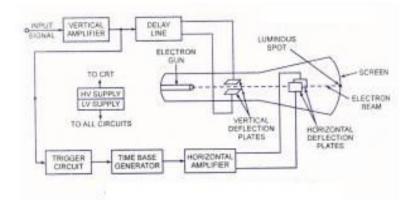

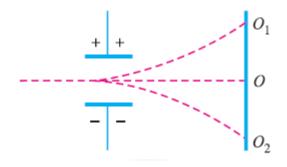

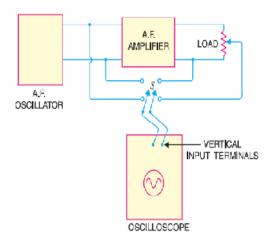

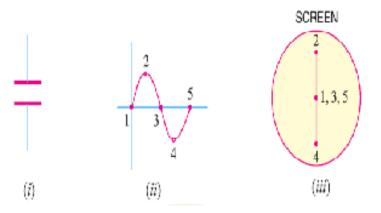

**Introduction to CRO:** Block Diagram of CRO. Applications of Oscilloscope: (1) Study of Waveform, (2) Measurement of Voltage, Current, Frequency and Phase Difference.

**Power Supply:** Half-wave Rectifiers. Centre-tapped and Bridge Full-wave Rectifiers Calculation of Ripple Factor and Rectification Efficiency, Basic idea about capacitor filter, Zener Diode and Voltage Regulation Timer IC: IC 555 Pin diagram and its application as Multivibrators: Astable and Monostable Multivibrators using transistors

#### **TEXT BOOKS**

- 1. Electronic devices and integrated circuits, A.K. Singh, 2011, PHI Learning Pvt. Ltd.

- Physics of Semiconductor Devices, By Massimo Rudan, 2015, Springer New York Heidelberg Dordrecht London, ISBN- 978-1-4939-1150-9, Semiconductor Devices: Physics and Technology by S. M. Sze, John Wiley & Sons Singapore Pte. Limited, 2012, ISBN - 9780470873670.

#### **REFERENCE BOOKS:**

- 1. Linear Integrated Circuits & Applications By U.A.Bakshi, A.P.Godse, Technical Publications Pune, 2010, ISBN- 9788184317619.

- 2. Electronic Devices and Circuits by G. S. N. Raju, I.K. International Publishing House Pvt. Limited, 2010, ISBN- 9788189866020.Semiconductor Physics and Devices, D.A.

Neamen, 2011, 4th Edition, McGraw Hill, Principles of Electronic Communication Systems by Louis Frenzel, McGraw-Hill Education, 2015, ISBN – 9780073373850.

Introduction to Instrumentation and Measurements, Third Edition, By Robert B. Northrop, CRC press, Taylor and Francis group, ISBN – 978-1-4822-1482-6

## KARPAGAM ACADEMY OF HIGHER EDUCATION

CLASS: II BSc PHYSCIS COURSE NAME: PHYSICS OF ELECTRONIC DEVICES AND CIRCUITS COURSE CODE: 18PHU302 UNIT: I (Devices) BATCH-2018-2021

## <u>UNIT-I</u>

### SYLLABUS

Devices:Characteristic and small signal equivalent circuits of UJT and JFET. Metal semiconductor Junction. Metal oxide semiconductor (MOS) device Ideal MOS and Flat Band voltage. SiO2-Si based MOS. MOSFET– their frequency limits. Enhancement and Depletion Mode MOSFETS, CMOS. Charge coupled devices. Tunnel diode.

### JUNCTION FIELD EFFECT TRANSISTOR

The Field Effect Transistor is a three terminal unipolar semiconductor device that has very similar characteristics to those of their Bipolar Transistor counterparts ie, high efficiency, instant operation, robust and cheap and can be used in most electronic circuit applications to replace their equivalent bipolar junction transistors (BJT) cousins.

Field effect transistors can be made much smaller than an equivalent BJT transistor and along with their low power consumption and power dissipation makes them ideal for use in integrated circuits such as the CMOS range of digital logic chips.

The field effect transistor is a three terminal device that is constructed with no PN-junctions within the main current carrying path between the Drain and the Source terminals, which correspond in function to the Collector and the Emitter respectively of the bipolar transistor. The current path between these two terminals is called the "channel" which may be made of either a P-type or an N-type semiconductor material. The control of current flowing in this channel is achieved by varying the voltage applied to the Gate. As their name implies, Bipolar Transistors are "Bipolar" devices because they operate with both types of charge carriers, Holes and Electrons. The Field Effect Transistor on the other hand is a "Unipolar" device that depends only on the conduction of electrons (N-channel) or holes (P-channel).

The Field Effect Transistor has one major advantage over its standard bipolar transistor cousins, in that their input impedance, (Rin) is very high, (thousands of Ohms), while the BJT is comparatively low. This very high input impedance makes them very sensitive to input voltage signals, but the price of this high sensitivity also means that they can be easily damaged by static electricity.

There are two main types of field effect transistor, the Junction Field Effect Transistor and the Insulated-gate Field Effect Transistor or IGFET), which is more commonly known as the standard Metal Oxide Semiconductor Field Effect Transistor .

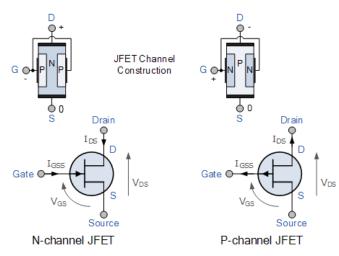

. The Junction Field Effect Transistor (JUGFET or JFET) has no PN-junctions but instead has a narrow piece of high resistivity semiconductor material forming a "Channel" of either N-type or P-type silicon for the majority carriers to flow through with two ohmic electrical connections at either end commonly called the Drain and the Source respectively. There are two basic configurations of junction field effect transistor, the N-channel JFET and the P-channel JFET. The N-channel JFET's channel is doped with donor impurities meaning that the flow of current through the channel is negative (hence the term N-channel) in the form of electrons.

Likewise, the P-channel JFET's channel is doped with acceptor impurities meaning that the flow of current through the channel is positive (hence the term P-channel) in the form of holes. N-channel JFET's have a greater channel conductivity (lower resistance) than their equivalent P-channel types, since electrons have a higher mobility through a conductor compared to holes. This makes the N-channel JFET's a

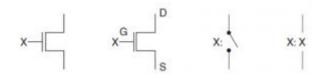

The symbols and basic construction for both configurations of JFETs are shown below.

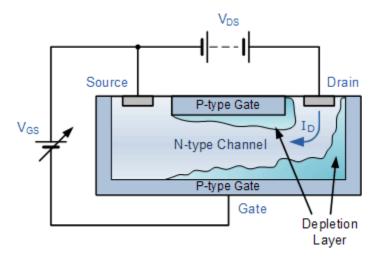

The semiconductor "channel" of the Junction Field Effect Transistor is a resistive path through which a voltage  $V_{DS}$  causes a current  $I_D$  to flow and as such the junction field effect transistor can conduct current equally well in either direction. As the channel is resistive in nature, a voltage gradient is thus formed down the length of the channel with this voltage becoming less positive as we go from the Drain terminal to the Source terminal. The result is that the PN-junction therefore has a high reverse bias at the Drain terminal and a lower reverse bias at the Source terminal. This bias causes a "depletion layer" to be formed within the channel and whose width increases with the bias.

The magnitude of the current flowing through the channel between the Drain and the Source terminals is controlled by a voltage applied to the Gate terminal, which is a reverse-biased. In an N-channel JFET this Gate voltage is negative while for a P-channel JFET the Gate voltage is positive. The main

difference between the JFET and a BJT device is that when the JFET junction is reverse-biased the Gate current is practically zero, whereas the Base current of the BJT is always some value greater than zero.

Biasing of an N-channel JFET

The cross sectional diagram above shows an N-type semiconductor channel with a P-type region called the Gate diffused into the N-type channel forming a reverse biased PN-junction and it is this junction which forms the depletion region around the Gate area when no external voltages are applied. JFETs are therefore known as depletion mode devices. This depletion region produces a potential gradient which is of varying thickness around the PN-junction and restrict the current flow through the channel by reducing its effective width and thus increasing the overall resistance of the channel itself. Then we can see that the most-depleted portion of the depletion region is in between the Gate and the Drain, while the least-depleted area is between the Gate and the Source. Then the JFET's channel conducts with zero bias voltage applied (ie, the depletion region has near zero width).

With no external Gate voltage ( $V_G = 0$ ), and a small voltage ( $V_{DS}$ ) applied between the Drain and the Source, maximum saturation current ( $I_{DSS}$ ) will flow through the channel from the Drain to the Source restricted only by the small depletion region around the junctions. If a small negative voltage ( $-V_{GS}$ ) is now applied to the Gate the size of the depletion region begins to increase reducing the overall effective area of the channel and thus reducing the current flowing through it, a sort of "squeezing" effect takes place. So by applying a reverse bias voltage increases the width of the depletion region which in turn reduces the conduction of the channel.

Since the PN-junction is reverse biased, little current will flow into the gate connection. As the Gate voltage ( $-V_{GS}$ ) is made more negative, the width of the channel decreases until no more current flows

between the Drain and the Source and the FET is said to be "pinched-off" (similar to the cut-off region for a BJT). The voltage at which the channel closes is called the "pinch-off voltage", ( $V_P$ ).

### JFET Channel Pinched-off

In this pinch-off region the Gate voltage,  $V_{GS}$  controls the channel current and  $V_{DS}$  has little or no effect.

### JFET-Model

The result is that the FET acts more like a voltage controlled resistor which has zero resistance when  $V_{GS} = 0$  and maximum "ON" resistance ( $R_{DS}$ ) when the Gate voltage is very negative. Under normal operating conditions, the JFET gate is always negatively biased relative to the source. It is essential that the Gate voltage is never positive since if it is all the channel current will flow to the Gate and not to the Source, the result is damage to the JFET. Then to close the channel:

- No Gate voltage (V<sub>GS</sub>) and V<sub>DS</sub> is increased from zero.

- No V<sub>DS</sub> and Gate control is decreased negatively from zero.

- V<sub>DS</sub> and V<sub>GS</sub> varying.

The P-channel Junction Field Effect Transistor operates the same as the N-channel above, with the following exceptions: 1). Channel current is positive due to holes, 2). The polarity of the biasing voltage needs to be reversed.

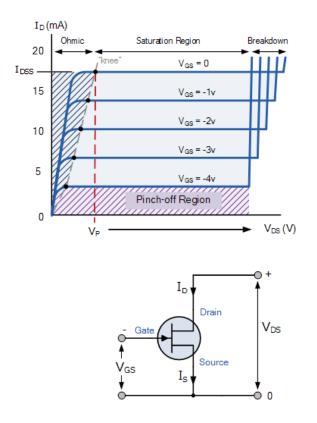

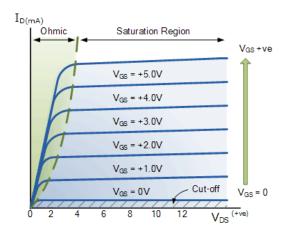

The output characteristics of an N-channel JFET with the gate short-circuited to the source is given as

The voltage  $V_{GS}$  applied to the Gate controls the current flowing between the Drain and the Source terminals.  $V_{GS}$  refers to the voltage applied between the Gate and the Source while  $V_{DS}$  refers to the voltage applied between the Drain and the Source.

Because a Junction Field Effect Transistor is a voltage controlled device, "NO current flows into the gate!" then the Source current ( $I_S$ ) flowing out of the device equals the Drain current flowing into it and therefore ( $I_D = I_S$ ).

The characteristics curves example shown above, shows the four different regions of operation for a JFET and these are given as:

- Ohmic Region When V<sub>GS</sub> = 0 the depletion layer of the channel is very small and the JFET acts like a voltage controlled resistor.

- Cut-off Region This is also known as the pinch-off region were the Gate voltage, V<sub>GS</sub> is sufficient to cause the JFET to act as an open circuit as the channel resistance is at maximum.

- Saturation or Active Region The JFET becomes a good conductor and is controlled by the Gate-Source voltage, (V<sub>GS</sub>) while the Drain-Source voltage, (V<sub>DS</sub>) has little or no effect.

- Breakdown Region The voltage between the Drain and the Source, (V<sub>DS</sub>) is high enough to causes the JFET's resistive channel to break down and pass uncontrolled maximum current.

The characteristics curves for a P-channel junction field effect transistor are the same as those above, except that the Drain current  $I_D$  decreases with an increasing positive Gate-Source voltage,  $V_{GS}$ . The Drain current is zero when  $V_{GS} = V_P$ . For normal operation,  $V_{GS}$  is biased to be somewhere between  $V_P$  and 0. Then we can calculate the Drain current,  $I_D$  for any given bias point in the saturation or active region as follows:

Drain current in the active region.

$I_{D = I_{DSS}} [1 - V_{GS} / V_p]^2$

Note that the value of the Drain current will be between zero (pinch-off) and  $I_{DSS}$  (maximum current). By knowing the Drain current  $I_D$  and the Drain-Source voltage  $V_{DS}$  the resistance of the channel ( $I_D$ ) is given as:

Drain-Source channel resistance.

$R_{DS} = \Delta V_{DS} / \Delta I_D = 1/g_m$

Where:  $g_m$  is the "transconductance gain" since the JFET is a voltage controlled device and which represents the rate of change of the Drain current with respect to the change in Gate-Source voltage.

### Modes of FET's

Like the bipolar junction transistor, the field effect transistor being a three terminal device is capable of three distinct modes of operation and can therefore be connected within a circuit in one of the following configurations.

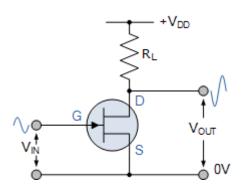

Common Source (CS) Configuration

In the Common Source configuration the input is applied to the Gate and its output is taken from the Drain as shown. This is the most common mode of operation of the FET due to its high input impedance and good voltage amplification and as such Common Source amplifiers are widely used. The common source mode of FET connection is generally used audio frequency amplifiers and in high input impedance pre-amps and stages. Being an amplifying circuit, the output signal is 180° "out-of-phase" with the input.

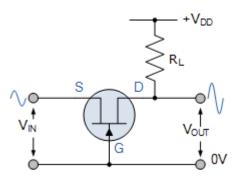

Common Gate (CG) Configuration

In the Common Gate configuration the input is applied to the Source and its output is taken from the Drain with the Gate connected directly to ground (0v) as shown. The high input impedance feature of the previous connection is lost in this configuration as the common gate has a low input impedance, but a high output impedance. This type of FET configuration can be used in high frequency circuits or in impedance matching circuits were a low input impedance needs to be matched to a high output impedance. The output is "in-phase" with the input.

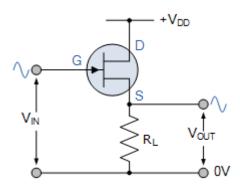

Common Drain (CD) Configuration

In the Common Drain configuration the input is applied to the Gate and its output is taken from the Source. The common drain or "source follower" configuration has a high input impedance and a low output impedance and near-unity voltage gain so is therefore used in buffer amplifiers. The voltage gain of the source follower configuration is less than unity, and the output signal is "in-phase",  $0^{\circ}$  with the input signal. This type of configuration is referred to as "Common Drain" because there is no signal available at the drain connection, the voltage present,  $+V_{DD}$  just provides a bias. The output is in-phase with the input.

### **The JFET Amplifier**

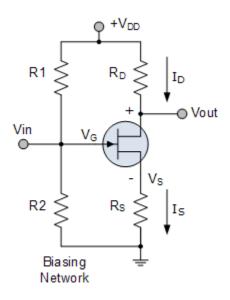

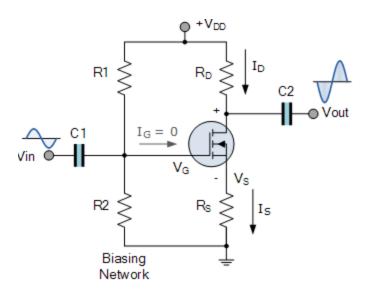

Like the bipolar junction transistor, JFET's can be used to make single stage class A amplifier circuits with the JFET common source amplifier and characteristics being very similar to the BJT common emitter circuit. The main advantage JFET amplifiers have over BJT amplifiers is their high input impedance which is controlled by the Gate biasing resistive network formed by R1 and R2 as shown.

Biasing of JFET Amplifier

This common source (CS) amplifier circuit is biased in class "A" mode by the voltage divider network formed by resistors R1 and R2. The voltage across the Source resistor  $R_S$  is generally set to be about one quarter of  $V_{DD}$ , ( $V_{DD}$ /4) but can be any reasonable value. The required Gate voltage can then be calculated from this  $R_S$  value. Since the Gate current is zero, ( $I_G = 0$ ) we can set the required DC quiescent voltage by the proper selection of resistors R1 and R2.

The control of the Drain current by a negative Gate potential makes the junction Field Effect Transistor useful as a switch and it is essential that the Gate voltage is never positive for an N-channel JFET as the channel current will flow to the Gate and not the Drain resulting in damage to the JFET. The principals of operation for a P-channel JFET are the same as for the N-channel JFET, except that the polarity of the voltages need to be reversed.

### MOSFET

### The MOSFET – Metal Oxide FET

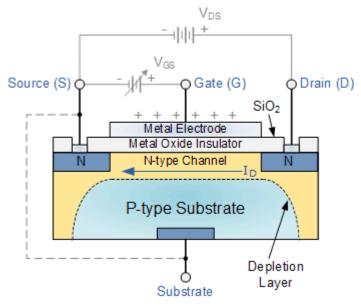

The IGFET or MOSFET is a voltage controlled field effect transistor that differs from a JFET in that it has a "Metal Oxide" Gate electrode which is electrically insulated from the main semiconductor n-channel or p-channel by a very thin layer of insulating material usually silicon dioxide, commonly known as glass. This ultra thin insulated metal gate electrode can be thought of as one plate of a capacitor. The isolation of the controlling Gate makes the input resistance of the MOSFET extremely high way up in the Mega-ohms (M $\Omega$ ) region thereby making it almost infinite.

As the Gate terminal is isolated from the main current carrying channel"NO current flows into the gate" and just like the JFET, the MOSFET also acts like a voltage controlled resistor were the current flowing through the main channel between the Drain and Source is proportional to the input voltage. Also like the JFET, the MOSFETs very high input resistance can easily accumulate large amounts of static charge resulting in the MOSFET becoming easily damaged unless carefully handled or protected.

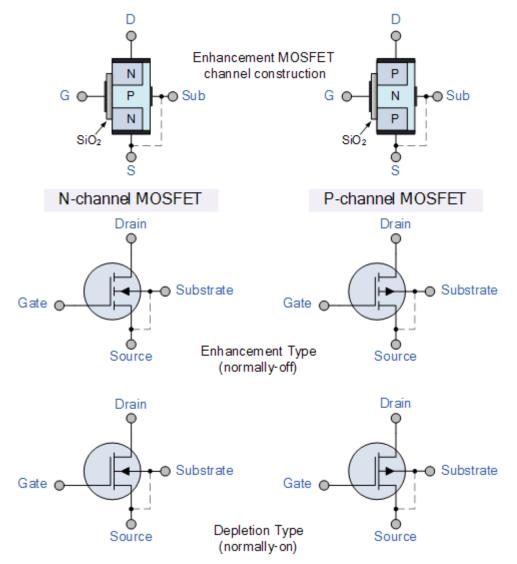

MOSFETs are also three terminal devices with a Gate, Drain and Source and both P-channel (PMOS) and N-channel (NMOS) MOSFETs are available. The main difference this time is that MOSFETs are available in two basic forms:

Depletion Type – the transistor requires the Gate-Source voltage, (V<sub>GS</sub>) to switch the device "OFF". The depletion mode MOSFET is equivalent to a "Normally Closed" switch.

Enhancement Type – the transistor requires a Gate-Source voltage, (V<sub>GS</sub>) to switch the device "ON". The enhancement mode MOSFET is equivalent to a "Normally Open" switch.

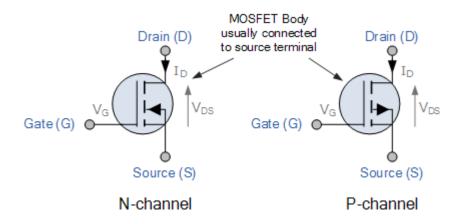

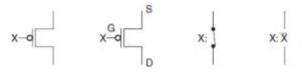

The symbols and basic construction for both configurations of MOSFETs are shown below.

The four MOSFET symbols above show an additional terminal called the Substrate and is not normally used as either an input or an output connection but instead it is used for grounding the substrate. It connects to the main semi conductive channel through a diode junction to the body or metal tab of the MOSFET. Usually in discrete type MOSFETs, this substrate lead is connected internally to the source terminal. When this is the case, as in enhancement types it is omitted from the symbol for clarification.

The line between the drain and source connections represents the semi conductive channel. If this is a solid unbroken line then this represents a "Depletion" (normally-ON) type MOSFET as drain current can flow with zero gate potential. If the channel line is shown dotted or broken it is an "Enhancement"

(normally-OFF) type MOSFET as zero drain current flows with zero gate potential. The direction of the arrow indicates whether the conductive channel is a p-type or an n-type semiconductor device.

### **Basic MOSFET Structure and Symbol**

The construction of the Metal Oxide Semiconductor FET is very different to that of the Junction FET. Both the Depletion and Enhancement type MOSFETs use an electrical field produced by a gate voltage to alter the flow of charge carriers, electrons for n-channel or holes for P-channel, through the semi conductive drain-source channel. The gate electrode is placed on top of a very thin insulating layer and there are a pair of small n-type regions just under the drain and source electrodes. It is possible to bias the gate of a MOSFET in either polarity, positive (+ve) or negative (-ve).

This makes the MOSFET device especially valuable as electronic switches or to make logic gates because with no bias they are normally non-conducting and this high gate input resistance means that very little or no control current is needed as MOSFETs are voltage controlled devices. Both the p-channel and the n-channel MOSFETs are available in two basic forms, the Enhancement type and the Depletion type.

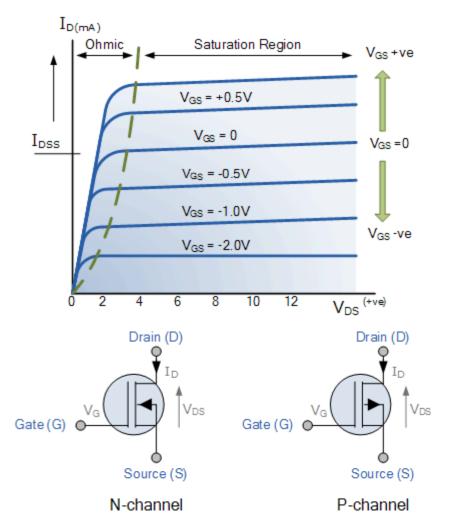

### **Depletion-mode MOSFET**

The Depletion-mode MOSFET, which is less common than the enhancement mode types is normally switched "ON" (conducting) without the application of a gate bias voltage. That is the channel conducts when  $V_{GS} = 0$  making it a "normally-closed" device. The circuit symbol shown above for a depletion MOS transistor uses a solid channel line to signify a normally closed conductive channel.

For the n-channel depletion MOS transistor, a negative gate-source voltage,  $-V_{GS}$  will deplete (hence its name) the conductive channel of its free electrons switching the transistor "OFF". Likewise for a pchannel depletion MOS transistor a positive gate-source voltage,  $+V_{GS}$  will deplete the channel of its free holes turning it "OFF". In other words, for an n-channel depletion mode MOSFET:  $+V_{GS}$  means more electrons and more current. While a  $-V_{GS}$  means less electrons and less current. The opposite is also true for the p-channel types. Then the depletion mode MOSFET is equivalent to a "normally-closed" switch.

### **Depletion-mode N-Channel MOSFET and circuit Symbols**

The depletion-mode MOSFET is constructed in a similar way to their JFET transistor counterparts were the drain-source channel is inherently conductive with the electrons and holes already present within the n-type or p-type channel. This doping of the channel produces a conducting path of low resistance between the Drain andSource with zero Gate bias.

### **Enhancement-mode MOSFET**

The more common Enhancement-mode MOSFET or e - MOSFET, is the reverse of the depletionmode type. Here the conducting channel is lightly doped or even undoped making it non-conductive. This results in the device being normally "OFF" (non-conducting) when the gate bias voltage, V<sub>GS</sub> is equal to zero. The circuit symbol shown above for an enhancement MOS transistor uses a broken channel line to signify a normally open non-conducting channel.

For the n-channel enhancement MOS transistor a drain current will only flow when a gate voltage ( $V_{GS}$ ) is applied to the gate terminal greater than the threshold voltage ( $V_{TH}$ ) level in which conductance takes place making it a transconductance device.

The application of a positive (+ve) gate voltage to a n-type eMOSFET attracts more electrons towards the oxide layer around the gate thereby increasing or enhancing the thickness of the channel allowing more current to flow. This is why this kind of transistor is called an enhancement mode device as the application of a gate voltage enhances the channel.Increasing this positive gate voltage will cause the channel resistance to decrease further causing an increase in the drain current, I<sub>D</sub> through the channel. In other words, for an n-channel enhancement mode MOSFET:  $+V_{GS}$  turns the transistor "ON", while a zero or  $-V_{GS}$  turns the transistor "OFF". Then, the enhancement-mode MOSFET is equivalent to a "normally-open" switch.

The reverse is true for the p-channel enhancement MOS transistor. When  $V_{GS} = 0$  the device is "OFF" and the channel is open. The application of a negative (-ve) gate voltage to the p-type e - MOSFET enhances the channels conductivity turning it "ON". Then for an p-channel enhancement mode MOSFET: +V<sub>GS</sub> turns the transistor "OFF", while -V<sub>GS</sub> turns the transistor "ON".

### **Out-put Characteristics**

Enhancement-mode MOSFETs make excellent electronics switches due to their low "ON" resistance and extremely high "OFF" resistance as well as their infinitely high input resistance due to their isolated gate. Enhancement-mode MOSFETs are used in integrated circuits to produce CMOS type Logic Gates and power switching circuits in the form of as PMOS (P-channel) and NMOS (N-channel) gates. CMOS actually stands for Complementary MOS meaning that the logic device has both PMOS and NMOS within its design.

### The MOSFET Amplifier

MOSFETs can be used to make single stage class "A" amplifier circuits with the enhancement mode n-channel MOSFET. The depletion mode MOSFET amplifiers are very similar to the JFET amplifiers, except that the MOSFET has a much higher input impedance.

This high input impedance is controlled by the gate biasing resistive network formed by R1 and R2. Also, the output signal for the enhancement mode common source MOSFET amplifier is inverted because when  $V_G$  is low the transistor is switched "OFF" and  $V_D$  (Vout) is high. When  $V_G$  is high the transistor is switched "ON" and  $V_D$  (Vout) is low.

Enhancement-mode N-Channel MOSFET Amplifier

The DC biasing of this common source (CS) MOSFET amplifier circuit is identical to the JFET amplifier. The MOSFET circuit is biased in class A mode by the voltage divider network formed by resistors R1 and R2. The AC input resistance is given as  $R_{IN} = R_G = 1M\Omega$ .

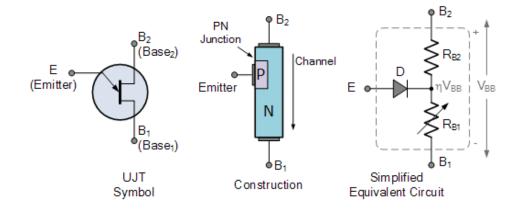

### **UNIJUNCTION TRANSISTOR OR UJT**

The Unijunction Transistor or UJT for short, is another solid state three terminal device that can be used in gate pulse, timing circuits and trigger generator applications to switch and control either thyristors and triacs for AC power control type applications.

Like diodes, unijunction transistors are constructed from separate P-type and N-type semiconductor materials forming a single (hence its name Uni-Junction) PN-junction within the main conducting N-type channel of the device.

Although the Unijunction Transistor has the name of a transistor, its switching characteristics are very different from those of a conventional bipolar or field effect transistor as it can not be used to amplify a signal but instead is used as a ON-OFF switching transistor. UJT's have unidirectional conductivity and negative impedance characteristics acting more like a variable voltage divider during breakdown.

Like N-channel FET's, the UJT consists of a single solid piece of N-type semiconductor material forming the main current carrying channel with its two outer connections marked as Base 2 ( $B_2$ ) and Base 1 ( $B_1$ ). The third connection, marked as the Emitter (E) is located along the channel. The emitter terminal is represented by an arrow pointing from the P-type emitter to the N-type base. The Emitter rectifying p-n junction of the unijunction transistor is formed by fusing the P-type material into the N-type silicon channel. The Emitter junction is positioned along the channel so that it is closer to terminal  $B_2$  than  $B_1$ . An arrow is

used in the UJT symbol which points towards the base indicating that the Emitter terminal is positive and the silicon bar is negative material.

### **Unijunction Transistor Symbol and Construction**

From the simplified equivalent circuit it is clear that the N-type channel consists of two resistors  $R_{B2}$  and  $R_{B1}$  in series with an equivalent diode, D representing the p-n junction connected to their center point. This Emitter p-n junction is fixed in position along the ohmic channel .Resistance  $R_{B1}$  is given between the Emitter, E and terminal  $B_1$ , while resistance  $R_{B2}$  is given between the Emitter, E and terminal  $B_1$ , while resistance  $R_{B2}$  is given between the Emitter, E and terminal  $B_2$ . As the physical position of the p-n junction is closer to terminal  $B_2$  than  $B_1$  the resistive value of  $R_{B2}$  will be less than  $R_{B1}$ .

The total resistance of the silicon bar will be dependent upon the semiconductors actual doping level as well as the physical dimensions of the N-type silicon channel but can be represented by  $R_{BB}$ .

These two series resistances produce a voltage divider network between the two base terminals of the unijunction transistor and since this channel stretches from  $B_2$  to  $B_1$ , when a voltage is applied across the device, the potential at any point along the channel will be in proportion to its position between terminals  $B_2$  and  $B_1$ . The level of the voltage gradient therefore depends upon the amount of supply voltage. When used in a circuit, terminal  $B_1$  is connected to ground and the Emitter serves as the input to the device. Suppose a voltage  $V_{BB}$  is applied across the UJT between  $B_2$  and  $B_1$  so that  $B_2$  is biased positive relative to  $B_1$ . With zero Emitter input applied, the voltage developed across  $R_{B1}$  (the lower resistance) of the resistive voltage divider can be calculated as:

### Unijunction Transistor R<sub>B1</sub> Voltage

$V_{RB1} = R_{B1}/R_{B1} + R_{B2} X V_{BB}$

For a unijunction transistor, the resistive ratio of  $R_{B1}$  to  $R_{BB}$  is called the intrinsic stand-off ratio and is given the Greek symbol:  $\eta$  (eta). Typical standard values of  $\eta$  range from 0.5 to 0.8 for most common UJT's.

If a small positive input voltage which is less than the voltage developed across resistance,  $R_{B1}$  ( $\eta V_{BB}$ ) is now applied to the Emitter input terminal, the diode p-n junction is reverse biased, thus offering a very high impedance and the device does not conduct. The UJT is switched "OFF" and zero current flows. However, when the Emitter input voltage is increased and becomes greater than  $V_{RB1}$  (or  $\eta V_{BB} + 0.7V$ , where 0.7V equals the p-n junction diode volt drop) the p-n junction becomes forward biased and the unijunction transistor begins to conduct. The result is that Emitter current,  $\eta I_E$  now flows from the Emitter into the Base region.

The effect of the additional Emitter current flowing into the Base reduces the resistive portion of the channel between the Emitter junction and the  $B_1$  terminal. This reduction in the value of  $R_{B_1}$  resistance to a very low value means that the Emitter junction becomes even more forward biased resulting in a larger current flow. The effect of this results in a negative resistance at the Emitter terminal.

If the input voltage applied between the Emitter and  $B_1$  terminal decreases to a value below breakdown, the resistive value of  $R_{B1}$  increases to a high value. Then the Unijunction Transistor can be thought of as a voltage breakdown device. So we can see that the resistance presented by  $R_{B1}$  is variable and is dependent on the value of Emitter current,  $I_E$ . Then forward biasing the Emitter junction with respect to  $B_1$  causes more current to flow which reduces the resistance between the Emitter, E and  $B_1$ . In other words, the flow of current into the UJT's Emitter causes the resistive value of  $R_{B1}$  to decrease and the voltage drop across it,  $V_{RB1}$  must also decrease, allowing more current to flow producing a negative resistance condition.

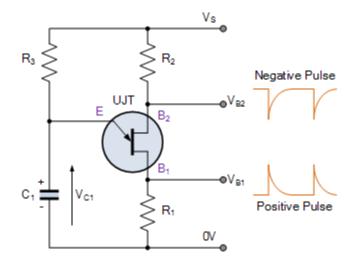

## **Unijunction Transistor Applications**

The most common application of a unijunction transistor is as a triggering device for scR and TRIAC, but other UJT applications include sawtoothed generators, simple oscillators, phase control, and timing circuits. The simplest of all UJT circuits is the Relaxation Oscillator producing non-sinusoidal waveforms.

In a basic and typical UJT relaxation oscillator circuit, the Emitter terminal of the unijunction transistor is connected to the junction of a series connected resistor and capacitor, RC circuit as shown below.

### **Unijunction Transistor Relaxation Oscillator**

When a voltage (Vs) is applied, the unijunction transistor is "OFF" and the capacitor C1 is fully discharged but begins to charge up exponentially through resistor R3. As the Emitter of the UJT is connected to the capacitor, when the charging voltage Vc across the capacitor becomes greater than the diode volt drop value, the p-n junction behaves as a normal diode and becomes forward biased triggering the UJT into conduction. The unijunction transistor is "ON". At this point the Emitter to B1 impedance collapses as the Emitter goes into a low impedance saturated state with the flow of Emitter current through R1 taking place.

As the ohmic value of resistor R1 is very low, the capacitor discharges rapidly through the UJT and a fast rising voltage pulse appears acrossR1. Also, because the capacitor discharges more quickly through the UJT than it does charging up through resistor R3, the discharging time is a lot less than the charging time as the capacitor discharges through the low resistance UJT.

When the voltage across the capacitor decreases below the holding point of the p-n junction ( $V_{OFF}$ ), the UJT turns "OFF" and no current flows into the Emitter junction so once again the capacitor charges up through resistor R3 and this charging and discharging process between  $V_{ON}$  and  $V_{OFF}$  is constantly repeated while there is a supply voltage, Vsapplied.

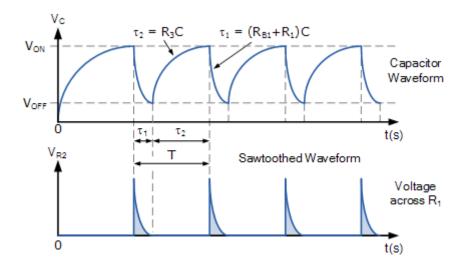

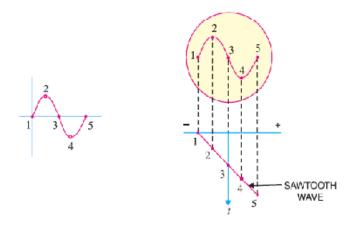

### UJT Oscillator Waveforms

Then we can see that the unijunction oscillator continually switches "ON" and "OFF" without any feedback. The frequency of operation of the oscillator is directly affected by the value of the charging resistanceR3, in series with the capacitor C1 and the value of  $\eta$ . The output pulse shape generated from the Base1 (B1) terminal is that of a sawtooth waveform and to regulate the time period, you only have to change the ohmic value of resistance, R3 since it sets the RC time constant for charging the capacitor.

The time period, T of the saw tooth waveform will be given as the charging time plus the discharging time of the capacitor. As the discharge time,  $\tau_1$  is generally very short in comparison to the larger RC charging time,  $\tau_2$  the time period of oscillation is more or less equivalent to T  $\cong \tau_2$ . The frequency of oscillation is therefore given by f = 1/T.

For example, if the value of R3 was too large, (Megohms) the capacitor may not charge up sufficiently to trigger the Unijunction's Emitter into conduction but must also be large enough to ensure that the UJT switches "OFF" once the capacitor has discharged to below the lower trigger voltage.

### CMOS

CMOS (complementary metal-oxide-semiconductor) technology is used predominantly to create digital circuitry. The fundamental building blocks of CMOS circuits are P-type and N-type MOSFET transistors. A P-type MOSFET can be modeled as a switch that is closed when the input voltage is low (0 V) and open when the input voltage is high (5 V). A N-type MOSFET can be modeled as a switch that is closed when the input voltage is high (5 V) and open when the input voltage is low (0 V). The basic idea for

CMOS technology is to combine P-type and N-type MOSFETs such that there is never a conducting path from the supply voltage (5 V) to ground. As a consequence, CMOS circuits consume very little energy.

CMOS technology employs two types of transistor: n-channel and p-channel. The two differ in the characteristics of the semiconductor materials used in their implementation and in the mechanism governing the conduction of a current through them.

The transistor has three terminals: the gate (G), the source (S), and the drain (D). The voltage applied between G and S determines whether a path for current to flow exists between D and S. If a path exists, we say that the transistor is ON, and if a path does not exist, we say that the transistor is OFF. The n-channel transistor is ON if the applied gate-to-source voltage is H and OFF if the applied voltage is L. Here we will make the usual assumption that a 1 represents the H voltage range and a 0 represents the L voltage range. The notion of whether a path for current to flow exists is easily modeled by a switch. The switch consists of two fixed terminals corresponding to the S and D terminals of the transistor. In addition, there is a movable contact that, depending on its position, determines whether the switch is open or closed. The position of the contact is controlled by the voltage applied to the gate terminal G. Since we are looking at logic behavior, this control voltage is represented on the symbol by the input variable X equal to 0 and closed (a path exists) for the input variable X equal to 1. Such a contact is traditionally referred to as being normally open, that is, open without a positive voltage applied to activate or close it.

The symbol for a p-channel transistor is shown in Figure below. The positions of the source S and drain D are seen to be interchanged relative to their positions in the n-channel transistor. The voltage applied between the gate G and the source S determines whether a path exists between the drain and source. The negation indicator or bubble appears as a part of the symbol. This is because, in contrast to the behavior of an n-channel transistor, a path exists between S and D in the p-channel transistor for input variable X equal to 0 (at value L) and does not exist for input variable X equal to 1 (at value H). This behavior is represented by the model which has a normally closed contact through which a path exists for X equal to 0. No path exists through the contact for X equal to 1.

The popular CMOS family include,

4000A, 4000B, 4000UB, 54/74C, 54/74HC, 54/74HCT, 54/74AC 54/74ACT

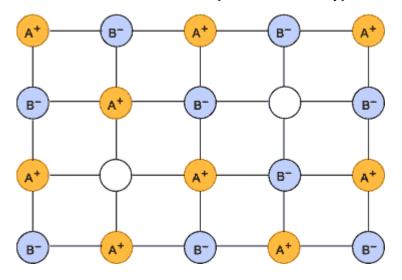

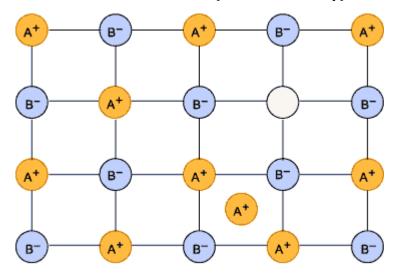

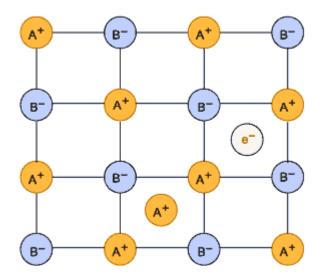

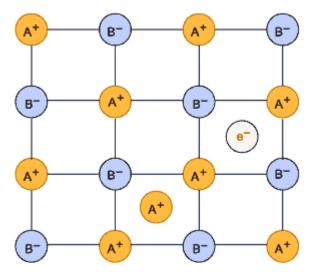

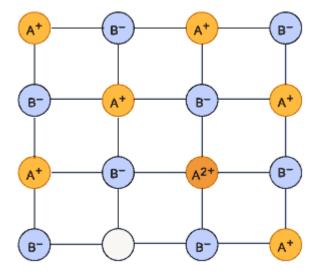

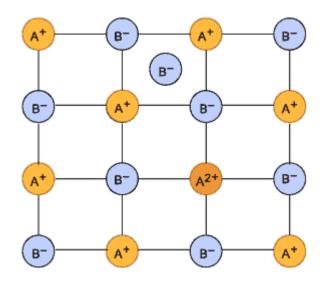

### CHARGE COUPLED DEVICE-CCD

CCD was developed in the year 1969 by Willard Boyle and George E. Smith at AT & T Bell Labs. It is a shift register device which can be used for the movement of electrical charge within the device. This movement can be from one area of the device to another and the digital value of the moved charge can be easily found out. When the signals are moved, one at a time from one place to another within the device, the value of the charge can be easily manipulated. There are capacitive bins in the device that allow the movement of charge.

### There are mainly two regions of a CCD

### 1. Photoactive Region

The photoactive region mainly consists of a capacitor array. These arrays can be one-dimensional or twodimensional depending on the type of device that uses the CCD. If a line scan camera is used, it introduces a one-dimensional capacitor array. It is called 1D because it captures the image in 1D form, that is, a single slice of the image. 2D is used mostly in video applications. This device captures the image in 2D form. The photoactive region is made out of an epitaxial layer of silicon. It is made by doping a boron ion on a substrate such as p++. Sometimes CCD's are also implanted with a phosphorus ion so as to give them an ndoping. This is often carried out in devices consisting of n-channels This is done in some areas of the silicon ion causing the movement of photo generated packets across them.

As soon as the silicon layer and substrates are made, a dielectric in the form of a gas oxide (mostly capacitor) is made to grow on top of them. Thus the separately lying gates will lie in a perpendicular angle to the channels. This is because the poly-silicon gates are undergoing chemical vapour deposition and then photolithography. Then the channel stop region and the charge carrying channel is made, and that too parallel to each other.

### **2.Transmission Region**

After the image is projected onto the capacitor array, the control circuit comes into action. This circuit makes the capacitors send the appropriate signal to a shift register. The shift register converts each signal into a voltage sequence. This is later sampled, digitized and then stored in the memory.

**Applications of CCD**

### 1.Astronomy

2. Colour Cameras

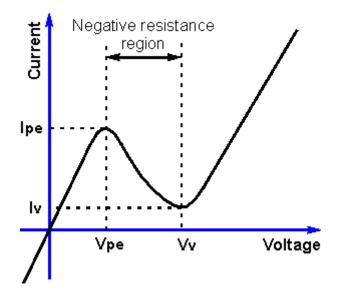

### TUNNEL DIODE

. A Tunnel diode is a heavily doped <u>p-n junction diode</u> in which the electric current decreases as the <u>voltage</u> increases. In tunnel diode, electric current is caused by "Tunneling". The tunnel diode is used as a very fast switching device in computers. It is also used in high-frequency oscillators and amplifiers. Tunnel diode was invented in 1958 by Leo Esaki. It is also known as Esaki diode which is named after Leo Esaki for his work on the tunneling effect.

In tunnel diode, the <u>p-type semiconductor</u> act as an anode and the <u>n-type semiconductor</u> act as a cathode.

Symbol

#### **Tunnelling mechanism & theory**

Tunnelling is an effect that is caused by quantum mechanical effects when electrons pass through a potential barrier. It can be visualised in very basic terms by them "tunnelling" through the energy barrier. The tunnelling only occurs under certain conditions. It occurs within tunnel diodes because of the very high doping levels employed.

At reverse bias, the electrons tunnel from the valence band in the p-type material to the conduction band in the n-type material, and the level of the current increase monotonically.For the forward bias situation there are a number of different areas. For voltages up to Vpe, electrons from the conduction band find increasing availability of empty states in the valence band and the level of current increases up to a point where the current equals Ipe.Once this point is reach, it is found that number of empty states available for electrons with the level of energy they are given by the increased voltage level starts to fall. This means that the current level falls in line with this. The overall current level falls away relatively swiftly, dropping to near zero.

As the current from the tunnelling effect falls, so the diffusion current, which is the same action as occurs in a normal PN junction diode starts to increase and steadily becomes the dominant mechanism.

Tunnel diode characteristics

### **Tunnel diode IV characteristic**

The diagram towards the top of the page shows the tunnel diode IV characteristic. This has a form of 'N' shaped curve. With an area of negative resistance between the peak voltage, Vpe and the valley voltage Vv.

The characteristic curve for a tunnel diode shows an area of negative resistance. When forward biased the current in the diode rises at first, but later it can be seen to fall with increasing voltage, before finally rising again. In this diode, current flows in the reverse direction - the reverse breakdown voltage is actually zero and the diode conducts in the reverse direction.

The reason for this is that there are a number of different components to forming the overall curve.

- Normal diode current: This is the 'normal' current that would flow through a PN junction diode.

- Tunnelling current: This is the current that arises as a result of the tunnelling effect.

- Excess current: This is a third element of current that contributes to the overall current within the diode. It results from what may be termed excess current that results from tunnelling though bulk states in the energy gap, and means that the valley current does not fall to zero.

The values for these voltages depend upon the diode material and also upon its individual characteristics. One of the useful figures of merit for a tunnel diode characteristic is the peak to valley current ratio, Ipe / Iv. From the values in the table it can be seen that silicon has a very low value and as a result, this means that it is not normally one of the best options for a tunnel diode.

### Advantages of tunnel diodes

- Long life

- High-speed operation

- Low noise

- Low power consumption

### **POSSIBLE QUESTIONS**

### PART-B (2 Marks)

- **1.** What is the difference between BJT and FET?

- 2. What is called Tunnel Diode?

- 3. What is called as tunneling effect?

- 4. What do you mean by charge coupled device?

- 5. What are the different mode of operations of MOSFET?

- 6. List out the advantages of CMOS.

- 7. List out the advantages of Tunnel diode.

- 8. Define transconductance.

- 9. What do ypu meant by negative resistance region?

- 10. What are the frequency limitations of MOSFET?

### PART-C (6 Marks)

- 1.Explain working principle and characteristics of UJT.

- 2.Explain working principle and characteristics of JFET.

- 3.Explain working principle and characteristics of tunnel diode.

- 4.Explain working principle and characteristics of D MOSFET

- 5.Explain working principle and characteristics of E MOSFET.

- 6.Explain working principle and characteristics of CMOS.

- 7.Write short note on i) CCD ii) tunneling effect.

- 8.Explain briefly about charge coupled device.

- 9. Explain working principle of relaxation oscillator.

- 10.Explain working principle of MOSFET amplifier.

KARPAGAM ACADEMY OF HIGHER EDUCATION,COIMBATO RE-21 DEPARTMENT OF PHYSICS II B.Sc., PHYSICS (2018-2021) PHYSICS OF ELECTRONIC DEVICES AND CIRCUTS (18PHU302)

UNIT - I

## Option-1 Option-2 Option-3 Option-4 Key

|                                        | Option 1              | Option 2              | Option 5              | Option 1              | ncy                   |

|----------------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| Junction Field Effect                  |                       |                       |                       |                       |                       |

| Transistors (JFET) contain             |                       |                       |                       |                       |                       |

| how many diodes?                       | 4                     | 3                     | 2                     | 1                     | 2                     |

| When not in use, MOSFET                |                       | noncondu              |                       |                       |                       |

| pins are kept at the same              | shipping              | ctive                 | conductiv             | a wrist               | conductiv             |

| potential through the use of:          | foil                  | foam                  | e foam                | strap                 | e foam                |

| D-MOSFETs are sometimes                |                       |                       |                       |                       |                       |

| used in series to construct a          | low                   |                       | high                  |                       | high                  |

| cascode high-frequency                 | output                | capacitiv             | input                 |                       | input                 |

| amplifier to overcome the              | impedanc              | e                     | impedanc              | inductive             | impedanc              |

| loss of:                               | e                     | reactance             | e                     | reactance             | e                     |

| A "U" shaped, opposite-                |                       |                       |                       |                       |                       |

| polarity material built near a         |                       |                       |                       |                       |                       |

| JFET-channel center is                 |                       |                       |                       |                       |                       |

| called the:                            | gate                  | block                 | drain                 | heat sink             | gate                  |

|                                        |                       |                       |                       |                       |                       |

|                                        | As                    | As                    | As                    | As                    | As                    |

| In the constant-current                | $V_{GS}$ decre        | $V_{\text{GS}}$ incre | $V_{\text{GS}}$ decre | $V_{\text{GS}}$ incre | $V_{GS}$ decre        |

| region, how will the                   | ases                  | ases                  | ases                  | ases                  | ases                  |

| I <sub>DS</sub> change in an n-channel | I <sub>D</sub> decrea | $I_{\rm D}$ increas   | $I_D$ remain          | $I_D$ remain          | I <sub>D</sub> decrea |

| JFET?                                  | ses                   | es.                   | s constant            | s constan             | ses                   |

| A MOSFET has how many                  |                       |                       |                       |                       |                       |

| terminals?                             | 2 or 3                | 5                     | 6                     | 3 or 4                | 3 or 4                |

|                                        |                       |                       |                       |                       |                       |

| I <sub>DSS</sub> can be defined as:<br>What is the input impedance                                                               | the<br>minimum<br>possible<br>drain<br>current | maximu<br>m<br>possible<br>current<br>with<br>V <sub>GS</sub> held<br>at -4 V | maximu<br>m<br>possible<br>current<br>with<br>V <sub>GS</sub> held<br>at 0 V | the<br>maximu<br>m drain<br>current<br>with the<br>source<br>shorted | maximu<br>m<br>possible<br>current<br>with<br>$V_{GS}$ held<br>at 0 V |

|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------|

| of a common-gate<br>configured JFET?<br>JFET terminal "legs" are<br>connections to the drain, the                                | very low                                       | high                                                                          | low                                                                          | very high                                                            | very low                                                              |

| gate, and the:                                                                                                                   | channel<br>widening                            | source                                                                        | substrate                                                                    | cathode<br>voltage-                                                  | source                                                                |

| A very simple bias for a D-                                                                                                      | the                                            | gate                                                                          | zero                                                                         | divider                                                              | zero                                                                  |

| MOSFET is called:<br>With the E-MOSFET, when<br>gate input voltage is zero,                                                      | channel<br>at                                  | biasing                                                                       | biasing                                                                      | biasing<br>widening<br>the                                           | biasing                                                               |

| drain current is:                                                                                                                | saturation                                     | zero                                                                          | I <sub>DSS</sub>                                                             | channel                                                              | zero                                                                  |

| When an input signal<br>reduces the channel size, the<br>process is called:<br>Which JFET configuration<br>would connect a high- | enhance<br>ment                                | substrate<br>connectin<br>g                                                   | gate<br>charge                                                               | depletion                                                            | depletion                                                             |

| resistance signal source to a low-resistance load?                                                                               | source<br>follower<br>from                     | common-<br>source<br>from                                                     | common-<br>drain<br>from                                                     | common-<br>gate<br>from                                              | source<br>follower<br>from                                            |

| How will electrons flow                                                                                                          |                                                | source to                                                                     |                                                                              | drain to                                                             | drain to                                                              |

| through a p-channel JFET?                                                                                                        | drain                                          | gate<br>an                                                                    | gate                                                                         | source                                                               | source                                                                |

| When $V_{GS} = 0$ V, a JFET is:<br>When applied input voltage                                                                    | saturated                                      | analog<br>device                                                              | an open<br>switch                                                            | cut off                                                              | saturated                                                             |

| varies the resistance of a channel, the result is called:                                                                        | saturizati<br>on<br>for high                   | polarizati<br>on                                                              | cutoff                                                                       | field<br>effect<br>for high                                          | field<br>effect                                                       |

| When is a vertical channel E-<br>MOSFET used?                                                                                    | frequenci<br>es<br>Two pn                      | for high<br>voltages<br>one on                                                | for high<br>currents<br>three pn                                             | resistance<br>s<br>foue pn                                           | for high<br>currents<br>one on                                        |

| A UJT has<br>In a UJT, the p-type emitter                                                                                        | junctions                                      |                                                                               | junction<br>Moderate                                                         | junction                                                             | junction                                                              |

| is doped                                                                                                                         | Lightly                                        | Heavily                                                                       | ly                                                                           | heavily                                                              | Heavily                                                               |

| When a UJT is turned ON,<br>the resistance between<br>emitter terminal and lower<br>base terminal    | remains<br>the same             | increased              | decreased           | zero                        | increased                   |

|------------------------------------------------------------------------------------------------------|---------------------------------|------------------------|---------------------|-----------------------------|-----------------------------|

| To turn on UJT, the forward<br>bias on the emitter diode<br>should be the<br>peak point voltage      | Less than                       | more<br>than           | zero                | grater<br>than or<br>equal  | more<br>than                |

| UJT is sometimes called<br>diode<br>When the temperature<br>increases, the inter-base                | Low<br>resistance               | high<br>resistance     | Single-<br>base     | double-<br>base             | double-<br>base             |

| resistance (RBB) of a UJT<br><br>When the temperature                                                | remains<br>the same             | increased              | decreased           | zero                        | increased                   |

| increases, the intrinsic stand<br>off ratio<br>Between the peak point and<br>the valley point of UJT | remains<br>the same             | increased              | decreased           | zero                        | remains<br>the same         |

| emitter characteristics we<br>have region<br>The device that exhibits                                | Saturatio<br>n                  | Negative resistance    | Cut-off             | positive<br>resistance      | Negative resistance         |

| negative resistance region is                                                                        | FET                             | UJT                    | Triac               | Diac                        | UJT                         |

| The UJT may be used as                                                                               | amplifier                       | sawtooth<br>generator  | rectifier           | switch                      | sawtooth<br>generator       |

| Which of the following is<br>not a characteristic of UJT?<br>When the JFET is no longer              | Intrinsic<br>stand off<br>ratio | Negative<br>resistance | -                   | Bilateral<br>conductio<br>n | Bilateral<br>conductio<br>n |

| able to control the current,<br>this point is called the<br>With a JFET, a ratio of                  | breakdow<br>n region            | depletion<br>region    | saturation<br>point | pinch-off<br>region         | breakdow<br>n region        |

| output current change against<br>an input voltage change is<br>called<br>Which type of JFET bias     | gain                            | transcond<br>uctance   | siemens             | resistivity                 | transcond<br>uctance        |

| requires a negative supply voltage?                                                                  | feedback                        | source                 | gate                | voltage<br>divider          | gate                        |

| The type of bias most often<br>used with E-MOSFET<br>circuits is:          | constant<br>current                      | drain-<br>feedback                      | voltage-<br>divider                             | zero<br>biasing                          | drain-<br>feedback                              |

|----------------------------------------------------------------------------|------------------------------------------|-----------------------------------------|-------------------------------------------------|------------------------------------------|-------------------------------------------------|

| The output of the comparator<br>for CMOS IC's is<br>Which component is     | 0.5V                                     | 1.2V                                    | 2.5V                                            | 4.5V                                     | 2.5V                                            |

| considered to be an "OFF" device?                                          |                                          | IFFT                                    | D-<br>MOSEET                                    | E-<br>MOSEET                             | E-<br>MOSEET                                    |

| In MOS transistors, is                                                     | transistor                               | silicon-                                | polysilico                                      | MOSFET                                   | polysilico                                      |

| used for their gate                                                        | metal                                    | di-oxide                                | n<br>lower                                      | gallium                                  | n                                               |

|                                                                            | insulating                               | conductin                               | metal                                           | p type                                   | conductin                                       |

| The gate region consists of                                                | layer                                    | g layer                                 | layer                                           | layer                                    | g layer                                         |

| Source in MOS transistors is<br>doped with material<br>In N channel MOSFET | n-type                                   | p-type                                  | c-type                                          | e-type                                   | n-type                                          |

| which is the more negative of the elements?                                | source                                   | gate                                    | drain                                           | source and drain                         | source                                          |

| If the gate is given                                                       | 500100                                   | Bare                                    |                                                 |                                          |                                                 |

| sufficiently large charge,                                                 | drain                                    | channel                                 | switch                                          | bulk                                     | channel                                         |

| electrons will be attracted to                                             | region                                   | region                                  | region                                          | region                                   | region                                          |

|                                                                            | p-type<br>substrate<br>of high<br>doping | n-type<br>substrate<br>of low<br>doping | p-type<br>substrate<br>of<br>moderate<br>doping | n-type<br>substrate<br>of high<br>doping | p-type<br>substrate<br>of<br>moderate<br>doping |

| nMOS devices are formed in                                                 | level                                    | level                                   | level                                           | level                                    | level                                           |

| Source and drain in nMOS                                                   | a single                                 | two                                     | three                                           | four                                     | two                                             |

| device are isolated b                                                      | diode                                    | diodes                                  | diodes                                          | diodes                                   | diodes                                          |

| In enhancement mode,<br>device is in                                       | conductin                                | non                                     | partially                                       | insulatin                                | non<br>conductin                                |

| condition                                                                  | g                                        | g                                       | g                                               | g                                        | g                                               |

|                                                                            | U                                        | non                                     | semi                                            | pseudo                                   | 0                                               |

| MOS transistor structure is                                                | cal                                      | symmetri<br>cal                         | symmetri<br>cal                                 | symmetri<br>cal                          | cal                                             |

|                                                                            | donor                                    | acceptor                                | no                                              | ·                                        | acceptor                                        |

| nMOS is                                                                    | doped<br>donor                           | doped<br>acceptor                       | doping<br>no                                    | insulating                               | doped<br>donor                                  |

| pMOS is                                                                    | doped                                    | doped                                   | doping                                          | insulating                               |                                                 |

| Inversion layer in                                                         | 1                                        | 1                                       | both in                                         | B                                        | 1                                               |

| enhancement mode consists                                                  | positive                                 | negative                                | equal                                           | neutral                                  | negative                                        |

| of excess of                                                               | carriers                                 | carriers                                | quantity                                        | carriers                                 | carriers                                        |

|                                                                            |                                          |                                         |                                                 |                                          |                                                 |

| As source drain voltage increases, channel depth                                                                                                         | increases                                                   | decreases                                                       | ically<br>increases                                                              | Source                                                                   | decreases                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------|

| If the n-MOS and p-MOS of<br>the CMOS inverters are<br>interchanged the output is<br>measured at:<br>What will be the effect on<br>output voltage if the | Source<br>of the<br>both<br>transistor                      | Drains<br>of the<br>both<br>transistor                          | Drain of<br>n-MOS<br>and<br>source of<br>p-MOS                                   | of n-<br>MOS<br>and<br>drain of<br>p-MOS                                 | Source<br>of the<br>both<br>transistor         |

| positions of n-MOS and p-<br>MOS in CMOS inverter<br>circuit are exchanged?                                                                              | Output is same                                              | Output is reversed                                              | -                                                                                | Output is<br>always<br>low                                               | Output is reversed                             |

| The average power<br>dissipated in resistive load n-<br>MOS inverter is:                                                                                 | 0                                                           | VDD<br>(VDD-<br>VOL)/R                                          | VDD<br>(VDD-<br>VOL)/2R                                                          | VDD<br>(VDD-<br>VIH)/2R                                                  | VDD<br>(VDD-<br>VOL)/2R                        |

|                                                                                                                                                          |                                                             |                                                                 |                                                                                  |                                                                          |                                                |

| In the CMOS inverter the output voltage is measured across:                                                                                              | Drain of<br>n-MOS<br>transistor<br>and<br>groun             | Source<br>of p-<br>MOS<br>transistor<br>and<br>ground<br>low    | and<br>source of<br>p-MOS                                                        | Gate of<br>p-MOS<br>transistor<br>and Gate<br>of n-<br>MOS<br>transistor | n-MOS<br>transistor<br>and                     |

| output voltage is measured                                                                                                                               | n-MOS<br>transistor<br>and                                  | of p-<br>MOS<br>transistor<br>and<br>ground<br>low<br>frequency | of n-<br>MOS<br>transistor<br>and<br>source of<br>p-MOS<br>transistor            | p-MOS<br>transistor<br>and Gate<br>of n-<br>MOS                          | n-MOS<br>transistor<br>and                     |

| output voltage is measured<br>across:<br>Tuneel diode operates in                                                                                        | n-MOS<br>transistor<br>and<br>groun<br>Microwa<br>ve region | of p-<br>MOS<br>transistor<br>and<br>ground<br>low<br>frequency | of n-<br>MOS<br>transistor<br>and<br>source of<br>p-MOS<br>transistor<br>visible | p-MOS<br>transistor<br>and Gate<br>of n-<br>MOS<br>transistor<br>radio   | n-MOS<br>transistor<br>and<br>groun<br>Microwa |

|                             | N-MOS      | P-MOS                     |            |            |            |

|-----------------------------|------------|---------------------------|------------|------------|------------|

| When the input of the       | is cutoff, | is cutoff,                | Both the   | Both the   | Both the   |

| CMOS inverter is equal to   | p-MOS      | n-MOS                     | transistor | transistor | transistor |

| Inverter Threshold Voltage  | is in      | is in                     | s are in   | s are in   | s are in   |

| Vth, the transistors are    | Saturatio  | Saturatio                 | linear     | saturation | saturation |

| operating in:               | n          | n                         | region     | region     | region     |

| The switching threshold     | <i></i>    |                           |            |            |            |

| voltage VTH for an ideal    | (VDD-      |                           |            |            |            |

| inverter is equal to        | VOL)/2     | VDD                       | (VDD)/2    | 0          | (VDD)/2    |

|                             | two        | three                     | one        | four       | one        |

| In dynamic CMOS logic       | phase      | phase                     | phase      | phase      | phase      |

| is used                     | clock      | clock                     | clock      | clock      | clock      |

| In clocked CMOS logic,      | on         |                           | both       | half of    | both       |

| output in evaluated in      | period     | off period                |            | on period  |            |

|                             | penica     | on p <b>o</b> no <b>a</b> | faster     | onpenea    | Periods    |

|                             |            |                           | first and  | slower     |            |

|                             |            |                           | then       | first and  |            |

| In clocked CMOS logic, rise |            |                           | slows      | then       |            |

| time and fall time are      | faster     | slower                    | down       | speeds up  | slower     |

|                             | two        | three                     | one        | four       | one        |

| In CMOS domino logic        | phase      | phase                     | phase      | phase      | phase      |

| is used                     | clock      | clock                     | clock      | clock      | clock      |

|                             |            |                           | inverting  |            |            |

|                             | • ,•       | non                       | and non    | very       | non        |

| In CMOS domino logic        | U          | inverting                 | C          | complex    | inverting  |

| is possible                 | structure  | structure                 | structure  | design     | structure  |

## KARPAGAM ACADEMY OF HIGHER EDUCATION

AGAM COURSE CODE: 18PHU302 UNIT: II (Power Supply) BATCH-2018-2021

## <u>UNIT-II</u>

### SYLLABUS

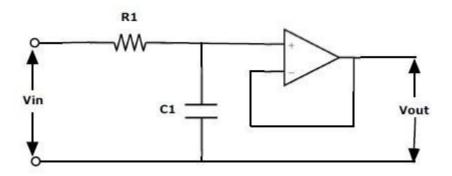

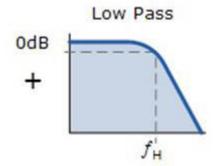

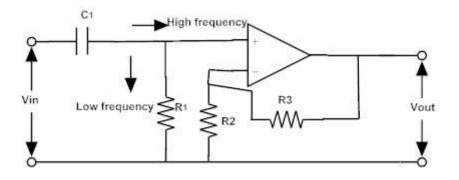

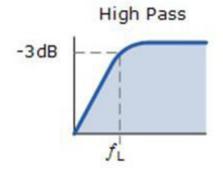

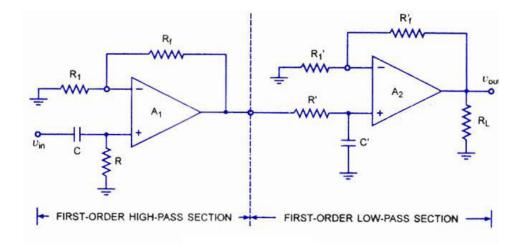

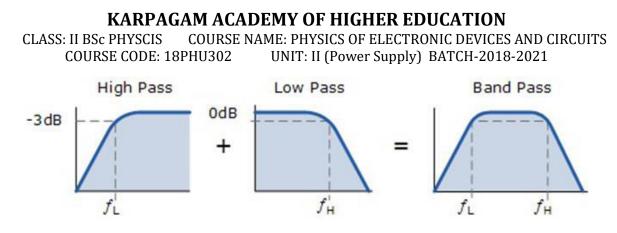

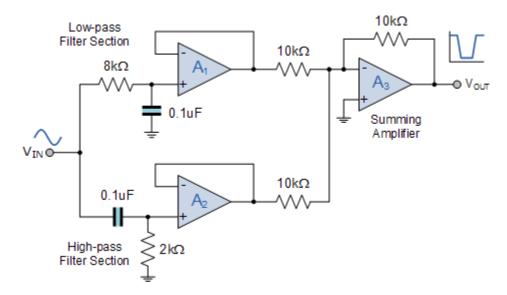

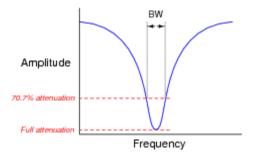

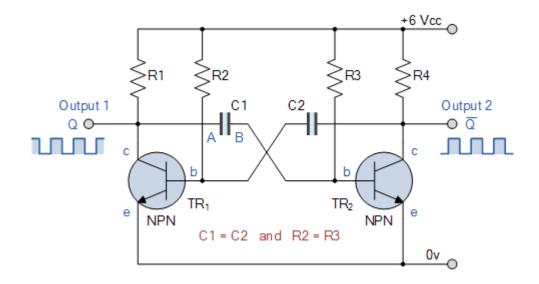

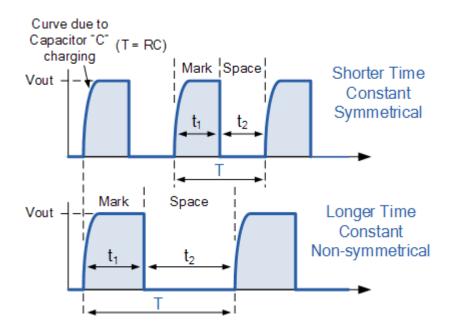

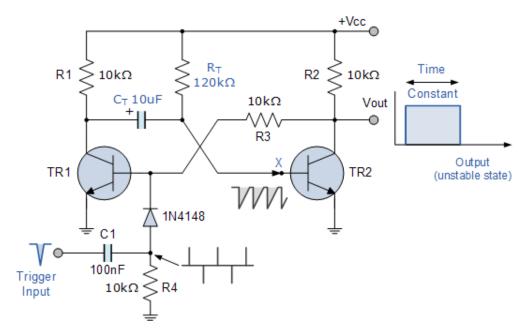

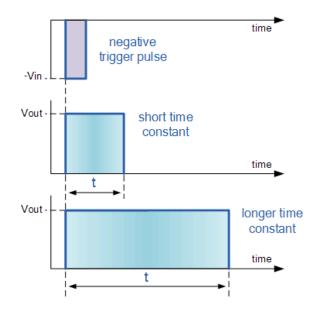

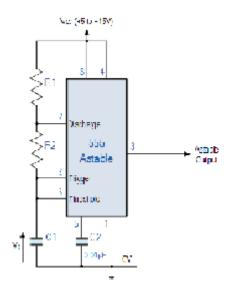

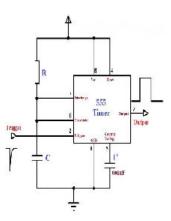

Power supply and Filters: Block Diagram of a Power Supply, Qualitative idea of C and L Filters. IC Regulators, Line and load regulation, Short circuit protection. Active and Passive Filters, Low Pass, High Pass, Band Pass and band Reject Filters. Multivibrators: Astable and Monostable Multivibrators using transistors.

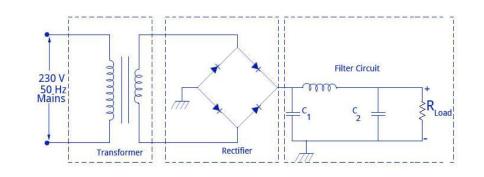

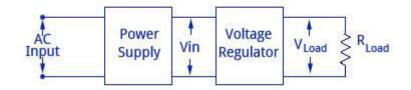

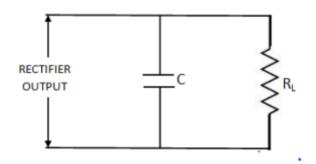

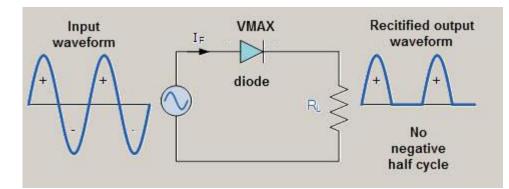

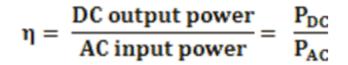

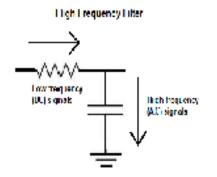

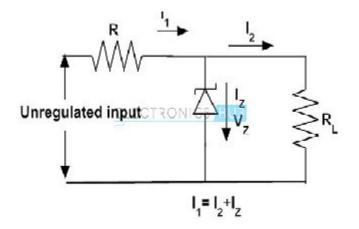

### **POWER SUPPLY**