SEMESTER III 4H- - 4C

| 19PHP304        | DIGITAL ELECTRONICS AND MICROPROCESSOR |                     |           |    |        |  |  |  |  |

|-----------------|----------------------------------------|---------------------|-----------|----|--------|--|--|--|--|

| Instruction Hou | rs / week: L: 4 T: 0 P: 0              | Marks: Internal: 40 | External: | 60 | Total: |  |  |  |  |

Instruction Hours / week: L: 4 T: 0 P: 0 100

End Semester Exam: 3 Hours

### **Course Objectives**

Digital electronics is very important in present day life due to its applications in almost all fields of life. Any signals stored in memory are first digitized. So it is important to have knowledge about digital electronics. This paper is intended to give an insight into the theory and applications of digital electronics, design of circuits with digital devices, details of microprocessor and its applications.

### Course Outcomes (Cos)

### At the end of the course, Students can

- 1. Acquire the basic knowledge of digital logic levels and application of digital electronics circuits.

- 2. Perform the analysis and design of various digital electronic circuits.

- 3. Acquired knowledge about Microprocessors and its need.

- 4. Ability to identify basic architecture of different Microprocessors.

- 5. Foster ability to write the programming using 8085 microprocessor.

- 6. Foster ability to understand the internal architecture and interfacing of different peripheral devices with 8085 Microprocessor.

### UNIT -I

**Flip Flops :** SR, JK, JK Master Slave, T Flip flop & D Flip Flop (Symbol and Truth table)Registers (Types, shift operations) - Counters (Types, Designing of MOD 5 synchronous Counter, Construction and truth table - verification of MOD 16 Asynchronous UP, Down counter) - Multiplexer And demultiplexer (16:1 and 1:16 description and truth table verification) - Decoders and encoders (Definitions, Seven segment decoder, decimal to BCD encoder)

### **UNIT-II**

**Special Function ICs:** Timer IC 555 (Block diagram, pin description), Application as Astable, monostable, bistable multivibrator - VCO IC 566 (Block diagram and pin description) - PLL IC 565 (Block diagram and pin description) - Fixed voltage Regulator ICs 7800 and 7900 series - Voltage Regulator IC 723 (description, designing for low and high voltage)

# UNIT-III

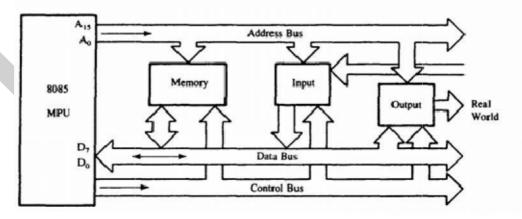

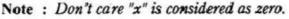

**Microprocessor:** Microprocessor Architecture, Pin out configuration of 8085-bus organization and timings –address bus, data bus, multiplexing address/data bus and control and status signal, Interrupts: maskable and non-maskable interrupt(concept),8085 interrupt.

# UNIT -IV

**Programming Model of 8085 :** Instruction set-Data transfer ,arithmetic, logical and branch instruction-Addressing modes -16 bit data transfer and memory related instructions-stack and subroutine instructions.

Simple Program: 8 bit addition-subtraction-multiplication- finding largest and smallest number, ascending and descending order, 16 bit addition,

# UNIT- V

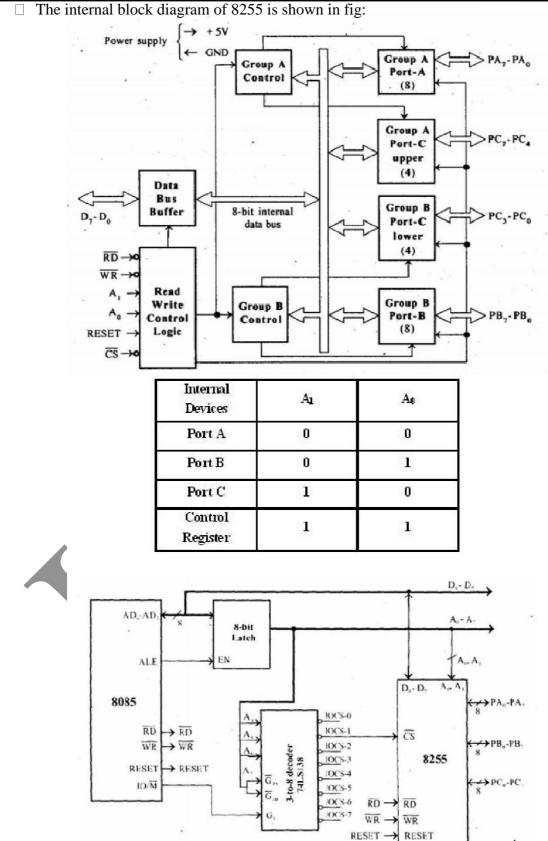

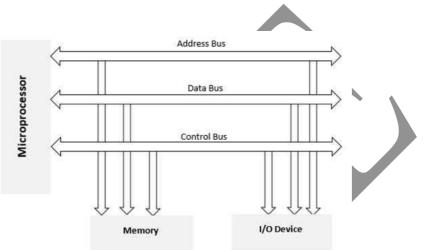

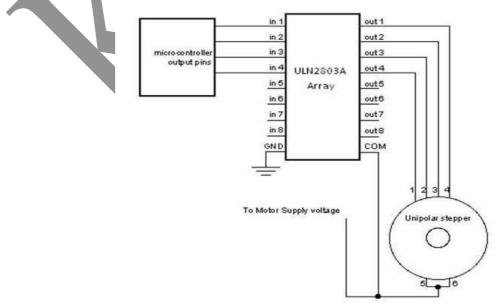

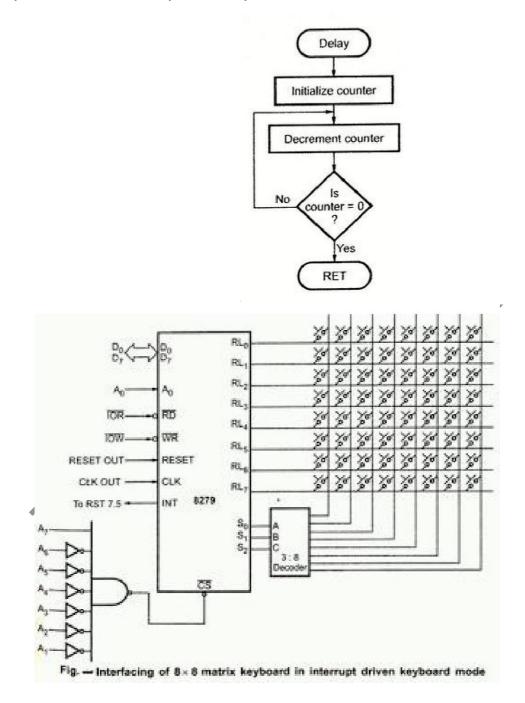

**Interfacing Peripherals and Applications**: Interfacing concepts-peripheral I/O instructions-Interfacing programs- Data Converters, LED interfacing, stepper motor interfacing, Hex Keyboard Interfacing.

# SUGGESTED READINGS

- 1. Floyd, 2003, Digital Fundamentals, 8th Edition, Pearson education, New Delhi.

- 2. Ramesh Gaonkar 6<sup>th</sup> edition 2013 Microprocessor Architecture, Programming and Applications with 8085 ,PENRAM International P Ltd

- Malvino and Leach, 2006, Digital Principles and Applications, 3rd Edition, Tata McGrawHill, New Delhi.

- Aditya P. Mathur, 24<sup>th</sup> reprint 2006, Introduction to Microprocessor, 3rd Edition, Tata McGrawHill, New Delhi.

- Morris Mano. M, 1<sup>st</sup> 2002, Digital Logic and Computer Design, Prentice Hall, New Delhi.

Lesson Plan Batch

Enable | Enlighten | Enrich (Deemed to be University) (Under Section 3 of UGC Act 1956) KARPAGAM ACADEMY OF HIGHER EDUCATION (Deemed to be University Established Under Section 3 of UGC Act 1956) Coimbatore – 641 021.

# LECTURE PLAN DEPARTMENT OF PHYSICS

# STAFF NAME: Mr. J.THIRUPATHY SUBJECT NAME: PHYSICS SEMESTER: III

# SUB.CODE:19PHP304 CLASS: II M.Sc (PHY)

| Serial<br>No. | Duration |                                                                                           |                            |  |  |  |  |

|---------------|----------|-------------------------------------------------------------------------------------------|----------------------------|--|--|--|--|

|               |          |                                                                                           |                            |  |  |  |  |

| 1             | 1        | SR flip flop                                                                              | T1-294 -298                |  |  |  |  |

| 2             | 1        | JK, JK Master Slave,                                                                      | T1-299-306                 |  |  |  |  |

| 3             | 1        | T Flip flop & D Flip Flop (Symbol and Truth table)                                        | T1-320-323                 |  |  |  |  |

| 4             | 1        | Registers (Types, shift operations)                                                       | T1-412-430                 |  |  |  |  |

| 5             | 1        | R1-310 -316                                                                               |                            |  |  |  |  |

| 6             | 1        | T1- 350-358,<br>368-370                                                                   |                            |  |  |  |  |

| 7             | 1        | Continuation                                                                              | R1-340-352                 |  |  |  |  |

| 8             | 1        | Multiplexer And demultiplexer (16:1 and 1:16<br>description and truth table verification) | T1- 247-260                |  |  |  |  |

| 9             | 1        | 1 Decoders and encoders (Definitions, Seven segment decoder, decimal to BCD encoder)      |                            |  |  |  |  |

| 10            | 1        | Revision                                                                                  |                            |  |  |  |  |

|               | То       | tal No. of Hours Planned For Unit I = 10                                                  |                            |  |  |  |  |

|               |          | UNIT-II                                                                                   |                            |  |  |  |  |

| 1             | 1        | Timer IC 555 (Block diagram, pin description)                                             | T1-427-428                 |  |  |  |  |

| 2             | 1        | Application as Astable, monostable                                                        | T1- 428-431<br>R2- 465-468 |  |  |  |  |

| 3             | 1        | bistable multivibrator                                                                    | T2-321-324<br>R2- 469-470  |  |  |  |  |

| 4             | 1        | VCO IC 566 (Block diagram and pin description)                                            |                            |  |  |  |  |

Lesson Plan <sup>2018-2020</sup> Batch

| 5  | 1  | PLL IC 565 (Block diagram and pin description)                                | T2- 326-330                 |

|----|----|-------------------------------------------------------------------------------|-----------------------------|

| 6  | 1  | Fixed voltage Regulator ICs 7800 and 7900 series                              |                             |

| 7  | 1  | Voltage Regulator IC 723 (description, designing for<br>low and high voltage) | T2- 421-428                 |

| 8  | 1  | Revision                                                                      |                             |

|    | To | otal No. of Hours Planned For Unit II = 8                                     |                             |

|    | •  | UNIT-III                                                                      |                             |

| 1  | 1  | Microprocessor Architecture                                                   | T3- 57-63                   |

| 2  | 1  | Continuation                                                                  |                             |

| 3  | 1  | Pin out configuration of 8085                                                 | T4- 16-21                   |

| 4  | 1  | Continuation                                                                  |                             |

| 5  | 1  | bus organization and timings –address bus, data bus,                          | T3- 59-60                   |

| 6  | 1  | Continuation                                                                  |                             |

| 7  | 1  | multiplexing address/data bus and control and status signal,                  | T3- 60                      |

| 8  | 1  | Interrupts: maskable and non-maskable<br>interrupt(concept),8085 interrupt    | T3- 385-388,<br>T3- 376-385 |

| 9  | 1  | Continuation                                                                  |                             |

| 10 | 1  | Revision                                                                      |                             |

|    |    |                                                                               |                             |

|    |    | UNIT-IV                                                                       |                             |

| 1  | 1  | Instruction set-Data transfer                                                 | T3- 176-179,                |

| 2  | 1  | Arithmetic Instruction                                                        | T3-186-191                  |

| 3  | 1  | logical and branch instruction                                                | T3- 196-201,<br>204-206     |

| 4  | 1  | Addressing modes                                                              | T3- 179-183                 |

| 5  | 1  | 16 bit data transfer and memory related instructions                          | T3- 180, 295-<br>315        |

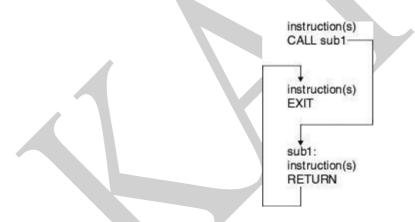

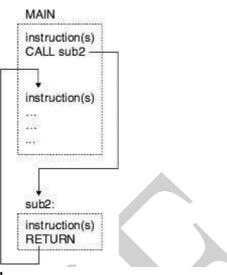

| 6  | 1  | stack and subroutine instructions                                             |                             |

| 7  | 1  | Simple Program: 8 bit addition-subtraction                                    | W1                          |

| 8  | 1  | Simple Program: multiplication- finding largest and<br>smallest number        | W1, W2                      |

| 9  | 1  | ascending and descending order, 16 bit addition                               | W1                          |

| 10 | 1  | Revision                                                                      | <u> </u>                    |

|    |    | al No. of Hours Planned For Unit IV = 10                                      |                             |

|    | 10 |                                                                               |                             |

Lesson Plan <sup>2018-2020</sup> Batch

|    | UNIT-V                                     |                                  |                           |  |  |  |  |  |  |

|----|--------------------------------------------|----------------------------------|---------------------------|--|--|--|--|--|--|

| 1  | 1                                          | T3-426-431                       |                           |  |  |  |  |  |  |

| 2  | 1                                          | peripheral I/O instructions      | T3- 460-468               |  |  |  |  |  |  |

| 3  | 1                                          | Interfacing programs             | T3-447                    |  |  |  |  |  |  |

| 4  | 1                                          | Data Converters, LED interfacing | T5-438-454,<br>T3-468-470 |  |  |  |  |  |  |

| 5  | 1                                          | stepper motor interfacing        | T4-408-410                |  |  |  |  |  |  |

| 6  | 1                                          | Hex Keyboard Interfacing         | T3-479-485,<br>T4-386-389 |  |  |  |  |  |  |

| 7  | 1                                          | Revision                         |                           |  |  |  |  |  |  |

| 8  | 1                                          | Old question paper discussion    |                           |  |  |  |  |  |  |

| 9  | 1                                          | Old question paper discussion    |                           |  |  |  |  |  |  |

| 10 | 1                                          | Old question paper discussion    |                           |  |  |  |  |  |  |

|    | Total No. of Hours Planned For Unit V = 10 |                                  |                           |  |  |  |  |  |  |

### **Text Books:**

T1- Digital fundamentals by Thomas L Flyod-8<sup>th</sup> edition, Pearson Education

T2- Linear Integrated Circuits- V.A.Bakshi, A.P.Godse, Technical Publications

T3- Microprocessor architecture, programming and applications with the 8085- Ramesh Gaonkar, 5<sup>th</sup> edition, penram international publishing Pvt ltd.

T4- Microprocessor and its applications, A.Nagoor Kanni, RBA Publications, Chennai.

T5-Digital Principles and Applications-Donald P Leach, Albert Paul Malvino, Goutam Saha, 7<sup>th</sup> Edition, Tata McGRaw Hill

### **Reference Books:**

R1- Digital Principles and applications-Donald P Leach, Albert Paul Malvino, Goutam Saha-6<sup>th</sup> Edition, Tata McGraw Hill Publication Pvt. Ltd., New Delhi

R2-Electronic Principles, Sahdev.S.K. Dhanpat Rai & sons

### Websites

W1- scanfree.com/microprocessor/programs-for-8085-microprocessor-learners.

W2- programmings4u.blogspot.in/2013/06/largesmall.html

# Unit- I

**Flip Flops :** SR, JK, JK Master Slave, T Flip flop & D Flip Flop (Symbol and Truth table)Registers (Types, shift operations) - Counters (Types, Designing of MOD 5 synchronous Counter, Construction and truth table - verification of MOD 16 Asynchronous UP, Down counter) - Multiplexer And demultiplexer (16:1 and 1:16 description and truth table verification) - Decoders and encoders (Definitions, Seven segment decoder, decimal to BCD encoder)

# Flip-Flop

A flip-flop or latch is a circuit that has two stable states and can be used to store state information. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are fundamental building blocks of digital electronics systems used in computers, communications, and many other types of systems.

Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a "one" and the other represents a "zero".

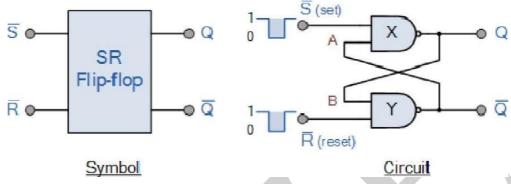

# **SR Flip-Flop**

The **SR flip-flop**, also known as a *SR Latch*, can be considered as one of the most basic sequential logic circuit possible. This simple flip-flop is basically a one-bit memory bistable device that has two inputs, one which will "SET" the device (meaning the output = "1"), and is labelled S and another which will "RESET" the device (meaning the output = "0"), labelled R.

Then the SR description stands for "Set-Reset". The reset input resets the flip-flop back to its original state with an output Q that will be either at a logic level "1" or logic "0" depending upon this set/reset condition.

A basic NAND gate SR flip-flop circuit provides feedback from both of its outputs back to its opposing inputs and is commonly used in memory circuits to store a single data bit. Then the SR flip-flop actually has three inputs, Set, Reset and its current output Q relating to it's current state or history. The term "Flip-flop" relates to the actual operation of the device, as it can be "flipped" into one logic Set state or "flopped" back into the opposing logic Reset state.

### The NAND Gate SR Flip-Flop

The simplest way to make any basic single bit set-reset SR flip-flop is to connect together a pair of cross-coupled 2-input NAND gates as shown, to form a Set-Reset Bistable also known as an active

LOW SR NAND Gate Latch, so that there is feedback from each output to one of the other NAND gate inputs. This device consists of two inputs, one called the *Set*, S and the other called the *Reset*, R with two corresponding outputs Q and its inverse or complement Q (not-Q) as shown below.

# The Basic SR Flip-flop

# The Set State

Consider the circuit shown above. If the input R is at logic level "0" (R = 0) and input S is at logic level "1" (S = 1), the NAND gate *Y* has at least one of its inputs at logic "0" therefore, its output Q must be at a logic level "1" (NAND Gate principles). Output Q is also fed back to input "A" and so both inputs to NAND gate *X* are at logic level "1", and therefore its output Q must be at logic level "0" Again NAND gate principals. If the reset input R changes state, and goes HIGH to logic "1" with S remaining HIGH also at logic level "1", NAND gate *Y* inputs are now R = "1" and B = "0". Since one of it inputs is still at logic level "0" the output at Q still remains HIGH at logic level "1" and there is no change of state. Therefore, the flip-flop circuit is said to be "Latched" or "Set" with Q = "1" and Q = "0".

# **Reset State**

In this second stable state, Q is at logic level "0", (not Q = "0") its inverse output at Q is at logic level "1", (Q = "1"), and is given by R = "1" and S = "0". As gate X has one of its inputs at logic "0" its output Q must equal logic level "1" (again NAND gate principles). Output Q is fed back to input "B", so both inputs to NAND gate Y are at logic "1", therefore, Q = "0".

If the set input, S now changes state to logic "1" with input R remaining at logic "1", output Q still remains LOW at logic level "0" and there is no change of state. Therefore, the flip-flop circuits "Reset" state has also been latched and we can define this "set/reset" action in the following truth table.

It can be seen that when both inputs S = "1" and R = "1" the outputs Q and Q can be at either logic level "1" or "0", depending upon the state of the inputs S or R BEFORE this input condition existed. Therefore the condition of S = R = "1" does not change the state of the outputs Q and Q.

However, the input state of S = "0" and R = "0" is an undesirable or invalid condition and must be avoided. The condition of S = R = "0" causes both outputs Q and Q to be HIGH together at logic level "1" when we would normally want Q to be the inverse of Q. The result is that the flip-flop looses control of Q and Q, and if the two inputs are now switched "HIGH" again after this condition to logic "1",

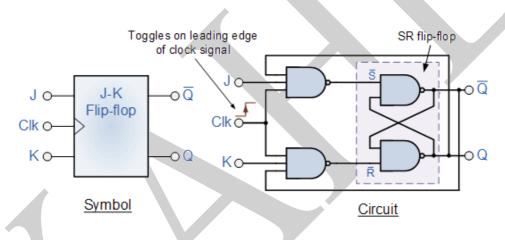

# JK Flip Flop

Both the S and the R inputs of the previous SR bistable have now been replaced by two inputs called the J and K inputs, respectively after its inventor Jack Kilby. Then this equates to: J = S and K = R.

The two 2-input AND gates of the gated SR bistable have now been replaced by two 3input NAND gates with the third input of each gate connected to the outputs at Q and Q. This cross coupling of the SR flip-flop allows the previously invalid condition of S = "1" and R = "1" state to be used to produce a "toggle action" as the two inputs are now interlocked.

If the circuit is now "SET" the J input is inhibited by the "0" status of Q through the lower NAND gate. If the circuit is "RESET" the K input is inhibited by the "0" status of Q through the upper NAND gate. As Q and Q are always different we can use them to control the input. When both inputs J and K are equal to logic "1", the JK flip flop toggles as shown in the following truth table.

|         | Inp | ut    | Outpu | ıt |               |

|---------|-----|-------|-------|----|---------------|

|         | G   | 5     | 0     | 0  | Description   |

|         | S   | R     | Q     | Q  |               |

|         | 0   | 0     | 0     | 0  | Memory        |

| Same    | 0   | 0     | 0     |    |               |

|         | 0   | 0     | 0     | 1  | no change     |

| as      | 0   | · 1   | 1 ·   | 0  |               |

| for the |     | • • • |       |    | . Reset Q » 0 |

|         | 0   | 1     | 0     | 1  |               |

| SR      |     |       |       |    |               |

| Latch   | 1   | 0     | 0     | 1  |               |

| •       |     |       |       |    | · Set Q » 1   |

|         | 1   | · 1 · | 0     | 1  | ·             |

|         | 1   | 1     | 0 .   | 1  |               |

| Toggle  | •   | • •   | •     |    | •             |

| · · ·   | •   |       | · ·   |    | Toggle        |

| action  | • 1 | · 1 · | 1 ·   | 0  |               |

|         |     |       |       |    |               |

# Truth Table for the JK Function

Then the JK flip-flop is basically an SR flip flop with feedback which enables only one of its two input terminals, either SET or RESET to be active at any one time thereby eliminating the invalid condition seen previously in the SR flip flop circuit.

when both the J and the K inputs are at logic level "1" at the same time, and the clock input is pulsed "HIGH", the circuit will "toggle" from its SET state to a RESET state, or visa-versa. This results in the JK flip flop acting more like a T-type toggle flip-flop when both terminals are "HIGH".

Although this circuit is an improvement on the clocked SR flip-flop it still suffers from timing problems called "race" if the output Q changes state before the timing pulse of the clock input has time to go "OFF". To avoid this the timing pulse period (T) must be kept as short as possible (high frequency).

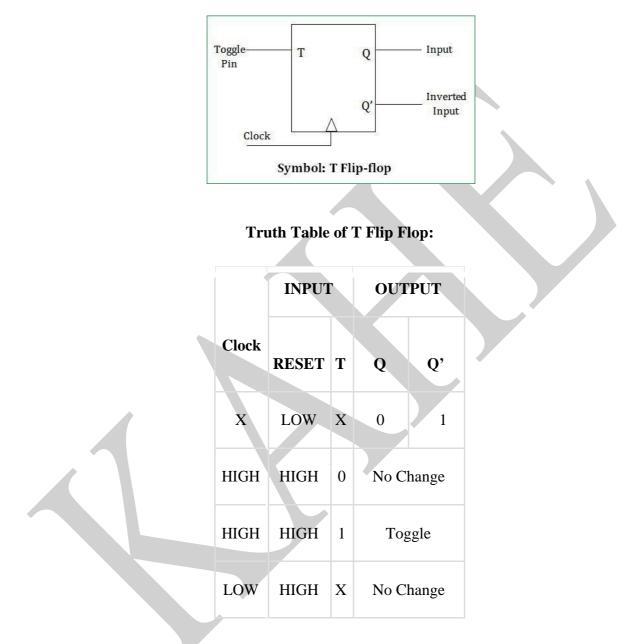

# T Flip flop

The name T flip-flop is termed from the nature of toggling operation. The major applications of T flip-flop are counters and control circuits. T flip flop is modified form of JK flip-flop making it to operate in toggling region.

Whenever the clock signal is LOW, the input is never going to affect the output state. The clock

has to be high for the inputs to get active. Thus, T flip-flop is a controlled Bi-stable latch where the clock signal is the control signal. Thus, the output has two stable states based on the inputs

The T-Flip flop is the modified form of JK flip flop. The Q and Q' represents the output states of the flip flop. According to the table, based on the input the output changes its state. But the important thing to consider is all these can occur only in the presence of the clock signal. This works unlike SR flip flop & JK flip flop for the complimentary inputs. This only has the toggling function.

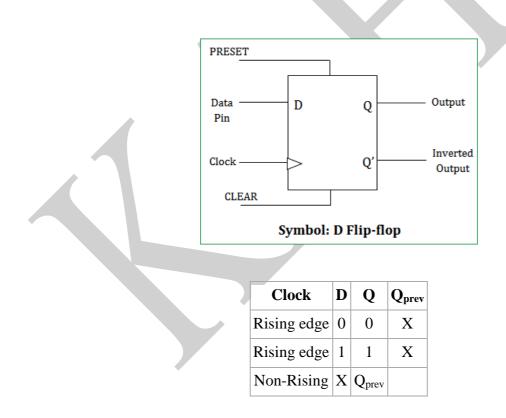

# D Flip-flop

D Flip-flops are used as a part of memory storage elements and data processors as well. D flipflop can be built using NAND gate or with NOR gate. Due to its versatility they are available as IC packages. The major applications of D flip-flop are to introduce delay in timing circuit, as a buffer, sampling data at specific intervals. D flip-flop is simpler in terms of wiring connection compared to JK flip-flop. Here we are using **NAND gates** for demonstrating the D flip flop

Whenever the clock signal is LOW, the input is never going to affect the output state. The clock has to be high for the inputs to get active. Thus, D flip-flop is a controlled Bi-stable latch where the clock signal is the control signal. Again, this gets divided **into** positive edge triggered D flip flop and negative edge triggered D flip-flop.

The D (Data) is the input state for the D flip-flop. The Q and Q' represents the output states of the flip-flop. According to the table, based on the inputs the output changes its state. But, the important thing to consider is all these can occur only in the presence of the clock signal. This, works exactly like SR flip-flop for the complimentary inputs alone.

# REGISTERS

When a number of flip flops are connected in series, this arrangement is called a Register. The stored information can be transferred within the registers; these are called as 'Shift Registers'. A shift register is a sequential circuit which stores the data and shifts it towards the output on every clock cycle. Basically shift registers are of 4 types. They are

- Serial In Serial Out shift register

- Serial In parallel Out shift register

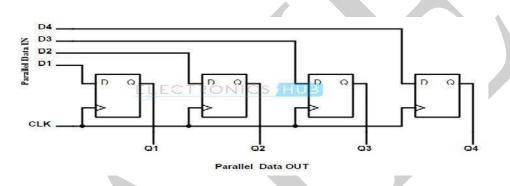

- Parallel In Serial Out shift register

- Parallel In parallel Out shift register

# Serial in Serial Out Shift Register

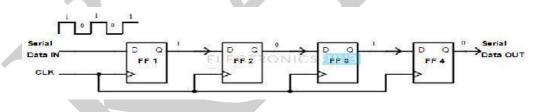

The input to this register is given in serial fashion i.e. one bit after the other through a single data line and the output is also collected serially. The data can be shifted only left or shifted only right. Hence it is called Serial in Serial out shift register or a SISO shift register.

As the data is fed from right as bit by bit, the shift register shifts the data bits to left. A 4-bit SISO shift register consists of 4 flip flops and only three connections.

The registers which will shift the bits to left are called "Shift left registers".

The registers which will shift the bits to right are called "Shift right registers".

As the clock signal is connected to all the 4 flip flops, the serial data is connected to the left most or right most flip flop. The output of the first flip flop is connected to the input of the next flip flop and so on.

In the above diagram, we see the shift right register; feeding the serial data input from the left side of the flip flop arrangement.

In this shift register, when the clock signal is applied and the serial data is given; only one bit will be available at output at a time in the order of the input data. The use of SISO shift register is to act as temporary data storage device. But the main use of a SISO is to act as a delay element.

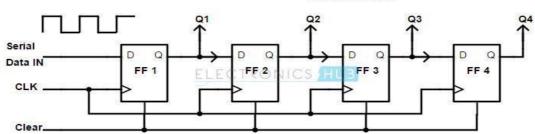

# Serial in Parallel Out shift register

The input to this register is given in serial and the output is collected in parallel. The clear (CLR) signal is connected in addition to clock signal to all the 4 flip flops in order to RESET them and the serial

data is connected to the flip flop at either end (depending on shift left register or shift right register). The output of the first flip flop is connected to the input of the next flip flop and so on. All the flip flops are connected with a common clock.

Unlike the serial in serial out shift registers, the output of Serial in Parallel out (SIPO) shift register is collected at each flip flop.  $Q_1$ ,  $Q_2$ ,  $Q_3$  and  $Q_4$  are the outputs of first, second, third and fourth flip flops, respectively. Parallel Outputs

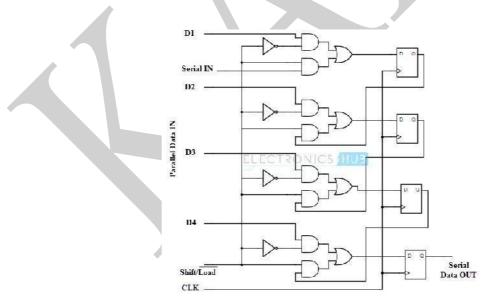

# Parallel in Serial out shift register

The input to this register is given in parallel i.e. data is given separately to each flip flop and the output is collected in serial at the output of the end flip flop.

The clock input is directly connected to all the flip flops but the input data is connected individually to each flip flop through a mux (multiplexer) at input of every flip flop. Here D1, D2, D3 and D4 are the individual parallel inputs to the shift register. In this register the output is collected in serial.

The output of the previous flip flop and parallel data input are connected to the input of the MUX and the output of MUX is connected to the next flip flop. A Parallel in Serial out (PISO) shift register converts parallel data to serial data. Hence they are used in communication lines where a number of data

lines are multiplexed into single serial data line.

# Parallel in Parallel out shift register

In this register, the input is given in parallel and the output also collected in parallel. The clear (CLR) signal and clock signals are connected to all the 4 flip flops. Data is given as input separately for each flip flop and in the same way, output also collected individually from each flip flop.

In the 4 stage parallel in parallel out register. Qa, Qb, Qc and Qd are the parallel outputs and Pa, Pb, Pc and Pd are the individual parallel inputs. There are no interconnections between any of the four flip flops.

A Parallel in Parallel out (PIPO) shift register is used as a temporary storage device and also as a delay element similar to a SISO shift register.

# COUNTERS

A **counter** is a device which stores (and sometimes displays) the number of times a particular event or process has occurred, often in relationship to a clock signal.

# Types of counter

- Asynchronous (ripple) counter changing state bits are used as clocks to subsequent state flip-flops

- Synchronous counter all state bits change under control of a single clock

- Decade counter counts through ten states per stage

- Up/down counter counts both up and down, under command of a control input

- Ring counter formed by a shift register with feedback connection in a ring

- Johnson counter a *twisted* ring counter

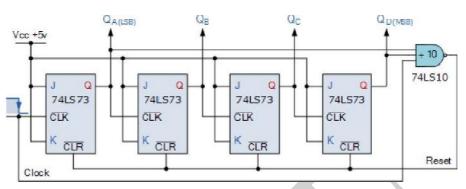

# **Asynchronous Decade Counter**

This type of asynchronous counter counts upwards on each trailing edge of the input clock signal starting from 0000 until it reaches an output 1001 (decimal 9). Both outputs QA and QD are now equal to logic "1". On the application of the next clock pulse, the output from the 74LS10 NAND gate changes state from logic "1" to a logic "0" level.

As the output of the NAND gate is connected to the CLEAR (CLR) inputs of all the 74LS73 J-K Flip-flops, this signal causes all of the Q outputs to be reset back to binary 0000 on the count of 10. As outputs QA and QD are now both equal to logic "0" as the flip-flop's have just been reset, the output of the NAND gate returns back to a logic level "1" and the counter restarts again from 0000. We now have a decade or Modulo-10 up-counter.

|    | Clock | Output b | it Pattern |              |           | Decimal |

|----|-------|----------|------------|--------------|-----------|---------|

|    | Count | QD       | QC         | QB           | QA        | Value   |

| 1  |       | 0        | 0          | 0            | 0         | 0       |

| 2  |       | 0        | 0          | 0            | 1         | 1       |

| 3  |       | 0        | 0          | 1            | 0         | 2       |

| 4  |       | 0        | 0          | 1            | 1         | 3       |

| 5  |       | 0        | 1          | 0            | 0         | 4       |

| 6  |       | 0        | 1          | 0            | 1         | 5       |

| 7  |       | 0        | 1          | 1            | 0         | 6       |

| 8  |       | 0        | 1          | 1            | 1         | 7       |

| 9  |       | 1        | 0          | 0            | 0         | 8       |

| 10 |       | 1        | 0          | 0            | 1         | 9       |

| 11 |       |          | Counter F  | Resets its ( | k to Zero |         |

Multiplexer

4

# KARPAGAM ACADEMY OF HIGHER EDUCATION

**CLASS: II MSc Physics** COURSE NAME: DIGITAL ELECTRONICS AND MICROPROCESSOR **COURSE CODE: 19PHP304 UNIT: I (FLIP-FLOPS)** BATCH-2018-2020

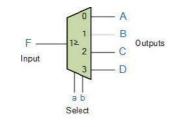

Multiplexer is a device that has multiple inputs and a single line output. The select lines determine which input is connected to the output, and also to increase the amount of data that can be sent over a network within certain time. It is also called a data selector.

The single pole multi-position switch is a simple example of non-electronic circuit of multiplexer, and it is widely used in many electronic circuits. The multiplexer is used to perform high-speed switching and is constructed by electronic components.

Multiplexers are capable of handling both analog and digital applications. In analog applications, multiplexers are made up of of relays and transistor switches, whereas in digital applications, the multiplexers are built from standard logic gates. When the multiplexer is used for digital applications, it is called a digital multiplexer.

# **Multiplexer Types**

- Multiplexers are classified into four types:

- 2-1 multiplexer (1select line)

- 4-1 multiplexer (2 select lines)

- 8-1 multiplexer(3 select lines)

- 16-1 multiplexer (4 select lines

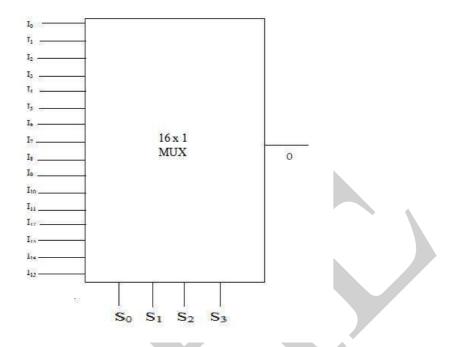

Multiplexer is one of the basic building units of a computer system which in principle allows sharing of a common line by more than one input lines. It connects multiple input lines to a single output line. At a specific time one of the input lines is selected and the selected input is passed on to the output line.

Relation between multiple Input lines and Selection lines

Input lines  $16 = 2^4$  i.e. 4 Selection lines

Input lines will be  $I_0 - I_{15}$

Selection lines will be  $S_0 - S_3$

# **Block Diagram:**

The diagram will be same as of the block diagram of 16-to-1 line multiplexer in which 8-to-1 line multiplexer Selection lines will be  $S_0 - S_2$  and  $S_3$  will be connected to 2-to-1 line multiplexer Selection and First 8-to-1 line multiplexer Input lines will be  $I_0 - I_7$  and Second8-to-1 line multiplexer Input lines will be  $I_8 - I_{15}$

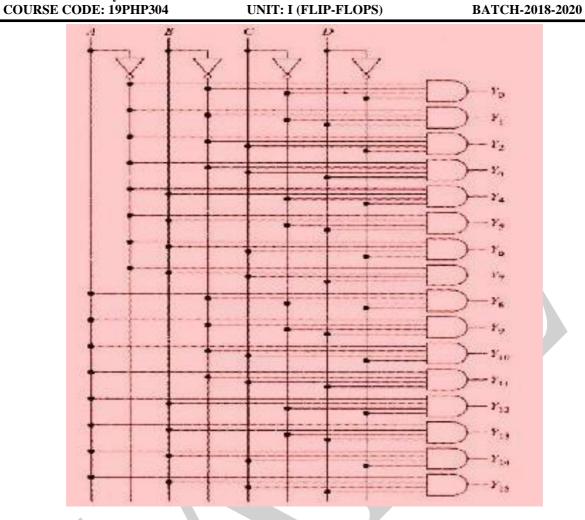

# Demultiplexer (1:16 description and truth table verification)

De-multiplexer is also a device with one input and multiple output lines. It is used to send a signal to one of the many devices. The main difference between a multiplexer and a de-multiplexer is that a multiplexer takes two or more signals and encodes them on a wire, whereas a de-multiplexer does reverse to what the multiplexer does.

1-16 demultiplexer (4 select lines)

The only input are the control input ABCD. In this logic circuit only 1 of the 16 output lines is high and therefore it is called 1 of 16 demultiplexer.

# KARPAGAM ACADEMY OF HIGHER EDUCATION

COURSE NAME: DIGITAL ELECTRONICS AND MICROPROCESSOR

# Truth table of 1 to 16 DEMUX

**CLASS: II MSc Physics**

| - |    |     |     |    |    |    |    |    |    |    |    |    | · · · · · |    |     |     |     |     |     |     |

|---|----|-----|-----|----|----|----|----|----|----|----|----|----|-----------|----|-----|-----|-----|-----|-----|-----|

|   |    | INP | UTS |    |    |    |    |    |    |    |    | OU | TPU       | TS |     |     |     |     |     |     |

| Ē | A3 | A2  | A1  | A0 | 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08        | 09 | 010 | 011 | 012 | 013 | 014 | 015 |

| 1 | X  | Х   | Х   | Х  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0         | 0  | 0   | 0   | 0   | 0   | 0   | 0   |

| 0 | 0  | 0   | 0   | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0         | 0  | 0   | 0   | 0   | 0   | 0   | 0   |

| 0 | 0  | 0   | 0   | 1  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0         | 0  | 0   | 0   | 0   | 0   | 0   | 0   |

| 0 | 0  | 0   | 1   | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0         | 0  | 0   | 0   | 0   | 0   | 0   | 0   |

| 0 | 0  | 0   | 1   | 1  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0         | 0  | 0   | 0   | 0   | 0   | 0   | 0   |

| 0 | 0  | 1   | 0   | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0         | 0  | 0   | 0   | 0   | 0   | 0   | 0   |

| 0 | 0  | 1   | 0   | 1  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0         | 0  | 0   | 0   | 0   | 0   | 0   | 0   |

| 0 | 0  | 1   | 1   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0         | 0  | 0   | 0   | 0   | 0   | 0   | 0   |

| 0 | 0  | 1   | 1   | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0         | 0  | 0   | 0   | 0   | 0   | 0   | 0   |

| 0 | 1  | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1         | 0  | 0   | 0   | 0   | 0   | 0   | 0   |

| 0 | 1  | 0   | 0   | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0         | 1  | 0   | 0   | 0   | 0   | 0   | 0   |

| 0 | 1  | 0   | 1   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0         | 0  | 1   | 0   | 0   | 0   | 0   | 0   |

| 0 | 1  | 0   | 1   | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0         | 0  | 0   | 1   | 0   | 0   | 0   | 0   |

| 0 | 1  | 1   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0         | 0  | 0   | 0   | 1   | 0   | 0   | 0   |

| 0 | 1  | 1   | 0   | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0         | 0  | 0   | 0   | 0   | 1   | 0   | 0   |

| 0 | 1  | 1   | 1   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0         | 0  | 0   | 0   | 0   | 0   | 1   | 0   |

| 0 | 1  | 1   | 1   | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0         | 0  | 0   | 0   | 0   | 0   | 0   | 1   |

### Decoders

A **decoder** is a device which does the reverse of an encoder, undoing the encoding so that the original information can be retrieved. The same method used to encode is usually just reversed in order to decode.

A decoder can take the form of a multiple-input, multiple-output logic circuit that converts coded inputs into coded outputs, where the input and output codes are different. e.g. n-to-2<sup>n</sup>, binary-coded decimal decoders. Enable inputs must be on for the decoder to function, otherwise its outputs assume a single "disabled" output code word. Decoding is necessary in applications such as data multiplexing, 7 segment display and memory address decoding.

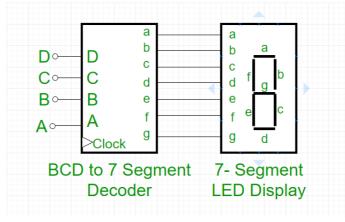

# BCD to seven segment decoder

In **Binary Coded Decimal (BCD)** encoding scheme each of the decimal numbers (0-9) is represented by its equivalent binary pattern (which is generally of 4-bits).

Whereas, **Seven segment** display is an electronic device which consists of seven Light Emitting Diodes (LEDs) arranged in some definite pattern (common cathode or common anode type), which is used to display Hexadecimal numerals (in this case decimal numbers, as input is BCD i.e., 0-9).BCD to seven segment decoder has four input lines (A, B, C and D) and 7 output lines (a, b, c, d, e, f and g), this output is given to seven segment LED display which displays the decimal number depending upon inputs.

Two types of seven segment LED display:

1. **Common Cathode Type:** In this type of display all cathodes of the seven LEDs are connected together to the ground or –Vcc (hence, common cathode) and LED displays digits when some 'HIGH' signal is supplied to the individual anodes.

2. **Common Anode Type:** In this type of display all the anodes of the seven LEDs are connected to battery or +Vcc and LED displays digits when some 'LOW' signal is supplied to the individual cathodes.

But, seven segment display does not work by directly supplying voltage to different segments of LEDs. First, our decimal number is changed to its BCD equivalent signal then BCD to seven segment decoder converts that signals to the form which is fed to seven segment display.

This BCD to seven segment decoder has four input lines (A, B, C and D) and 7 output lines (a, b, c, d, e, f and g), this output is given to seven segment LED display which displays the decimal number depending upon inputs.

| Digit | A | В | С | D | а | b | с | d | e | f | g |

|-------|---|---|---|---|---|---|---|---|---|---|---|

| 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 1     | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 |

| 2     | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| 3     | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

| 4     | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 |

| 5     | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 |

| 6     | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 7     | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

| 8     | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 9     | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

From the above truth table, the Boolean expressions of each output functions can be written as

$$\begin{aligned} a &= F1 (A, B, C, D) = \sum m (0, 2, 3, 5, 7, 8, 9) \\ b &= F2 (A, B, C, D) = \sum m (0, 1, 2, 3, 4, 7, 8, 9) \\ c &= F3 (A, B, C, D) = \sum m (0, 1, 3, 4, 5, 6, 7, 8, 9) \\ d &= F4 (A, B, C, D) = \sum m (0, 2, 3, 5, 6, 8) \\ e &= F5 (A, B, C, D) = \sum m (0, 2, 6, 8) \\ f &= F6 (A, B, C, D) = \sum m (0, 4, 5, 6, 8, 9) \\ g &= F7 (A, B, C, D) = \sum m (2, 3, 4, 5, 6, 8, 9) \end{aligned}$$

# **K-Map Simplification**

The below figures shows the k-map simplification for the common cathode seven-segment decoder in order to design the combinational circuit.

### **KARPAGAM ACADEMY OF HIGHER EDUCATION** CLASS: II MSc Physics COURSE NAME: DIGITAL ELECTRONICS AND MICROPROCESSOR **COURSE CODE: 19PHP304 UNIT: I (FLIP-FLOPS)** BATCH-2018-2020 ср<sub>|00</sub> CD ABCD AB AB × × × × × × × × × × × × × X x X X X $\mathbf{c} = \mathbf{B} + \overline{\mathbf{C}} + \mathbf{D}$ $\mathbf{b} = \overline{\mathbf{B}} + \overline{\mathbf{C}} \ \overline{\mathbf{D}} + \mathbf{C}\mathbf{D}$ $\mathbf{a} = \mathbf{A} + \mathbf{C} + \mathbf{B}\mathbf{D} + \overline{\mathbf{B}\mathbf{D}}$ CD ABCD CD AB AB × × × × × × X X × X X × X × × × x × $\mathbf{f} = \mathbf{A} + \overline{\mathbf{C}} \ \overline{\mathbf{D}} + \mathbf{B} \ \overline{\mathbf{C}} + \mathbf{B} \ \overline{\mathbf{D}}$ $e = \overline{B} \overline{D} + C \overline{D}$ $\mathbf{d} = \mathbf{\overline{B}} \ \mathbf{\overline{D}} + \mathbf{C} \ \mathbf{\overline{D}} + \mathbf{B} \ \mathbf{\overline{C}} \ \mathbf{D} + \mathbf{\overline{B}} \ \mathbf{C} + \mathbf{A}$ CD AB

× × × × × ×  $\mathbf{g} = \overline{\mathbf{B}} \mathbf{C} + \mathbf{C} \overline{\mathbf{D}} + \mathbf{B} \overline{\mathbf{C}} + \mathbf{B} \overline{\mathbf{C}} + \mathbf{A}$

From the above simplification, we get the output values as

### KARPAGAM ACADEMY OF HIGHER EDUCATION

CLASS: II MSc Physics COURSE CODE: 19PHP304 COURSE NAME: DIGITAL ELECTRONICS AND MICROPROCESSOR UNIT: I (FLIP-FLOPS) BATCH-2018-2020

$a = A + C + BD + \overline{B} \overline{D}$   $b = \overline{B} + \overline{C} \overline{D} + CD$   $c = B + \overline{C} + D$   $d = \overline{B} \overline{D} + C \overline{D} + B \overline{C} D + \overline{B} C + A$   $e = \overline{B} \overline{D} + C \overline{D}$   $f = A + \overline{C} \overline{D} + B \overline{C} + B \overline{D}$  $g = A + B \overline{C} + \overline{B} C + C \overline{D}$

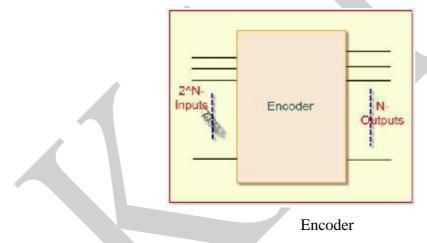

# Encoders

An encoder is a device, that converts information from one format to another. The purpose of encoder is standardization, speed, security, or saving space by shrinking size. Encoders are combinational logic circuits and they are exactly opposite of decoders. They accept one or more inputs and generate a multi bit output code.

# **Decimal to BCD Encoder**

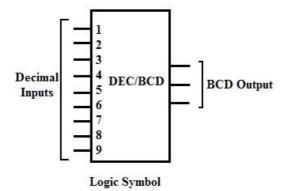

This type of encoder usually consists of ten input lines and 4 output lines. Each input line corresponds to the each decimal digit and 4 outputs correspond to the BCD code.

This encoder accepts the decoded decimal data as an input and encodes it to the BCD output which is available on the output lines.

The figure below shows the basic logic symbol of decimal to BCD encoder along with its truth table. The truth table represents the BCD code for each decimal digit.

From this we can formulate the relationship between the BCD bit and decimal digit. It is

important to note that there is no explicit input line for decimal zero. When this condition occurs, i.e.,

decimal inputs 1 to 9 all are zero, then the BCD output is 0000.

From the above table, we get the expressions as

$$Y3 = D8 + D9$$

$$Y2 = D4 + D5 + D6 + D7$$

$$Y1 = D2 + D3 + D6 + D7$$

$$Y0 = D1 + D3 + D5 + D7 + D9$$

From the above expressions, the decimal to BCD encoder logic circuit can be implemented by using set of OR gates.

# **Possible Questions**

# 2 Marks

- 1. Define flip-flop.

- 2. What is called toggle?

- 3. Define multiplexer and demultiplexer.

- 4. Define decoder and encoder.

- 5. Construct 4 to 1 MUX.

- 6. Write the truth table of BCD to 7 segment display.

# 8 Marks

- 1. What are the types of flip flop? Explain clocked RS flip-flop.

- 2. What is called racing in JK flip-flop? How it is solved in JK master-slave flip-flop?

- 3. Explain the shift left shift right shift registers.

- 4. Explain mod 16 counter.

- 5. With a neat diagram construct and explain the working of D flip-flop.

- 6. What is called as multiplexer? Draw the circuit for an 8 input multiplexer and explain it.

- 7. Discuss about 2 to 4 and 3 to 8 decoder.

- 8. Discuss the working of a multiplexer in detail.

- 9. With a neat circuit explain BCD to seven segment decoder..

- 10. What is an encoder? Give the truth table for a octal to binary encoder.

- 11. Design a 16-inpt multiplexer using two 8-inpts multiplexers having active low strobe input.

- 12. (i) An 8 bit DAC has an output voltage range of 0-2.55 V. Define its resolution in two ways.

- a. The digital input for a 4-bit DAC is 0110. Calculate its final output voltage.

CLASS: II MSc Physics COURSE CODE: 19PHP304

# UNIT-2

**Special Function ICs:** Timer IC 555 (Block diagram, pin description), Application as Astable, monostable, bistable multivibrator - VCO IC 566 (Block diagram and pin description) - PLL IC 565 (Block diagram and pin description) - Fixed voltage Regulator ICs 7800 and 7900 series - Voltage Regulator IC 723 (description, designing for low and high voltage)

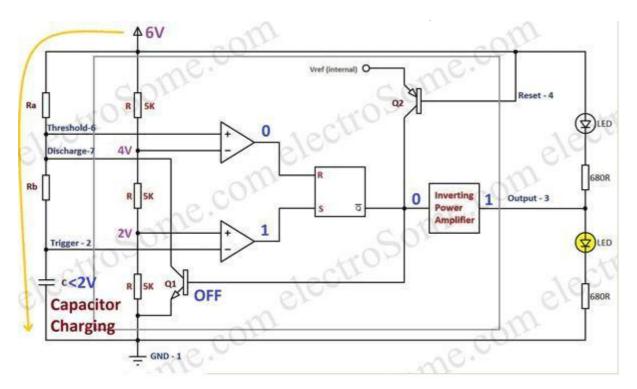

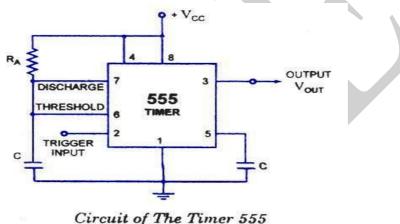

### Special Function Ics: Timer Ic 555 (Block Diagram, Pin Description)

It is a monolithic timing circuit that gives precise and highly stable delays of time or oscillation. These types of ICs are very cheap and reliable in cost when we compared with the OP-Amp applications in the same areas. These ICs are used as an astable and monostable multivibrators in digital log ic probes, DC-DC converters, tachometers, analog frequency meters, voltage regulators, temperature controlled and measurement devices.

The designing of IC 555 timers can be done by using various electrical and electronic components like transistors, resistors, diodes and a flip flop. The operating range of this IC ranges from 4.5V -15V DC supply. The functional parts of the 555 timer IC include flip-flop, voltage divider and a comparator. The main function of this IC is to generate an accurate timing pulse. In the monostable mode, the delay of this IC is controlled by the external components like a resistor and capacitor. In the astable mode, both the duty cycle & frequency are controlled by two external resistors and one capacitor.

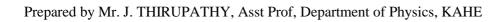

The pin configuration of this I C is shown below.

# Pin Configuration of 555 Timer IC GND Pin

Pin-1 is a GND pin which is used to supply a zero voltage to the IC.

# **Trigger Pin**

Pin-2 is a trigger pin which is used to convert the FF from set to RST (reset). The output of the timer depends on the amplitude of the external trigger pulse that is applied to the trigger pin.

### **Output Pin**

Pin-3 is an output pin.

### **Reset Pin**

Pin-4 is a RST pin. When the negative pulse is applied to this pin to disable or reset, and false triggering can be neglected by connecting to VCC.

# **Control Voltage Pin**

Pin-5 is the control voltage pin used to control the pulse width of the output waveform and also the levels of threshold and trigger. When an external voltage is applied to this pin, then the output waveform will be modulated

### **Threshold Pin**

Pin-6 is the threshold pin, when the voltage is applied to threshold pin, then it contrasts with a reference voltage. The set state of the FF can be depends on the amplitude of this pin.

### **Discharge Pin**

Pin-7 is the discharge pin, when the output of the open collector discharges a capacitor between the intervals, then it toggles the output from high to low.

### **Supply Terminal**

Pin-8 is the voltage supply pin which is used to supply the voltage to the IC with respect to the ground terminal.

# Application As Astable Multivibrator

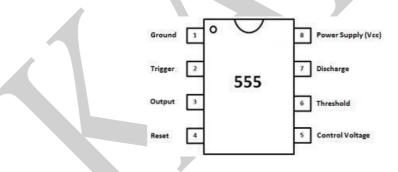

Astable Multivibrator using 555 An Astable Multivibrator is an oscillator circuit that continuously produces rectangular wave without the aid of external triggering. So Astable Multivibrator is also known as Free Running Multivibrator. Astable Multivibrator using 555 Timer is very simple, easy to design, very stable and low cost. It can be used for timing from microseconds to hours. Due to these reasons 555 has a large number of applications and it is a popular IC among electronics hobbyists.

CLASS: II MSc Physics COURSE CODE: 19PHP304

# Astable Multivibrator using 555 Timer Circuit Diagram

The circuit diagram of a 555 Timer wired in Astable Mode. 8th pi n and 1st pin of the IC are used to give power, V cc and GND respectively. The 4th pin is RESET pin which is active low and is connected to Vcc to avoid accidental resets. 5th pin is the Control Voltage pin which is not used. So to avoid high frequency noises it is connected to a capacitor C' whose other end is connected to ground. Usually  $C' = 0.01\mu$ F. The T rigger (pin 2) and Threshold (pin 6) inputs are connected to the capacitor which determines the output of the timer. Discharge pin (pin 7) is connected to the resistor Rb such that the capacitor can discharge through Rb. Diode D connected in parallel to Rb is only used when an output of duty cycle less than or equal to 50% is required.

Since the Control Voltage (pin 5) is not used the comparator reference voltages will be 2/3 Vcc and 1/3 Vcc respectively. So the output of the 555 will set (goes high) when the capacitor voltage goes below 1/3 Vcc and output will reset (goes low) when the capacitor voltage goes above 2/3 Vcc.

### Working

When the circuit is switched ON, the capacitor (C) voltage will be less than 1/3 Vcc.

So the output of the lower comparator will be HIGH and of the higher comparator will be LOW. This SETs the output of the SR Flip-flop.

- □ Thus the discharging transistor will be OFF and the capacitor C starts charging from Vcc through resistor Ra & Rb.

- □ When the capacitor voltage will become greater than 1/3 Vcc (less than 2/3 Vcc), the output of both comparators will be LOW and the output of SR Flip-flop will be same as the previous condition.

Astable Multivibrator using 555 Timer – Working

- □ When the capacitor voltage will becomes slightly greater than 2/3 Vcc the output of the higher comparator will be HIGH and of lower comparator will be LOW. This resets the SR Flip-flop.

- Thus the discharging transistor turns ON and the capacitor starts discharging through resistor Rb.

- □ Soon the capacitor voltage will be less than 2/3 Vcc and output of both comparators will be LOW. So the output of the SR Flip-flop will be the previous state.

- □ So the discharging of capacitor continuous.

- □ When the capacitor voltage will become less than 1/3 Vcc, the output SETs since the output of lower comparator is HIGH and of higher comparator is LOW and the

### KARPAGAM ACADEMY OF HIGHER EDUCATION

CLASS: II MSc Physics

COURSE NAME: DIGITAL ELECTRONICS AN MICROPROCESSOR

COURSE CODE: 19PHP304

UNIT: II (Special Function IC's)

BATCH-2018-2020

capacitor starts charging again.

□ This process continuous and a rectangular wave will be obtained at the output.

### **Monostable Multivibrator**

A monostable multivibrator (MMV) is often called a pulse generator circuit in which the duration of the pulse is determined by the R-C network, connected externally to the 555 timer. Here one state of output is stable while the other is unstable to make stable state energy is stored by an externally connected capacitor C.

The time taken in storage determines the pulse width. The schematic of a 555 timer in monostable mode of operation is shown in the figure

as a Monostable Multivibrator

### Monostable Multivibrator Circuit details

Pin 1 is grounded. Trigger input is applied to pin 2. The input is kept at + VCC. To obtain transition of output from stable state to unstable state, a negative-going pulse and amplitude of greater than + 2/3 VCC is applied to pin 2. Output is taken from pin 3. Pin 4 is usually connected to + VCC Pin 5 is grounded through a 0.01 u F capacitor to avoid noise problem. Pin 6 (threshold) is shorted to pin 7. A resistor RA is connected between pins 6 and 8. At pins 7 a discharge capacitor is connected while pin 8 is connected to supply VCC.

### WORKING

When the output at pin 3 is low i.e. the circuit is in a stable state, the transistor is on and capacitor- C is shorted to ground. When a negative pulse is applied to pin 2, the trigger input falls below  $\pm 1/3$  VCC, the output of comparator goes high which resets the flip-flop and consequently the transistor turns off and the output at pin 3 goes high. This is the

### KARPAGAM ACADEMY OF HIGHER EDUCATION

# CLASS: II MSc PhysicsCOURSE NAME: DIGITAL ELECTRONICS AN MICROPROCESSORCOURSE CODE: 19PHP304UNIT: II (Special Function IC's)BATCH-2018-2020

transition of the output from stable to quasi-stable state, as shown in figure. As the discharge transistor is cut off, the capacitor C begins charging toward +VCC through resistance RA with a time constant equal to RAC. When the increasing capacitor voltage becomes slightly greater than +2/3 VCC, the output of comparator 1 goes high, which sets the flip-flop. The transistor goes to saturation, thereby discharging the capacitor C and the output of the timer goes low, as illustrated in figure.

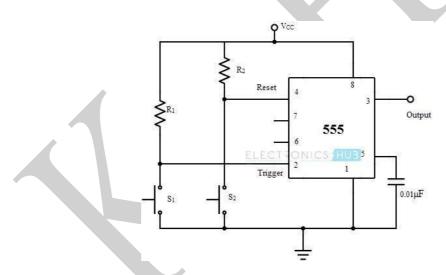

### **Bistable Multivibrator**

A Bistable multivibrator is a type of circuit which has two stable states (high and low). It stays in the same state until and unless an external trigger input is applied.

Generally, a bistable multivibrator stays low until a trigger signal is applied and it stays high until a reset signal is applied. Bistable multi vibrators are also called as flip-flops or latches. The term flip-flop is used because it 'flips' to one state and stays there until a trigger is applied and once the trigger is applied it 'flops' back to the original state.

The circuit for a bistable multivibrator using the 555 timer is shown below

A bistable multivibrator is one of the easiest circuits that can be built using a 555 timer. It doesn't require a capacitor as the RC charging unit is not responsible for the generation of the output. The generation of high and low outputs is not dependent on the charging and discharging of the capacitor in the RC unit but rather it is controlled by the external trigger and reset signals.

# CLASS: II MSc PhysicsCOURSE NAME: DIGITAL ELECTRONICS AN MICROPROCESSORCOURSE CODE: 19PHP304UNIT: II (Special Function IC's)BATCH-2018-2020

The explanation of the bi stable mode of operation of the 555 timer is as follows. The trigger and reset pins (pins 2 and 4 respectively) are connected to the supply through two resistors  $R_1$  and  $R_2$  so that they are always high. In all the previous cases, the reset pin is not used and in order to avoid any accidental reset, it is simply connected to VCC.

Two switches are connected between these pins and ground in order to make them go low momentarily. The switch at the trigger input will act as S (SET) input for the internal flipflop. The switch at the reset input will act as reset for the internal flip-flop.

When the switch  $S_1$  is pressed, the voltage from VCC will bypass the trigger terminal and is shorted to ground through the resistor  $R_1$ . Hence, the trigger pulse will momentarily go low and the output of the timer at pin 3 will become HIGH. The output stays HIGH because there is no input from the threshold pin (pin 6 is left open or better if connected to ground) and the output of the internal comparator (comparator 1) will not go high.

When the switch  $S_2$  is pressed, the voltage from VCC will bypass the reset terminal and is shorted to ground through the resistor  $R_2$ . This pin is internally connected to the RESET terminal of the flip-flop. When this signal goes low for a moment, the flip-flop receives the reset signal and RESETs the flip-flop.

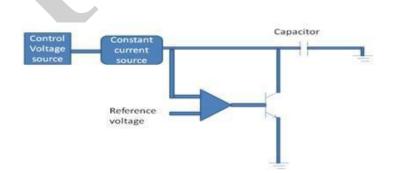

# **Voltage Controlled Oscillator**

A Voltage controlled oscillator is an oscillator with an output signal whose output can be varied over a range, which is controlled by the input DC voltage. It is an oscillator whose output frequency is directly related to the voltage at its input. The oscillation frequency varies from few hertz to hundreds of GHz. By varying the input DC voltage, the output frequency of the signal produced can be adjusted

### Working

### KARPAGAM ACADEMY OF HIGHER EDUCATION

CLASS: II MSc PhysicsCOURSE NAME: DIGITAL ELECTRONICS AN MICROPROCESSORCOURSE CODE: 19PHP304UNIT: II (Special Function IC's)BATCH-2018-2020

For a Voltage controlled oscillator generating a saw tooth waveform, the main component is the capacitor who's charging and discharging actually decides the formation of the output waveform. The input is given in form a voltage which can be controlled. This voltage is converted to a current signal and is applied to the capacitor. As the current passes through the capacitor, it starts charging and a voltage starts building across it. As the capacitor charges and the voltage across it increases gradually, the voltage is compared with a reference voltage using a comparator.

When the capacitor voltage exceeds the reference voltage, the comparator generates a high logic output which triggers the transistor and the capacitor is connected to ground and starts discharging. Thus the output waveform generated is the representation of the charging and discharging of the capacitor and the frequency is controlled by the input dc voltage.

### **Applications of VCO**

- □ Electronic jamming equipment.

- □ Function generator.

- □ Production of electronic music, for production of different types of noise.

- $\Box$  Phase locked loop.

- □ Frequency synthesizers, used in communication circuits.

# Voltage Controlled Oscillator (VCO – LM566)

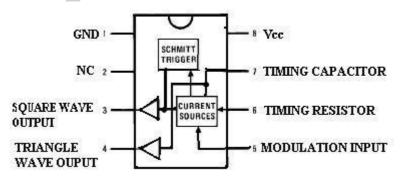

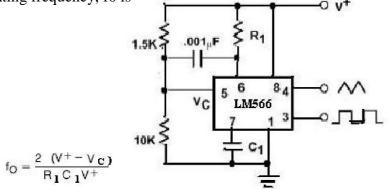

A practical example of a voltage controlled oscillator (VCO) is the LM566. The LM566 is a general purpose VCO which may be used to generate square wave and triangular waveforms as a function input voltage.

The LM566 is specified for operation over 0°C to 70°C temperature range. The frequency of which is a linear function of a controlling voltage. The frequency is also controlled by an external resistor and capacitor, whose values control the free running frequency.

| 3 of UGC Act, 1956 )                                 |                                                                    |                                   |

|------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------|

| CLASS: II MSc Physics COURS<br>COURSE CODE: 19PHP304 | E NAME: DIGITAL ELECTRONICS AN<br>UNIT: II (Special Function IC's) | MICROPROCESSOR<br>BATCH-2018-2020 |

| Pin Description:                                     |                                                                    |                                   |

| □ Pin 1: Ground (GND)                                |                                                                    |                                   |

| $\Box$ Pin 2: No connection (NC)                     |                                                                    |                                   |

| □ Pin 3: Square wave output                          |                                                                    |                                   |

| D Pin 4: Triangular wave output                      | ut                                                                 |                                   |

| D Pin 5: Modulation input                            |                                                                    |                                   |

| □ Pin 6: Timing resistor                             |                                                                    |                                   |

| □ Pin 7: Timing capacitor                            |                                                                    |                                   |

| D Pin 8: Vcc                                         |                                                                    |                                   |

| Applications:                                        |                                                                    |                                   |

| □ Function generator                                 |                                                                    |                                   |

| □ Tone generator                                     |                                                                    |                                   |

| □ FM modulation                                      |                                                                    |                                   |

| □ Frequency shift keying                             |                                                                    |                                   |

□ Clock generator

### Working of LM566:

Figure shows that the LM566 IC contains current sources to charge and discharge an external capacitor at a rate set by an external resistor R1 and the modulating dc input voltage V. A  $0.001\mu$ F capacitor is connected to pin 5 and pin 6. A Schmitt trigger circuit is used to switch the current sources between charging and discharging the capacitor and the triangular voltage produced across the capacitor and square wave from the Schmitt trigger are provided as outputs through buffer amplifiers. Both the output waveforms are buffered so that the output impedance of each is 50 f2. The typical magnitude of the triangular wave and the square wave are 2.4 V peak to peak and 5.4 V peak to peak. The free running or center-operating frequency, f0 is

# Phase Locked Loop

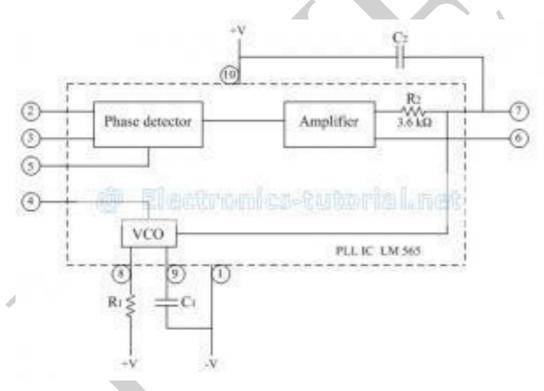

### PLL Ic 565 (Block Diagram And Pin Description)

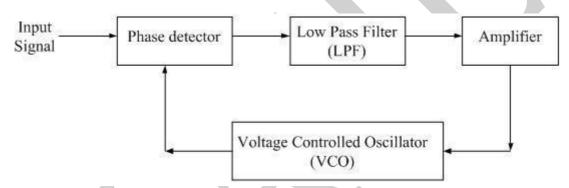

The Phase Locked Loop concept was first developed in 1930. Since then it is used in communication systems of different types, particularly in satellite communication system. Before the invention of IC PLL, systems were very complex and costly for use in most consumer & industrial systems. Now PLL ICs are fabricated at a very low cost. Therefore their use has become attractive for many applications such as FM demodulator, Stereo demodulators, Tone detectors, frequency synthesizers etc. Bellow figure shows the block diagram of PLL which consists of phase detector, LPF, error amplifier and Voltage controlled oscillator.

The phase detector block has two inputs, external signal and oscillator signal. Phase detector detects the phase between two signals and develops an output voltage proportional to phase difference. This block also called as phase detector or phase comparator. Output of phase detector is passed through a LPF. It removes high frequency signal and passes only low frequencies. This filter is also called as loop filter because the PLL system is a closed loop system. Output of filter is amplified by amplifier. This amplified output is applied as input for VCO. This input voltage adjusts the frequency of VCO such that the VCO frequency is equal to signal frequency i.e. VCO converts input voltage into frequency i.e. acts as voltage to frequency converter.

When the signal frequency and VCO frequency is same the loop gets locked. The loop gets locked by detecting the phase difference between two inputs so called Phase Locked Loop (PLL). Without application of any external signal, VCO has some frequency called as free running frequency or centre frequency. In this initial condition loop is not locked i.e. in open condition.

CLASS: II MSc PhysicsCOURSE NAME: DIGITAL ELECTRONICS AN MICROPROCESSORCOURSE CODE: 19PHP304UNIT: II (Special Function IC's)BATCH-2018-2020

When external signal is applied its frequency is either less or greater than VCO frequency so there is a phase difference between them. Phase detector detects the phase difference between two inputs and generates an error voltage. This is passed through LPF. After amplification it is given as a controlled voltage. This adjusts the frequency of VCO such that input frequency is equal to VCO frequency and forms locked condition. This process of locking the loop is called Capture effect.

The time required for VCO to adjust its frequency with signal frequency is called capture time. It depends on the internal parameters of system. There is some limit for input signal for which system can acquire a locked condition. This range of frequency between which the system can goes into locked condition is called capture range. This range is symmetrical about centre frequency. This capture range depends upon filter and amplifier characteristics.

If system acquires a locked condition then even if the signal frequency changes the loop remains in locked condition. The range of input frequency over which the locked condition maintained is called locked range. This also depends on amplifier and filter characteristics. Capture range is always less than lock range or almost equal; but capture range is never greater than locked range.

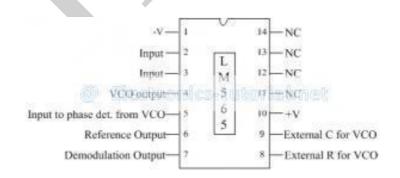

#### <u>PLL IC 565</u>

The PLL IC 565 is usable over the frequency range 0.1 Hz to 500 kHz. It has highly stable centre frequency and is able to achieve a very linear FM detection. The output of VCO is capable of producing TTL compatible square wave The dual supply is i n the range of  $\pm 6V$  to  $\pm 12V$ . The IC can also be operated from single supply in the range 12V to 24V. The following figure shows the pin-out and the internal block schematic of PLL IC LM 565.

It is a 14 pin IC, operated from a dual power supply +V (at pin no. 10) and -V (at pin no. 1).

CLASS: II MSc PhysicsCOURSE NAME: DIGITAL ELECTRONICS AN MICROPROCESSORCOURSE CODE: 19PHP304UNIT: II (Special Function IC's)BATCH-2018-2020

Pin 2 & 3 - Signal input for phase detector

Pin 4 - VCO output is available

Pin 4 & 5 - Shorted externally so that VCO output is applied for phase detection. In some

applications PLL loop is broken and some circuit is to be connected between pin no 4 and 5.

Pin 6 - Reference dc voltage is available

Pin 7 - Demodulated output. If input signal between pin no 2 and 3 is FM signal then at pin no 7 we get FM demodulation out put.

Pin 8 - Extern al R1 and C1 for VCO (determines free running frequency of VCO) Internal resistance R2 and external capacitor C2 forms a LPF. The value of internal resistance R2 is  $3.6k\Omega$ .

#### Features of IC 565:

- 1) Extreme stability of centre frequency typically 200ppm.

- 2) Wide range of operating vo ltage  $\pm 6V$  to  $\pm 12V$ .

- 3) Centre frequency of VCO is programmable by means of resistor, capacitor or voltage.

- 4) TTL compatible square wave output.

- 5) Highly linear triangular wave output available at pin no.9

- 6) Loop can be broken betwee n pin no.4 and 5 and external circuit can be added.

- 7) Frequency adjustable over the range 1:10 with single capacitor.

CLASS: II MSc Physics COURSE CODE: 19PHP304

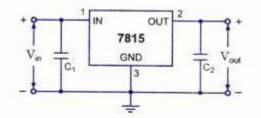

#### Fixed Voltage Regulator Ics 7800 And 7900 Series

#### Voltage Regulators using 78XX series IC

Connection of 7815 Voltage Regulator

7815 voltage regulator (15 volts Power Supply)

The series 7800 regulators provide eight voltage options, ranging from 5 to 24 V. These ICs are designed as fixed voltage regulators and with adequate heat sinking can deliver output currents in excess of 1 A. Although these devices do not require any external component, such components can be employed for providing adjustable voltages and currents. These ICs also have internal thermal overload protection and internal short-circuit current limiting. Figure illustrates how one such IC, a 7815, is connected to provide voltage regulation with output of + 15 V dc from this unit. An unregulated, input voltage V<sub>in</sub> is filtered by capacitor C, and connected to the pin .1 (IN terminal) of IC. The pin 2 (OUT terminal) of the IC provides a regulated + 15 V which is filtered by capacitor C<sub>2</sub> (mostly for any high frequency noise). The third pin (GND terminal) of the IC is connected to ground. While the input voltage may vary over some permissible voltage range, and the output load may vary over some acceptable range, the output voltage remains constant within specified voltage variation limits. These limitations are mentioned in the manufacturer's specification sheet. In addition, the difference between input and output voltages (V<sub>in</sub>- V<sub>out</sub>), called the

### CLASS: II MSc PhysicsCOURSE NAME: DIGITAL ELECTRONICS AN MICROPROCESSORCOURSE CODE: 19PHP304UNIT: II (Special Function IC's)BATCH-2018-2020

dropout voltage, must be typically 20 V, even during the low point on the input ripple voltage. Furthermore, the capacitor  $C_1$ , is required if the regulator is located an appreciable distance from a power supply filter. Even though  $C_2$  is not required, it may be used to improve the transient response of the regulator.

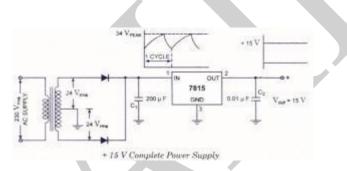

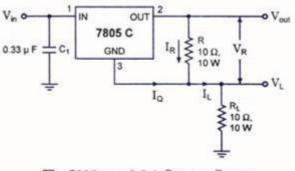

The 7805 as a 0.5 A Current Source

The connection of a 7815 in a complete supply is shown in figure. The ac line voltage is stepped down to 24  $V_{rms}$  across each half of the centre-tapped transformer. A full-wave rectifier and capacitor filter then provides an unregulated dc voltage with ac ripple of a few volts as input to the voltage regulator. The 7815 IC then provides an output of + 15 V dc.

The 7800 regulators can also be employed as current sources. A typical connection diagram of 7805 IC as a 0.5 A current source is depicted in figure.

The current supplied to the load is given as

$$\mathbf{IL} = \mathbf{V}_{\mathbf{R}} / \mathbf{R} + \mathbf{I}_{\mathbf{Q}}$$

when Iq is quiescent current in amperes (4.3 m A typically for the 7805 IC) In figure,  $V_R = V_{23} = 5$  V and R = 10 ohms

So

$$I_L = 5/10 = 0.5A$$

The output voltage with respect to ground is

$$\mathbf{V}_{out} = \mathbf{V}_{\mathbf{R}} + \mathbf{V}_{\mathbf{L}}$$

The load resistance,  $R_L = 10$  Ohms, therefore  $V_L = 5$  V

Thus

$$V_{out} = V_R + V_L = 5 + 5 = 10$$

V Minimum input voltage required,

$$V_{in} = V_{out} + dropout \ voltage = 10 + 2 = 12V$$

**Specifications.** The specification sheet of fixed positive voltage regulators of 7800 series is given below. Some considerations of a few of the more important parameters should be considered.

#### **Absolute Maximum Ratings**

Input voltage: 40 V

Continuous total power dissipation: 2 W

Operating free-air temperature range : -65 to  $150^{\circ}$  C

#### **Output Voltage**.

The specification for the 7812 indicates that its nominal output voltage is 12 V but could be as low as 11.5 V or as high as 12.5 V.

#### Input or Line Regulation.

The input or line regulation is seen to be typically 3 mV, to a maximum of 120 mV.

#### **Output or Load Regulation**.

The output or load regulation is seen to be typically 4 mV to a maximum of 100 mV (for output currents from 0.25 to 0.75 A). It means that the output voltage can typically vary only 4 mV from the rated 12 V dc.

#### Short-circuit Output Current.

The amount of current is limited to 350 m A if the output were to be short-circuited (may be by accident or by another faulty component). Peak Output Current. The typical peak output current that might be drawn from the supply is 2.2 A against rated maximum current of 1.5 A. It indicates that though the IC is rated as capable of providing 1.5 A, but somewhat more current can be drawn (possibly for a short duration of time).

#### Drop out Voltage.

The dropout voltage, typically 2 V, is the minimum amount of voltage across the input-output terminals that is required to be maintained if the IC is to operate as a regulator. In case the input voltage falls too low or the output rises so that at least 2 V is not maintained across the input-output terminals of IC, the IC will no longer provide voltage regulation. So input voltage is maintained large enough to ensure that the dropout voltage is provided.

#### **VOLTAGE REGULATOR IC 723**

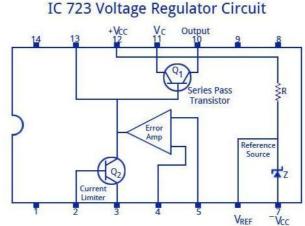

The functional diagram of the voltage regulator is shown below. It consists of a voltage reference source (Pin 6), an error amplifier with its inverting input on pin 4 and non-inverting input on pin 5, a series pass transistor (pins 10 and 11), and a current limiting transistor on pins 2 and 3. The device can be set to work as both posistive and negaive voltage regulators with an output voltage ranging from 2 V to 37 V, and output current levels upto 150 m A. The maximum supply voltage is 40 V, and the line and load regulations are each specified as 0.01%.

The 723 Voltage Regulator IC. The functional diagram of the voltage regulator isPrepared by Mr. J. THIRUPATHY, Asst Prof, Department of Physics, KAHE16/19

CLASS: II MSc PhysicsCOURSE NAME: DIGITAL ELECTRONICS AN MICROPROCESSORCOURSE CODE: 19PHP304UNIT: II (Special Function IC's)BATCH-2018-2020

shown below. It consists of a voltage reference source (Pin 6), an error amplifier with its inverting input on pin 4 and non-inverting input on pin 5, a series pass transistor (pins 10 and 11), and a current limiting transistor on pins 2 and 3. The device can be set to work as both posistive and negaive voltage regulators with an output voltage ranging from 2 V to 37 V, and output current levels upto 150 m A. The maximum supply voltage is 40 V, and the line and load regulations are each specified as 0.01%.

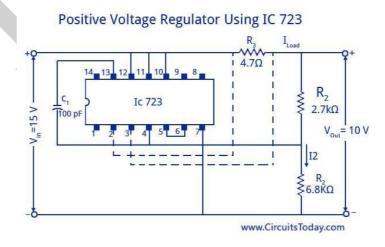

The figure shown below is a positive voltage regulator with an IC 723. The output voltage can be set to any desired positive voltage between (7-37) volts. 7 volts is the reference starting voltage. All these variations are brought with the change of values in resistors R1 and R2 with the help of a potentiometer. A darlington connection is made by the transistor to Q1 to handle large load current. The broken lines in the image indicate the internal connections for current limiting. Even feedback current limiting is possible in this IC. A regulator output voltage less than the 7 V reference level can be obtained by using a voltage divider across the reference source. The potentially divided reference voltage is then connected to terminal 5.

Prepared by Mr. J. THIRUPATHY, Asst Prof, Department of Physics, KAHE

CLASS: II MSc Physics COURSE CODE: 19PHP304

Positive Voltage Regulator Using IC 723

The IC is provided with voltage at the lowest point on the ripple waveform, should be at least 3 V greater than the output of the regulator and greater than  $V_{ref}$ . If it is not so a high-amplitude output ripple is possible to occur.

#### **Possible Questions**

#### 2 Marks

- 1. What are the applications of IC 555?

- 2. Draw the pin diagram of IC 566.

- 3. Give the pin configuration of IC 555.

- 4. Draw the circuit of astable multivibrator.

- 5. Draw the circuit of a monostable multivibrator.

#### 8 Marks

- 1) Explain the pin diagram of IC 555 timer.

- 2) Explain the operation of IC 566 with the help of block diagram.

- 3) Explain the block diagram of IC 555 timer.

- 4) Explain the pin configuration of IC 565.

- 5) Draw the circuit of a bistable multivibrator using 555 timer and explain its working.

- 6) Draw the circuit of a astable multivibrator using 555 timer and explain its working.

- 7) Explain fixed voltage regulator IC 7800

- 8) Draw the circuit of a monostable multivibrator using 555 timer and explain its working.

- 9) Discuss about phase locked loop.

- 10) Draw the circuit diagram of an astable multivibrator to generate the output signal with frequency of 1kHz and the duty cycle of 75%.

- 11) Design a timer, which should turn ON heater immediately after pressing a push button and should hold heater in ON-state for 5 seconds.

CLASS: II MSc Physics COURSE CODE: 19PHP304 COURSE NAME: DIGITAL ELECTRONICS AND MICROPROCESSOR UNIT: III (MICROPROCESSOR) BATCH-2018-2020

#### UNIT-3

**Microprocessor:** Microprocessor Architecture, Pin out configuration of 8085-bus organization and timings –address bus, data bus, multiplexing address/data bus and control and status signal, Interrupts: maskable and non-maskable interrupt (concept),8085 interrupt.

### CLASS: II MSc Physics<br/>COURSE CODE: 19PHP304COURSE NAME: DIGITAL ELECTRONICS AND MICROPROCESSOR<br/>UNIT: III (MICROPROCESSOR)MICROPROCESSOR<br/>BATCH-2018-2020

#### **MICROPROCESSOR:**

8085 is pronounced as "eighty- eighty-five" microprocessor. It is an 8-bit microprocessor

designed by Intel in 1977 using NMOS technology.

It has the following configuration -

- 8-bit data bus

- 16-bit address bus, which can address upto 64KB

- A 16-bit program counter

- A 16-bit stack pointer

- Six 8-bit registers arrange d in pairs: BC, DE, HL

- Requires +5V supply to operate at 3.2 MHZ single phase

clock It is used in washing machines, microwave ovens, mobile

phones, etc.

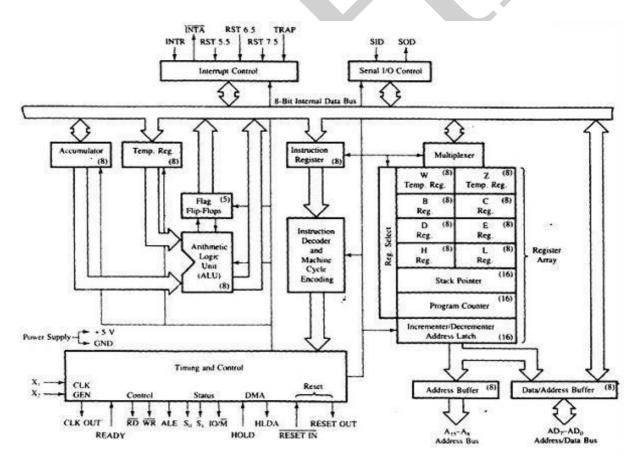

#### **MICROPROCESSOR ARCHITE CTURE,**

The architecture of 8085 with this following image -

CLASS: II MSc Physics<br/>COURSE CODE: 19PHP304COURSE NAME: DIGITAL ELECTRONICS AND MICROPROCESSOR<br/>UNIT: III (MICROPROCESSOR)MICROPROCESSOR<br/>BATCH-2018-2020

| X <sub>1</sub>  | 1  | 40 | VCC               |

|-----------------|----|----|-------------------|

| X, [            | 2  | 39 | HOLD              |

| RST OUT         | 3  | 38 | HLDA              |

| SOD 🗆           | 4  | 37 | CLK OUT           |

| SID 🗆           | 5  | 36 | RST IN            |

| TRAP            | 6  | 35 | READY             |

| RST7.5          | 7  | 34 | IO/M              |

| RST6.5          | 8  | 33 | S1                |

| RST5.5          | 9  | 32 | RD                |

| INTR 🗆          | 10 | 31 | WR                |

| INTA 🗆          | 11 | 30 | ALE               |

| AD <sub>o</sub> | 12 | 29 | S <sub>o</sub>    |

| AD <sub>1</sub> | 13 | 28 | ] A <sub>15</sub> |

| AD <sub>2</sub> | 14 | 27 | A14               |