Semester - I

4H-4C

## COMPUTER SYSTEM ARCHITECTURE

17CSU102

Instruction Hours / week; L: 4 T: 0 P: 0 Marks; Int: 40 Ext: 60

60 Total: 100

### SCOPE

Computer System Architecture deals with the architecture of computer systems with its various processing units and also the performance measurement of the computer system. This course is designed to provide a comprehensive introduction to digital logic design leading to the ability to understand number system representations, binary codes, binary arithmetic and Boolean algebra, and its relevance to digital logic design.

### OBJECTIVE

- To enable the students to gain knowledge on the architecture of modern computer.

- To understand how computer stores positive and negative numbers and to perform arithmetic operation of positive and negative numbers.

- To learn Cache memory and its importance

### UNIT -I Introduction

Logic gates, Boolean algebra, circuit simplification, combinational circuits: Adders and Subtractors –Multiplexers and De multiplexers – Encoders and Decoders-sequential circuits: Flip Flop's, registers, counters and memory units.

# UNIT -II Data Representation and Basic Computer Arithmetic

Number systems, complements, fixed and floating point representation, character representation, addition, subtraction, magnitude comparison, multiplication and division algorithms for integers

## UNIT -III Basic Computer Organization and Design

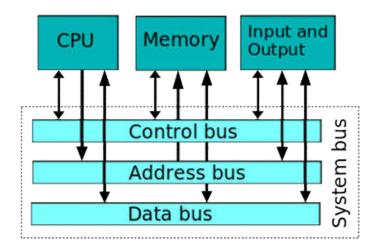

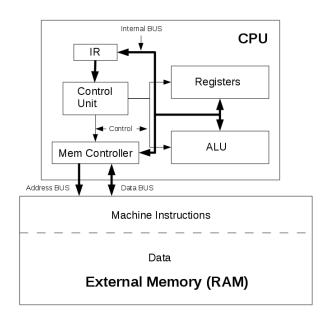

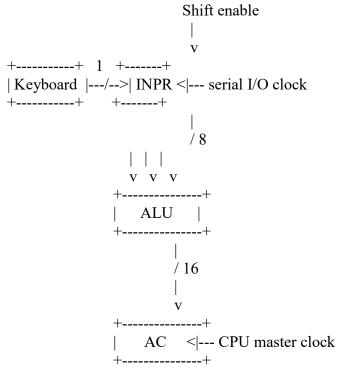

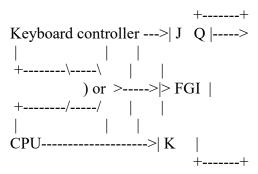

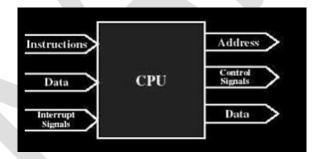

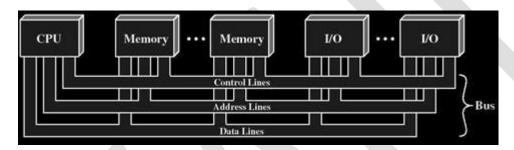

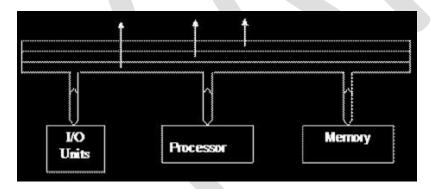

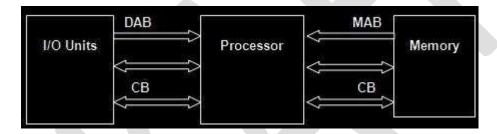

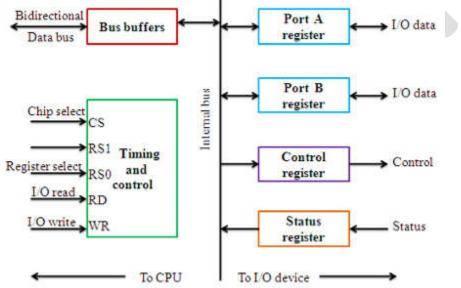

Computer registers, bus system, instruction set, timing and control, instruction eycle, memory reference, input-output and interrupt, Interconnection Structures, Bus Interconnection design of basic computer.

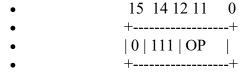

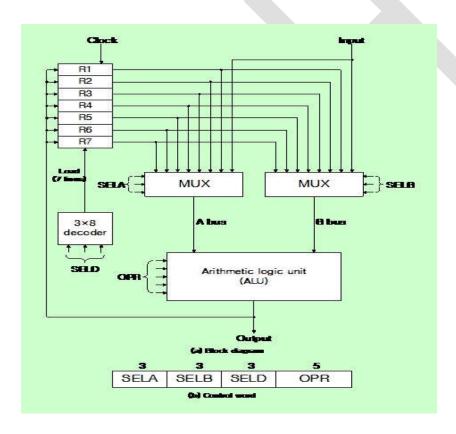

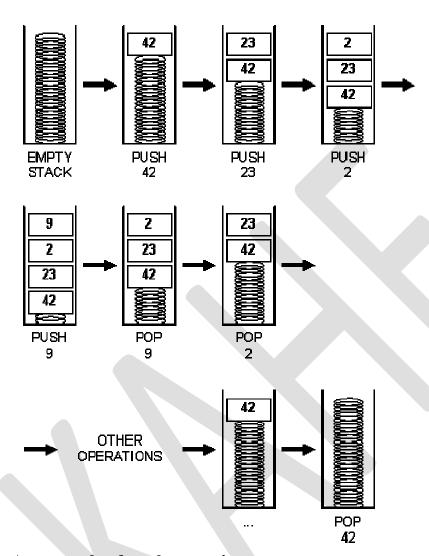

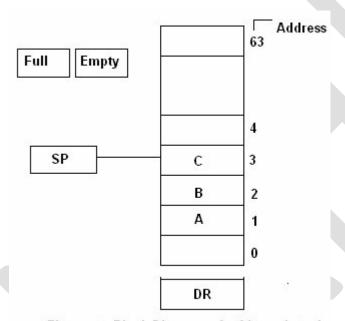

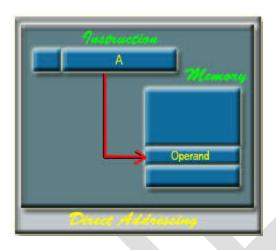

### UNIT-IV Central Processing Unit

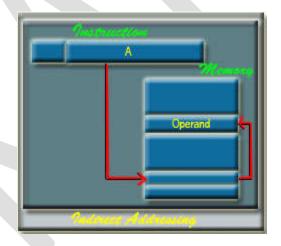

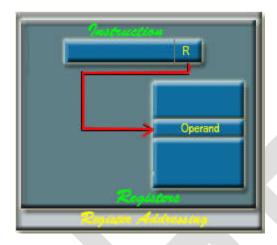

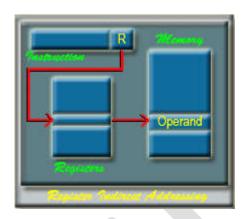

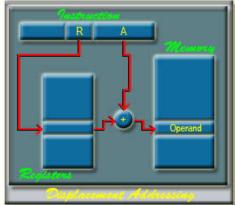

Register organization, arithmetic and logical micro-operations, stack organization, micro programmed control. Instruction formats, addressing modes, instruction codes, machine language, assembly language, input output programming, RISC, CISC architectures, pipelining and parallel architecture.

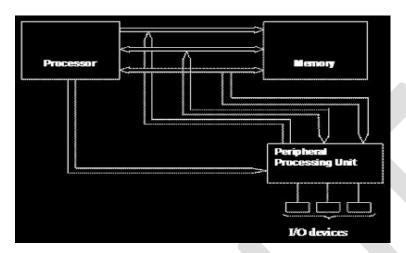

## UNIT -V Memory and Input-Output Organization

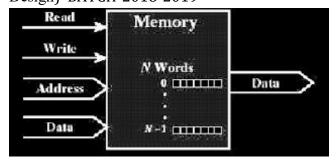

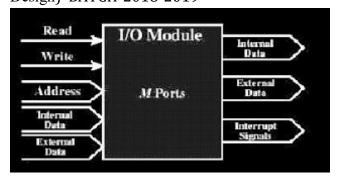

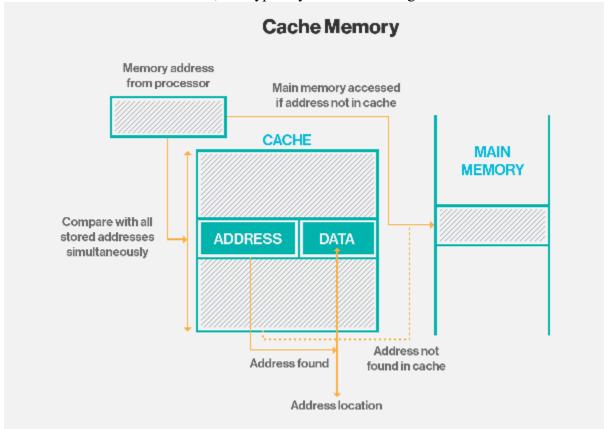

Cache memory, Associative memory, mapping Input / Output: External Devices, I/O Modules , Programmed I/O, Interrupt-Driven I/O, Direct Memory Access, I/O Channels. Suggested Readings:

- 1. Dos'Reis, A. J. (2009). Assembly Language and Computer Architecture using C++

- and JAVA. Course Technology

2. Stallings, W. (2010). Computer Organization and Architecture Designing for

- Performance (8th ed.) New Delhi: Prentice Hall of India, 3. Mano, M.M. (2013). Digital Design, New Delhi: Pearson Education Asia.

- 4. Carl Hamacher. (2012). Computer Organization (5th ed.), New Delhi: McGrawHill.

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

### **UNIT I**

Introduction: Logic Gates -Boolean Algebra-Circuit Simplification-Combinational Circuits-Adders and Subtractor-Multiplexers and De-multiplexers-Encoders and Decoders-Sequential Circuits-Flip-Flops, registers-Counters and memory units.

### **Basic Gates**

Boolean functions may be practically implemented by using electronic gates. The following points are important to understand.

- Electronic gates require a power supply.

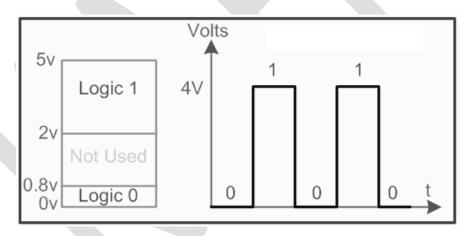

- Gate **INPUTS** are driven by voltages having two nominal values, e.g. 0V and 5V representing logic 0 and logic 1 respectively.

- The **OUTPUT** of a gate provides two nominal values of voltage only, e.g. 0V and 5V representing logic 0 and logic 1 respectively. In general, there is only one output to a logic gate except in some special cases.

- There is always a time delay between an input being applied and the output responding.

### **Truth Tables**

Truth tables are used to help show the function of a logic gate. If you are unsure about truth tables and need guidance on how go about drawing them for individual gates or logic circuits then use the truth table section link.

### Logic gates

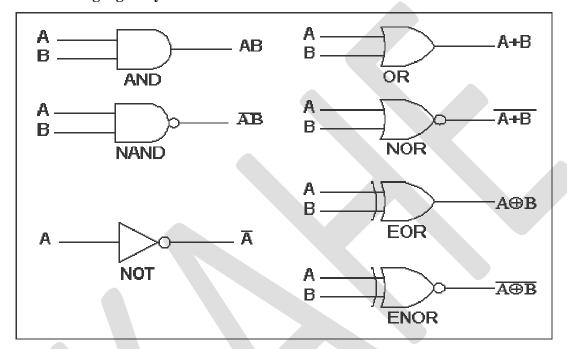

Digital systems are said to be constructed by using logic gates. These gates are the AND, OR, NOT, NAND, NOR, EXOR and EXNOR gates. The basic operations are described below with the aid of truth tables.

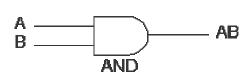

### AND gate

| 2 Input AND gate |   |     |  |  |  |

|------------------|---|-----|--|--|--|

| Α                | В | A.B |  |  |  |

| 0                | 0 | 0   |  |  |  |

| 0                | 1 | 0   |  |  |  |

| 1                | 0 | 0   |  |  |  |

| 1                | 1 | 1   |  |  |  |

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

The AND gate is an electronic circuit that gives a **high** output (1) only if **all** its inputs are high. A dot (.) is used to show the AND operation i.e. A.B. Bear in mind that this dot is sometimes omitted i.e. AB

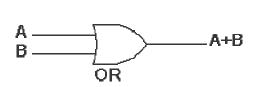

### OR gate

| 2 Input OR gate |   |     |  |  |

|-----------------|---|-----|--|--|

| Α               | В | A+B |  |  |

| 0               | 0 | 0   |  |  |

| 0               | 1 | 1   |  |  |

| 1               | 0 | 1   |  |  |

| 1               | 1 | 1   |  |  |

The OR gate is an electronic circuit that gives a high output (1) if **one or more** of its inputs are high. A plus (+) is used to show the OR operation.

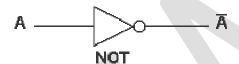

### NOT gate

| NOT ( | gate |

|-------|------|

| Α     | Ā    |

| 0     | 1    |

| 1     | 0    |

The NOT gate is an electronic circuit that produces an inverted version of the input at its output. It is also known as an *inverter*. If the input variable is A, the inverted output is known as NOT A. This is also shown as A', or A with a bar over the top, as shown at the outputs

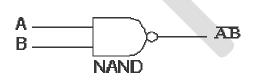

### NAND gate

| 2 Input NAND gate |   |   |  |  |

|-------------------|---|---|--|--|

| A B A.B           |   |   |  |  |

| 0                 | 0 | 1 |  |  |

| 0                 | 1 | 1 |  |  |

| 1                 | 0 | 1 |  |  |

| 1                 | 1 | 0 |  |  |

This is a NOT-AND gate which is equal to an AND gate followed by a NOT gate. The outputs of all NAND gates are high if **any** of the inputs are low. The symbol is an AND gate with a small circle on the output. The small circle represents inversion.

Department of ECS Prepared by Dr. A.SanjayGandhi, Assitant Prof., KAHE Page 2/45

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

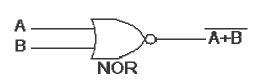

### NOR gate

| 2 Input NOR gate |   |                |  |  |

|------------------|---|----------------|--|--|

| Α                | В | <del>A+B</del> |  |  |

| 0                | 0 | 1              |  |  |

| 0                | 1 | 0              |  |  |

| 1                | 0 | 0              |  |  |

| 1                | 1 | 0              |  |  |

This is a NOT-OR gate which is equal to an OR gate followed by a NOT gate. The outputs of all NOR gates are low if **any** of the inputs are high. The symbol is an OR gate with a small circle on the output. The small circle represents inversion.

### **EXOR** gate

| 2 Input EXOR gate |   |     |  |  |  |

|-------------------|---|-----|--|--|--|

| Α                 | В | A⊕B |  |  |  |

| 0                 | 0 | 0   |  |  |  |

| 0                 | 1 | 1   |  |  |  |

| 1                 | 0 | 1   |  |  |  |

| 1                 | 1 | 0   |  |  |  |

The 'Exclusive-OR' gate is a circuit which will give a high output if either, but not both, of its two inputs are high. An encircled plus sign  $(\oplus)$  is used to show the EOR operation.

### **EXNOR** gate

| 2 Input EXNOR gate |   |   |  |  |

|--------------------|---|---|--|--|

| A B <del>A⊕B</del> |   |   |  |  |

| 0                  | 0 | 1 |  |  |

| 0                  | 1 | 0 |  |  |

| 1                  | 0 | 0 |  |  |

| 1                  | 1 | 1 |  |  |

The 'Exclusive-NOR' gate circuit does the opposite to the EOR gate. It will give a low output if either, but not both, of its two inputs are high. The symbol is an EXOR gate with a small circle on the output. The small circle represents inversion.

The NAND and NOR gates are called *universal functions* since with either one the AND and OR functions and NOT can be generated.

Department of ECS Prepared by Dr. A.SanjayGandhi, Assitant Prof., KAHE Page 3/45

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

### Note:

A function in *sum of products* form can be implemented using NAND gates by replacing all AND and OR gates by NAND gates. A function in *product of sums* form can be implemented using NOR gates by replacing all AND and OR gates by NOR gates.

Table 1: Logic gate symbols

Table 2 is a summary truth table of the input/output combinations for the NOT gate together with all possible input/output combinations for the other gate functions. Also note that a truth table with 'n' inputs has 2<sup>n</sup> rows. You can compare the outputs of different gates.

Table 2: Logic gates representation using the Truth table

|         |      | INPU | JTS  |    | OUTPUTS |      |       |   |   |

|---------|------|------|------|----|---------|------|-------|---|---|

| A B AND |      |      | NAND | OR | NOR     | EXOR | EXNOR |   |   |

| NOT     | gate | 0    | 0    | 0  | 1       | 0    | 1     | 0 | 1 |

| Α       | Ā    | 0    | 1    | 0  | 1       | 1    | 0     | 1 | 0 |

| 0       | 1    | 1    | 0    | 0  | 1       | 1    | 0     | 1 | 0 |

| 1       | 0    | 1    | 1    | 1  | 0       | 1    | 0     | 0 | 1 |

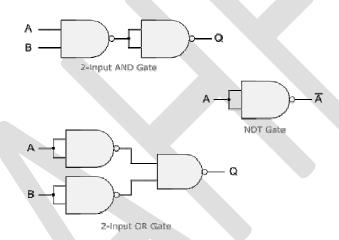

The "Universal" NAND Gate

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

The **Logic NAND** Gate is generally classed as a "Universal" gate because it is one of the most commonly used logic gate types. NAND gates can also be used to produce any other type of logic gate function, and in practice the NAND gate forms the basis of most practical logic circuits. By connecting them together in various combinations the three basic gate types of AND, OR and NOT function can be formed using only NAND's, for example.

### **Various Logic Gates using only NAND Gates**

As well as the three common types above, Ex-Or, Ex-Nor and standard NOR gates can be formed using just individual NAND gates.

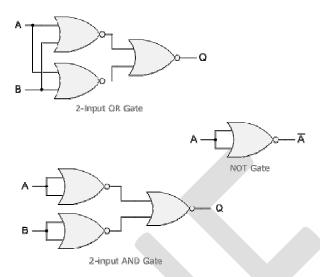

### The "Universal" NOR Gate

Like the NAND gate seen in the last section, the NOR gate can also be classed as a "Universal" type gate. NOR gates can be used to produce any other type of logic gate function just like the NAND gate and by connecting them together in various combinations the three basic gate types of AND, OR and NOT function can be formed using only NOR's, for example.

### **Various Logic Gates using only NOR Gates**

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

As well as the three common types above, Ex-Or, Ex-Nor and standard NOR gates can also be formed using just individual NOR gates.

### **Boolean arithmetic**

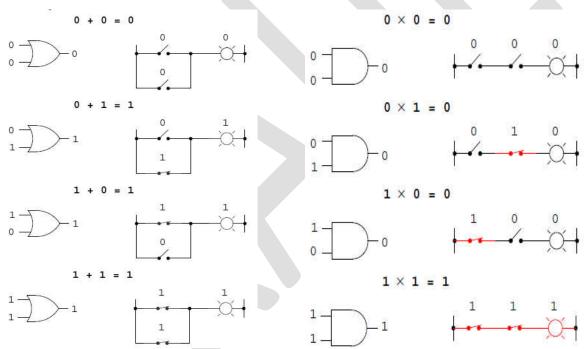

Let us begin our exploration of Boolean algebra by adding numbers together:

$$0 + 0 = 0$$

$0 + 1 = 1$

$1 + 0 = 1$

$1 + 1 = 1$

The first three sums make perfect sense to anyone familiar with elementary addition. The last sum, though, is quite possibly responsible for more confusion than any other single statement in digital electronics, because it seems to run contrary to the basic principles of mathematics. Well, it *does* contradict principles of addition for real numbers, but not for Boolean numbers. Remember that in the world of Boolean algebra, there are only two possible values for any quantity and for any arithmetic operation: 1 or 0. There is no such thing as "2" within the scope of Boolean values. Since the sum"1 + 1" certainly isn't 0, it must be 1 by process of elimination.

It does not matter how many or few terms we add together, either. Consider the following sums:

$$0+1+1=1$$

$$0+1+1+1=1$$

Department of ECS Prepared by Dr. A.SanjayGandhi, Assitant Prof., KAHE Page 6/45

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

$$1 + 0 + 1 + 1 + 1 = 1$$

$1 + 1 + 1 = 1$

Take a close look at the two-term sums in the first set of equations. Does that pattern look familiar to you? It should! It is the same pattern of 1's and 0's as seen in the truth table for an

OR gate. In other words, Boolean addition corresponds to the logical function of an"OR" gate, as well as to parallel switch contacts:

There is no such thing as subtraction in the realm of Boolean mathematics. Subtraction implies the existence of negative numbers: 5 - 3 is the same thing as 5 + (-3), and in Boolean algebra negative quantities are forbidden. There is no such thing as division in Boolean mathematics, either, since division is really nothing more than compounded subtraction, in the same way that multiplication is compounded addition.

Multiplication is valid in Boolean algebra, and thankfully it is the same as in real-number algebra: anything multiplied by 0 is 0, and anything multiplied by 1 remains unchanged:

$$0 \times 0 = 0$$

$$0 \times 1 = 0$$

$1 \times 0 = 0$

Department of ECS Prepared by Dr. A.SanjayGandhi, Assitant Prof, , KAHE

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

$$1 \times 1 = 1$$

This set of equations should also look familiar to you: t is the same pattern found in the truth table for an AND gate. In other words, Boolean multiplication corresponds to the logical function of an"AND" gate, as well as to series switch contacts:

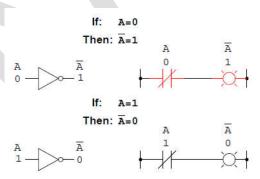

Like"normal" algebra, Boolean algebra uses alphabetical letters to denote variables. Unlike "normal" algebra, though, Boolean variables are always CAPITAL letters, never lowercase. Because they are allowed to possess only one of two possible values, either 1 or 0, each and every variable has a *complement*: the opposite of its value. For example, if variable"A" has a value of 0, and then the complement of A has a value of 1. Boolean notation uses a bar above the variable character to denote complementation, like this:

If: A=0, Then: A=1

If: A=1 Then: A=0

In written form, the complement of "A" denoted as "A-not" or "A-bar". Sometimes a" prime" symbol is used to represent complementation. For example, A' would be the complement of A, much the same as using a prime symbol to denote differentiation in calculus rather than the fractional notation d/dt. Usually, though, the "bar" symbol finds more widespread use than the "prime" symbol, for reasons that will become more apparent later in this chapter.

Boolean complementation finds equivalency in the form of the NOT gate, or a normally closed switch or relay contact:

Department of ECS Prepared by Dr. A.SanjayGandhi, Assitant Prof, , KAHE

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

The basic definition of Boolean quantities has led to the simple rules of addition and multiplication, and has excluded both subtraction and division as valid arithmetic operations. We have a symbology for denoting Boolean variables, and their complements.

### • REVIEW:

- Boolean addition is equivalent to the OR logic function, as well as parallel switch contacts.

- Boolean multiplication is equivalent to the *AND* logic function, as well as *series* switch contacts.

- Boolean complementation is equivalent to the *NOT* logic function, as well as *normally closed* relay contacts.

### **Basic Laws**

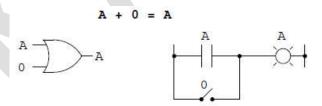

In mathematics, an *identity* is a statement true for all possible values of its variable or variables. The algebraic identity of x + 0 = x tells us that anything (x) added to zero equals the original "anything," no matter what value that "anything" (x) may be. Like ordinary algebra, Boolean algebra has its own unique identities based on the bivalent states of Boolean variables. The first Boolean identity is that the sum of anything and zero is the same as the original anything." This identity is no different from its real-number algebraic equivalent:

No matter what the value of A, the output will always be the same: when A=1, the output will also be 1; when A=0, the output will also be 0.

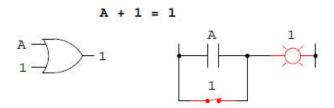

The next identity is most definitely *different* from any seen in normal algebra. Here we discover that the sum of anything and one is one:

Department of ECS Prepared by Dr. A.SanjayGandhi, Assitant Prof, , KAHE Page 9/45

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

No matter what the value of A, the sum of A and 1 will always be 1. In a sense, the"1" signal *overrides* the effect of A on the logic circuit, leaving the output fixed at a logic level of 1. Next, we examine the effect of adding A and A together, which is the same as connecting both inputs of an OR gate to each other and activating them with the same signal:

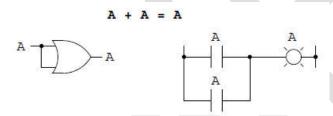

In real-number algebra, the sum of two identical variables is twice the original variable's value (x + x = 2x), but remember that there is no concept of'2" in the world of Boolean math, only 1 and 0, so we cannot say that A + A = 2A. Thus, when we add a Boolean quantity to itself, the sum is equal to the original quantity: 0 + 0 = 0, and 1 + 1 = 1.

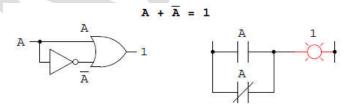

Introducing the uniquely Boolean concept of complementation into an additive identity, we find an interesting effect. Since there must be one"1" value between any variable and its complement, and since the sum of any Boolean quantity and 1 is 1, the sum of a variable and Its complement must be 1:

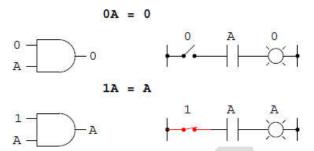

Just as there are four Boolean additive identities (A+0, A+1, A+A, and A+A'), so there are also four multiplicative identities: Ax0, Ax1, AxA, and AxA'. Of these, the first two are no different from their equivalent expressions in regular algebra:

Department of ECS Prepared by Dr. A.SanjayGandhi, Assitant Prof, , KAHE Page 10/45

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

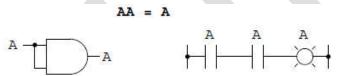

The third multiplicative identity expresses the result of a Boolean quantity multiplied by itself. In normal algebra, the product of a variable and itself is the *square* of that variable (3 x 3 = 32 = 9). However, the concept of 'square' implies a quantity of 2, which has no meaning in Boolean algebra, so we cannot say that A x A = A2. Instead, we find that the product of a Boolean quantity and itself is the original quantity, since 0 x 0 = 0 and 1 x 1 = 1:

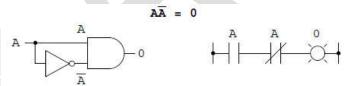

The fourth multiplicative identity has no equivalent in regular algebra because it uses the complement of a variable, a concept unique to Boolean mathematics. Since there must be one "0" value between any variable and its complement, and since the product of any Boolean quantity and 0 is 0, the product of a variable and its complement must be 0:

To summarize, then, we have four basic Boolean identities for addition and four for multiplication:

Additive

$$A + 0 = A$$

$$A + 1 = 1$$

$$A + A = A$$

$$A + A = 1$$

Department of ECS Prepared by Dr. A.SanjayGandhi, Assitant Prof, , KAHE

CLASS: I B.Sc., CS, IT, CA& CT COURSE NAME: Computer Systems Architecture

COURSECODE: 18CSU102 UNIT:I (Logic Gates) BATCH-2018-2019

Multiplicative

$$0A = 0$$

$$1A = A$$

$$AA = A$$

$$AA = 0$$

### Basic Boolean algebraic identities

Another identity having to do with complementation is that of the *double complement*: a variable inverted twice. Complementing a variable twice (or any even number of times) results in the original Boolean value. This is analogous to negating (multiplying by -1) in real-number algebra: an even number of negations cancel to leave the original value:

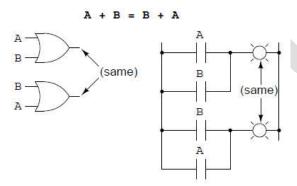

Commutative property of addition

### **Boolean algebraic properties**

Another type of mathematical identity, called a "property" or a "law," describes how differing variables relate to each other in a system of numbers. One of these properties is known as the *commutative property*, and it applies equally to addition and multiplication. In essence, the commutative property tells us we can reverse the order of variables that are either added together or multiplied together without changing the truth of the expression:

Department of ECS Prepared by Dr. A.SanjayGandhi, Assitant Prof, , KAHE

Page 12/45

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

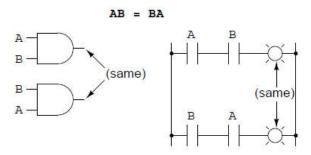

### Commutative property of multiplication

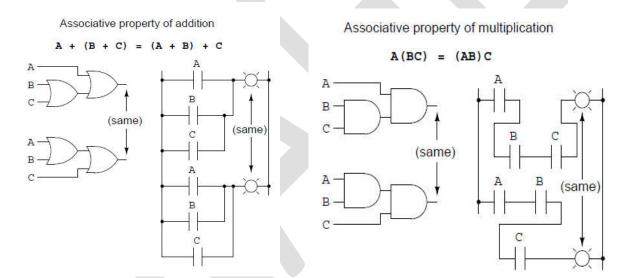

Along with the commutative properties of addition and multiplication, we have the *associative property*, again applying equally well to addition and multiplication. This property tells us we can associate groups of added or multiplied variables together with parentheses without altering the truth of the equations.

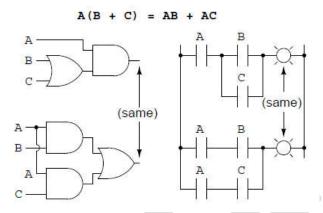

Lastly, we have the *distributive property*, illustrating how to expand a Boolean expression formed by the product of a sum, and in reverse shows us how terms may be factored out of Boolean sums-of-products:

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

### Distributive property

To summarize, here are the three basic properties: commutative, associative, and distributive. Basic Boolean algebraic properties

$$A(B+C) = AB + AC$$

Additive

$$A + (B + C) = (A + B) + C$$

$$A + B = B + A$$

Multiplicative

$$A(BC) = (AB)C$$

$$AB = BA$$

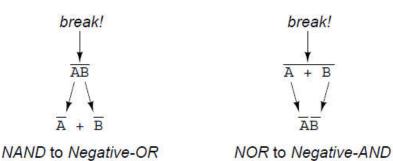

### **DeMorgan's Theorems**

A mathematician named DeMorgan developed a pair of important rules regarding group complementation in Boolean algebra. By *group* complementation, I'm referring to the complement of a group of terms, represented by a long bar over more than one variable. You should recall from the chapter on logic gates that inverting all inputs to a gate reverses that gate's essential function from AND to OR, or vice versa, and also inverts the output. So, an OR gate with all inputs inverted (a Negative-OR gate) behaves the same as a NAND gate, and an AND gate with all inputs inverted (a Negative-AND gate) behaves the same as a NOR Department of ECS Prepared by Dr. A.SanjayGandhi, Assitant Prof., KAHE Page 14/45

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

gate. DeMorgan's theorems state the same equivalence in "backward" form: that inverting the output of any gate results in the same function as the opposite type of gate (AND vs. OR) with inverted inputs:

$$A = \overline{AB}$$

$$AB =$$

$$\overline{AB} = \overline{A} + \overline{B}$$

A long bar extending over the term AB acts as a grouping symbol, and as such is entirely different from the product of A and B independently inverted. In other words, (AB)' is not equal to A'B'. Because the "prime" symbol (') cannot be stretched over two variables like a bar can, we are forced to use parentheses to make it apply to the whole term AB in the previous sentence. A bar, however, acts as its own grouping symbol when stretched over more than one variable. This has profound impact on how Boolean expressions are evaluated and reduced, as we shall see.

DeMorgan's theorem may be thought of in terms of *breaking* a long bar symbol. When a long bar is broken, the operation directly underneath the break changes from addition to multiplication, or vice versa, and the broken bar pieces remain over the individual variables. To illustrate:

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

### DeMorgan's Theorems

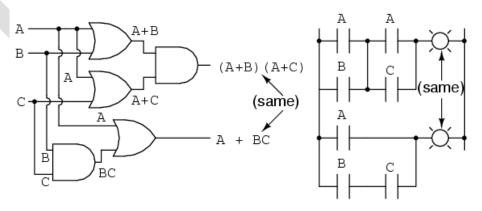

Boolean algebra finds its most practical use in the simplification of logic circuits. If we translate a logic circuit's function into symbolic (Boolean) form, and apply certain algebraic rules to the resulting equation to reduce the number of terms and/or arithmetic operations, the simplified equation may be translated back into circuit form for a logic circuit performing the same function with fewer components. If equivalent function may be achieved with fewer components, the result will be increased reliability and decreased cost of manufacture.

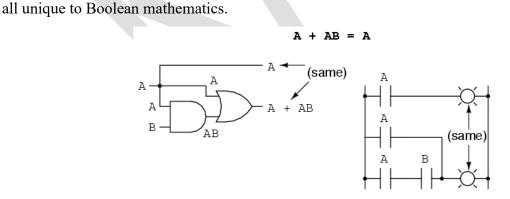

To this end, there are several rules of Boolean algebra presented in this section for use in reducing expressions to their simplest forms. The identities and properties already reviewed in this chapter are very useful in Boolean simplification, and for the most part bear similarity to many identities and properties of "normal" algebra. However, the rules shown in this section are

Department of ECS Prepared by Dr. A.SanjayGandhi, Assitant Prof, , KAHE

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

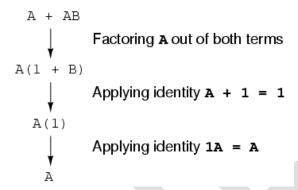

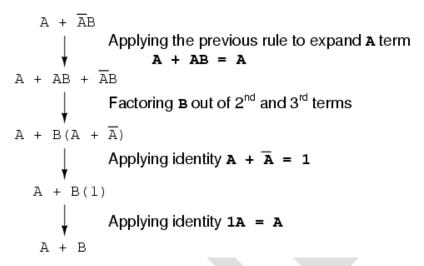

This rule may be proven symbolically by factoring an "A" out of the two terms, then applying the rules of A + 1 = 1 and 1A = A to achieve the final result:

Please note how the rule A + 1 = 1 was used to reduce the (B + 1) term to 1. When a rule like "A + 1 = 1" is expressed using the letter "A", it doesn't mean it only applies to expressions containing "A". What the "A" stands for in a rule like A + 1 = 1 is *any* Boolean variable or collection of variables. This is perhaps the most difficult concept for new students to master in Boolean simplification: applying standardized identities, properties, and rules to expressions not in standard form.

For instance, the Boolean expression ABC + 1 also reduces to 1 by means of the "A + 1 = 1" identity. In this case, we recognize that the "A" term in the identity's standard form can represent the entire "ABC" term in the original expression.

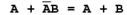

The next rule looks similar to the first one shown in this section, but is actually quite different and requires a more clever proof:

Department of ECS Prepared by Dr. A.SanjayGandhi, Assitant Prof, , KAHE

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

Note how the last rule (A + AB = A) is used to "un-simplify" the first "A" term in the expression, changing the "A" into an "A + AB". While this may seem like a backward step, it certainly helped to reduce the expression to something simpler! Sometimes in mathematics we must take "backward" steps to achieve the most elegant solution. Knowing when to take such a step and when not to is part of the art-form of algebra, just as a victory in a game of chess almost always requires calculated sacrifices.

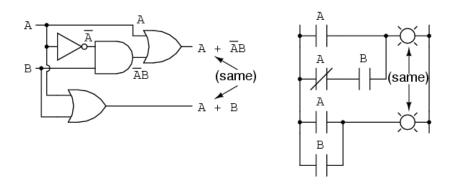

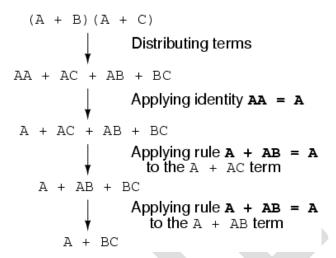

Another rule involves the simplification of a product-of-sums expression:

$$(A + B)(A + C) = A + BC$$

And, the corresponding proof:

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

To summarize, here are the three new rules of Boolean simplification expounded in this section:

### Useful Boolean rules for simplification

$$A + AB = A$$

$A + \overline{A}B = A + B$

$(A + B)(A + C) = A + BC$

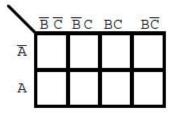

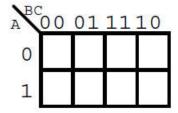

### Karnaugh map

The Karnaugh map, like Boolean algebra, is a simplification tool applicable to digital logic. The Karnaugh Map will simplify logic faster and more easily in most cases.

Boolean simplification is actually faster than the Karnaugh map for a task involving two or fewer Boolean variables. It is still quite usable at three variables, but a bit slower. At four input variables, Boolean algebra becomes tedious. Karnaugh maps are both faster and easier. Karnaugh maps work well for up to six input variables, are usable for up to eight variables. For more than six to eight variables, simplification should be by *CAD* (computer automated design).

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

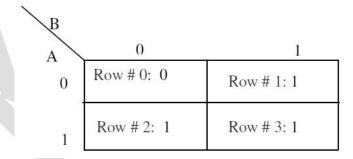

### Relationship between a Karnaugh Map and a Truth Table

Each row in the table (or minterm) is equivalent to a a cell on the Karnaugh Map.

### Example #1:

Here is a two-input truth table for a digital circuit:

### Row Inputs Output

| Row     | Inputs |   | Output |   |

|---------|--------|---|--------|---|

|         | A      | В | F      |   |

| Row # 0 | 0      | 0 | 0      |   |

| Row # 1 | 0      | 1 | 1      | , |

| Row # 2 | 1      | 0 | 1      |   |

| Row # 3 | 1      | 1 | 1      |   |

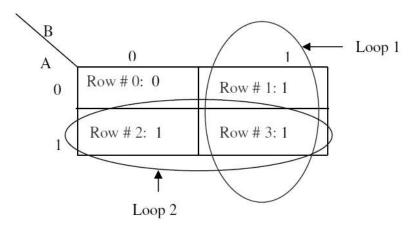

The corresponding K-map is:

### Example #2:

Here is a three-input truth table for a digital circuit:

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

| Row     | Inputs |   |   | Output |

|---------|--------|---|---|--------|

|         | A      | В | C | F      |

| Row # 0 | 0      | 0 | 0 | 0      |

| Row # 1 | 0      | 0 | 1 | 1      |

| Row # 2 | 0      | 1 | 0 | 1      |

| Row # 3 | 0      | 1 | 1 | 1      |

| Row # 4 | 1      | 0 | 0 | 1      |

| Row # 5 | 1      | 0 | 1 | 1      |

| Row # 6 | 1      | 1 | 0 | 0      |

| Row # 7 | 1      | 1 | 1 | 1      |

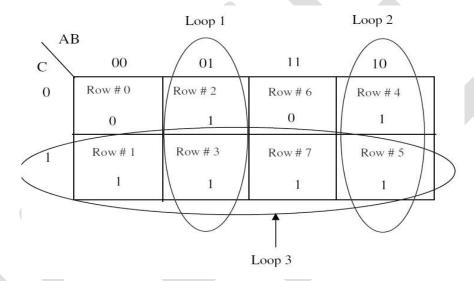

The corresponding K-map is:

| \ AI | 3       |         |         |         |

|------|---------|---------|---------|---------|

| c    | 00      | 01      | 11      | 10      |

| 0    | Row # 0 | Row # 2 | Row# 6  | Row # 4 |

|      | 0       | 1       | 0       | 1       |

| 1    | Row # 1 | Row # 3 | Row # 7 | Row # 5 |

|      | 1       | 1       | 1       | 1       |

### Example #3:

Here is a four-input truth table for a digital circuit:

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

| Row      | Inpu | its | Output |   |   |

|----------|------|-----|--------|---|---|

|          | A    | В   | C      | D | F |

| Row # 0  | 0    | 0   | 0      | 0 | 0 |

| Row # 1  | 0    | 0   | 0      | 1 | 1 |

| Row # 2  | 0    | 0   | 1      | 0 | 1 |

| Row # 3  | 0    | 0   | 1      | 1 | 1 |

| Row # 4  | 0    | 1   | 0      | 0 | 1 |

| Row # 5  | 0    | 1   | 0      | 1 | 1 |

| Row # 6  | 0    | 1   | 1      | 0 | 0 |

| Row # 7  | 0    | 1   | 1      | 1 | 1 |

| Row # 8  | 1    | 0   | 0      | 0 | 1 |

| Row # 9  | 1    | 0   | 0      | 1 | 0 |

| Row # 10 | 1    | 0   | 1      | 0 | 1 |

| Row # 11 | 1    | 0   | 1      | 1 | 1 |

| Row # 12 | 1    | 1   | 0      | 0 | 1 |

| Row # 13 | 1    | 1   | 0      | 1 | 1 |

| Row # 14 | 1    | 1   | 1      | 0 | 1 |

| Row # 15 | 1    | 1   | 1      | 1 | 0 |

The corresponding K-map is:

| \ AI | 3       |         |          |          |

|------|---------|---------|----------|----------|

| CD   | 00      | 01      | 11       | 10       |

| 00   | Row # 0 | Row # 4 | Row # 12 | Row # 8  |

|      | 0       | 1       | 1        | 1        |

| 01   | Row # 1 | Row # 5 | Row # 13 | Row # 9  |

|      | 1       |         | 1        | 0        |

| 11   | Row # 3 | Row # 7 | Row # 15 | Row # 11 |

| 11   | 1       | 1       | 0        | 1        |

| 10   | Row # 2 | Row # 6 | Row # 14 | Row # 10 |

| 10   | 1       | 0 1     | 1        | 1        |

Simplifying Boolean Expressions using Karnaugh map

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

To simplify the resulting Boolean expression using a Karnaugh map adjacent cells containing one are looped together. This step eliminated any terms of the form AA. Adjacent cells means:

- 1. Cells that are side by side in the horizontal and vertical directions (but not diagonal).

- 2. For a map row: the leftmost cell and the rightmost cell.

- 3. For a map column: the topmost cell and the bottom most cell.

- 4. For a 4 variable map: cells occupying the four corners of the map.

Cells may only be looped together in twos, fours, or eights. As few groups as possible must

be formed. Groups may overlap one another and may contain only one cell.

The larger the number of 1s looped together in a group the simpler is the product term that the group represents.

### Example #1:

Simplifying the corresponding K-map of a two-input truth table for a digital circuit:

In Loop 1 the variable A has both logic 0 and logic 1 values in the same loop. B has a value of 1. Hence minterm equation is: F = B.

In Loop 2 Variable B have both logic 0 and 1 values in the same loop. A = 1, hence minterm equation is: F = A.

The overall Boolean expression for F is therefore: F = A + B

### Example #2:

Department of ECS Prepared by Dr. A.SanjayGandhi, Assitant Prof, , KAHE Page 23/45

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

Simplifying the corresponding K-map of a three-input truth table for a digital circuit, In Loop 1 the variable C has both logic 0 and logic 1 values in the same loop. A has a value of 0 and B has a logic value of 1. Hence minterm equation is: F = AB

In Loop 2 the variable C has both logic 0 and 1 values in the same loop. A = 1 and B = 0, hence minterm equation is: F = AB.

In Loop 3 the two variables A and B both have logic 0 and logic 1 values in the same loop. C has a value of 1. Hence minterm equation is: F = C.

The overall Boolean expression for F is therefore: F = AB + AB + C

### Example #3:

Simplifying the corresponding K-map of a four-input truth table for a digital circuit, In Loop 1 the two variables A and D both have logic 0 and logic 1 values in the same loop. C has a value of 0 and B has a value of 1. Hence minterm equation is: F = BC.

In Loop 2 the two variables B and C both have logic 0 and logic 1 values in the same loop. A has a value of 1 and D has a value of 0. Hence minterm equation is: F = AD.

In Loop 3 the variable D has logic 0 and logic 1 values in the same loop. A and B both have a value of 0 and C has a value of 1. Hence minterm equation is: F = ABC.

In Loop 4 the two variables B and C both have logic 0 and logic 1 values in the same loop. A has a value of 0 and D has a value of 1. Hence minterm equation is: F = AD.

Department of ECS Prepared by Dr. A.SanjayGandhi, Assitant Prof, , KAHE Page 24/45

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

In Loop 5 the variable C has logic 0 and logic 1 values in the same loop. A and D both have a value of 1 and B has a value of 0. Hence minterm equation is: F = ABD.

The overall Boolean expression for F is therefore: F = BC + AD + ABC + AD + ABD

### **COMBINATIONAL CIRCUITS**

### HALF ADDER

A key requirement of digital computers is the ability to use logical functions to perform arithmetic operations. The basis of this is addition; if it is possible to add two binary numbers, it is just as easily subtract them, or get a little fancier and perform multiplication and division. Then how to add two binary numbers?

Let's start by adding two binary bits. Since each bit has only two possible values, 0 or 1, there are only four possible combinations of inputs. These four possibilities, and the resulting sums, are:

0 + 0 = 0 0 + 1 = 1 1 + 0 = 11 + 1 = 10

The above fourth line indicates that we have to account for two output bits when we add two input bits: the sum and a possible carry. Let's set this up as a truth table with two inputs and two outputs,

| INP | UTS | OUT<br>UTS | ГР  |

|-----|-----|------------|-----|

| A   | В   | CARRY      | SUM |

| 0   | 0   | 0          | 0   |

| 0   | 1   | 0          | 1   |

| 1   | 0   | 0          | 1   |

| 1   | 1   | 1          | 0   |

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

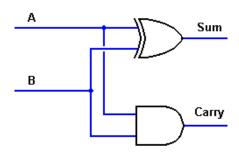

From the above table it is clear that, the Carry output is a simple AND function, and the Sum is an Exclusive-OR. Thus, two gates can be used to add these two bits together. The resulting circuit is shown below.

In a computer, it is very much necessary to add multi-bit numbers together. If each pair of bits can produce an output carry, it must also be able to recognize and include a carry from the next lower order of magnitude. This is the same requirement as adding decimal numbers -- if you have a carry from one column to the next; the next column has to include that carry. We have to do the same thing with binary numbers, for the same reason. As a result, the circuit to the left is known as a "half adder," because it only does half of the job. There is need a circuit that will do the entire job.

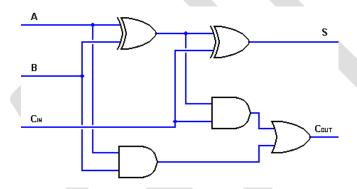

To construct a full adder circuit, we'll need three inputs and two outputs. Since we'll have both an input carry and an output carry, we'll designate them as  $C_{\rm IN}$  and  $C_{\rm OUT}$ . At the same time, we'll use S to designate the final Sum output. The resulting truth table is shown below.

| I | NPU | JTS             | OUTPU | TS |

|---|-----|-----------------|-------|----|

| A | В   | C <sub>IN</sub> | Cout  | S  |

| 0 | 0   | 0               | 0     | 0  |

| 0 | 0   | 1               | 0     | 1  |

| 0 | 1   | 0               | 0     | 1  |

| 0 | 1   | 1               | 1     | 0  |

| 1 | 0   | 0               | 0     | 1  |

| 1 | 0   | 1               | 1     | 0  |

| 1 | 1   | 0               | 1     | 0  |

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

| 1 1 1 | 1 | 1 |

|-------|---|---|

|-------|---|---|

This is looking a bit messy. It looks as if  $C_{OUT}$  may be either an AND or an OR function, depending on the value of A, and S is either an XOR or an XNOR, again depending on the value of A. Looking a little more closely, however, we can note that the S output is actually an XOR between the A input and the half-adder SUM output with B and  $C_{IN}$  inputs. Also, the output carry will be true if any two or all three inputs are logic 1.

What this suggests is also intuitively logical: we can use two half-adder circuits. The first will add A and B to produce a partial Sum, while the second will add  $C_{\rm IN}$  to that Sum to produce the final S output. If either half-adder produces a carry, there will be an output carry. Thus,  $C_{\rm OUT}$  will be an OR function of the half-adder Carry outputs. The resulting full adder circuit is shown below.

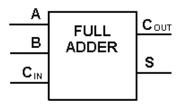

The circuit above is really too complicated to be used in larger logic diagrams, so a separate symbol, shown below, is used to represent a one-bit full adder. In fact, it is common practice in logic diagrams to represent any complex function as a "black box" with input and output signals designated. It is, after all, the logical function that is important, not the exact method of performing that function.

### HALF SUBTRACTOR

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT: I (Logic Gates) BATCH-2018-2019

We have seen how simple logic gates can perform the process of binary addition. It is only logical to assume that a similar circuit could perform binary subtraction.

If we look at the possibilities involved in subtracting one 1-bit number from another, we can quickly see that three of the four possible combinations are easy and straightforward. The fourth one involves a bit more:

0 - 0 = 0

1 - 0 = 1

1 - 1 = 0

0 - 1 = 1, with a borrow bit.

That borrow bit is just like a borrow in decimal subtraction: it subtracts from the next higher order of magnitude in the overall number. Let's see what the truth table looks like.

| INP | UTS | OUTPU  | TS    |

|-----|-----|--------|-------|

| A   | В   | BORROW | A - B |

| 0   | 0   | 0      | 0     |

| 0   | 1   | 1      | 1     |

| 1   | 0   | 0      | 1     |

| 1   | 1   | 0      | 0     |

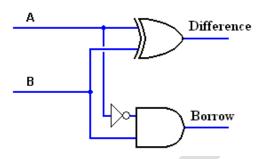

This is an interesting result. The difference, A-B, is still an Exclusive-OR function, just as the sum was for addition. The borrow is still an AND function, but is A'B instead of AB.

What we'd like to do, now, is find an easy way to use the binary adder to perform subtraction as well. We already have half of it working: the difference output. Can we simply invert the A input so the AND gate will have the right signals? No, we can't, because that would invert the sense of the Exclusive-OR function.

What would be really nice is to convert B to the negative equivalent of its value, and then use the basic adder just as it stands. To see if we can do that, let's consider negative binary numbers below.

The half adder circuit can be designed as designed as follows,

Department of ECS Prepared by Dr. A.SanjayGandhi, Assitant Prof, , KAHE Page 28/45

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

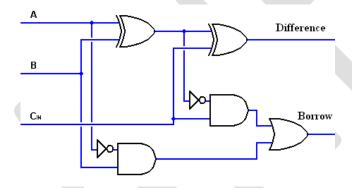

As like as the normal subtraction it is possible to perform the subtraction between three binary numbers. It is necessary since when multi-bit subtraction is going to be performed the borrow will be transferred to the next bit subtraction on some occasions. The full subtractor circuit is show in the below figure.

The input and output of the full subtractor is given below as a truth table,

|   | INP | PUTS               | OUTPU   | TS   |

|---|-----|--------------------|---------|------|

| A | В   | Borr <sub>IN</sub> | Borrout | Diff |

| 0 | 0   | 0                  | 0       | 0    |

| 0 | 0   | 1                  | 0       | 1    |

| 0 | 1   | 0                  | 0       | 1    |

| 0 | 1   | 1                  | 1       | 0    |

| 1 | 0   | 0                  | 0       | 1    |

| 1 | 0   | 1                  | 1       | 0    |

| 1 | 1   | 0                  | 1       | 0    |

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

| 1 | 1 | 1 | 1 | 1 |

|---|---|---|---|---|

|---|---|---|---|---|

### **MULTIPLEXER**

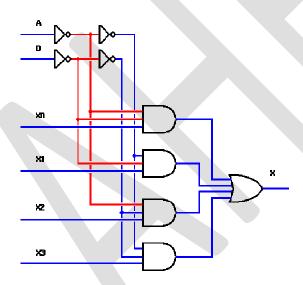

One circuit I've received a number of requests for is the *multiplexer* circuit. This is a digital circuit with multiple signal inputs, one of which is selected by separate address inputs to be sent to the single output. It's not easy to describe without the logic diagram, but is easy to understand when the diagram is available.

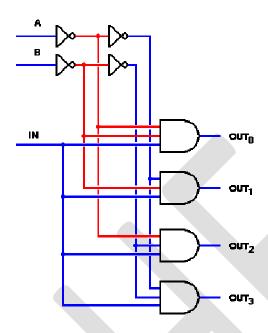

The 4x1 multiplexer circuit is shown in the below figure,

The multiplexer circuit is typically used to combine two or more digital signals onto a single line, by placing them there at different times. Technically, this is known as *time-division multiplexing*.

Input A is the addressing input, which controls which of the two data inputs, X0 or X1, will be transmitted to the output. If the A input switches back and forth at a frequency more than double the frequency of either digital signal, both signals will be accurately reproduced, and can be separated again by a *Demultiplexer* circuit synchronized to the multiplexer.

This is not as difficult as it may seem at first glance; the telephone network combines multiple audio signals onto a single pair of wires using exactly this technique, and is readily able to separate many telephone conversations so that everyone's voice goes only to the

Department of ECS Prepared by Dr. A.SanjayGandhi, Assitant Prof, , KAHE Page 30/45

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

intended recipient. With the growth of the Internet and the World Wide Web, most people have heard about T1 telephone lines. A T1 line can transmit up to 24 individual telephone conversations by multiplexing them in this manner.

Very common application for this type of circuit is found in computers, where dynamic memory uses the same address lines for both row and column addressing. A set of multiplexers is used to first select the row address to the memory, then switch to the column address. This scheme allows large amounts of memory to be incorporated into the computer while limiting the number of copper traces required to connect that memory to the rest of the computer circuitry. In such an application, this circuit is commonly called a *data selector*.

Multiplexers are not limited to two data inputs. If we use two addressing inputs, we can multiplex up to four data signals. With three addressing inputs, we can multiplex eight signals. If you would like to see a demonstration of a four-input multiplexer.

### DEMULTIPLEXER/DECODER

The opposite of the multiplexer circuit, logically enough, is the *demultiplexer*. This circuit takes a single data input and one or more address inputs, and selects which of multiple outputs will receive the input signal. The same circuit can also be used as a *decoder*, by using the address inputs as a binary number and producing an output signal on the single output that matches the binary address input. In this application, the data input line functions as a circuit enabler — if the circuit is disabled, no output will show activity regardless of the binary input number.

This circuit uses the same AND gates and the same addressing scheme as the two-input multiplexer circuit shown in these pages. The basic difference is that it is the inputs that are combined and the outputs that are separate. By making this change, we get a circuit that is the inverse of the two-input multiplexer. If you were to construct both circuits on a single breadboard, connect the multiplexer output to the data IN of the Demultiplexer, and drive the Address inputs of both circuits with the same signal, you would find that the initial X0 input would be transmitted to  $OUT_0$  and the X1 input would reach only  $OUT_1$ .

The one problem with this arrangement is that one of the two outputs will be inactive while the other is active. To retain the output signal, we need to add a latch circuit that can follow the data signal while it's active, but will hold the last signal state while the other data signal is active. An excellent circuit for this is the D (or Data) Latch. By placing a latch after each output and using the Addressing input (or its inverse) to control them, we can maintain both output signals at all times. If the Address input changes much more rapidly than the data inputs, the output signals will match the inputs faithfully.

A 2-to-4 line decoder/Demultiplexer is shown below.

Department of ECS Prepared by Dr. A.SanjayGandhi, Assitant Prof, , KAHE Page 31/45

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT: I (Logic Gates) BATCH-2018-2019

Like the multiplexer circuit, the decoder/Demultiplexer is not limited to a single address line, and therefore can have more than two outputs. With two, three, or four addressing lines, this circuit can decode a two, three, or four-bit binary number, or can Demultiplexer up to four, eight, or sixteen time-multiplexed signals.

As a decoder, this circuit takes an n-bit binary number and produces an output on one of  $2^n$  output lines. It is therefore commonly defined by the number of addressing input lines and the number of data output lines. Typical decoder/Demultiplexer ICs might contain two 2-to-4 line circuits, a 3-to-8 line circuit, or a 4-to-16 line circuit. One exception to the binary nature of this circuit is the 4-to-10 line decoder/Demultiplexer, which is intended to convert a BCD (Binary Coded Decimal) input to an output in the 0-9 range.

If you use this circuit as a Demultiplexer, you may want to add data latches at the outputs to retain each signal while the others are being transmitted. However, this does not apply when you are using this circuit as a decoder — then you will want only a single active output to match the input code.

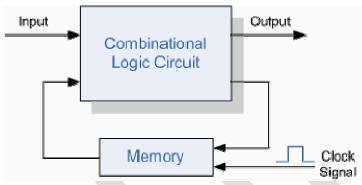

### **Sequential Logic Basics**

Unlike Combinational Logic circuits that change state depending upon the actual signals being applied to their inputs at that time, Sequential Logic circuits have some form of inherent "Memory" built in to them and they are able to take into account their previous input state as well as those actually present, a sort of "before" and "after" is involved. They are generally

Department of ECS Prepared by Dr. A.SanjayGandhi, Assitant Prof., KAHE Page 32/45

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

termed as Two State or Bistable devices which can have their output set in either of two basic states, a logic level "1" or a logic level "0" and will remain "latched" indefinitely in this current state or condition until some other input trigger pulse or signal is applied which will cause it to change its state once again.

### **Sequential Logic Circuit**

The word "Sequential" means that things happen in a "sequence", one after another and in Sequential Logic circuits, the actual clock signal determines when things will happen next. Simple sequential logic circuits can be constructed from standard Bistable circuits such as Flipflops, Latches or Counters and which themselves can be made by simply connecting together NAND Gates and/or NOR Gates in a particular combinational way to produce the required sequential circuit.

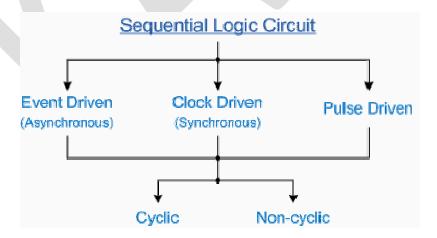

### **Classification of Sequential Logic**

As well as the two logic states mentioned above logic level "1" and logic level "0", a third element is introduced that separates Sequential Logic circuits from their Combinational Logic

Department of ECS Prepared by Dr. A.SanjayGandhi, Assitant Prof, , KAHE Page 33/45

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102

COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

counterparts, namely TIME. Sequential logic circuits that return back to their original state once reset, i.e. circuits with loops or feedback paths are said to be "Cyclic" in nature.

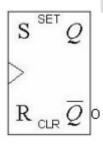

### Flip-Flops

Flip-flops are synchronous bistable devices. The term synchronous means the output changes state only when the clock input is triggered. That is, changes in the output occur in synchronization with the clock.

Flip-flop is a kind of multivibrator. There are three types of multivibrators:

- 1. Monostable multivibrator (also called one-shot) has only one stable state. It produces a single pulse in response to a triggering input.

- 2. Bistable multivibrator exhibits two stable states. It is able to retain the two SET and RESET states indefinitely. It is commonly used as a basic building block for counters, registers and memories.

- 3. A stable multivibrator has no stable state at all. It is used primarily as an oscillator to generate periodic pulse waveforms for timing purposes.

### **Edge-Triggered Flip-flops**

An edge-triggered flip-flop changes states either at the positive edge (rising edge) or at the negative edge (falling edge) of the clock pulse on the control input. The three basic types are introduced here: S-R, J-K and D.

The S-R, J-K and D inputs are called synchronous inputs because data on these inputs are transferred to the flip-flop's output only on the triggering edge of the clock pulse. On the other hand, the direct set (SET) and clear (CLR) inputs are called asynchronous inputs, as they are inputs that affect the state of the flip-flop independent of the clock. For the synchronous operations to work properly, these asynchronous inputs must both be kept LOW.

### **Edge-triggered J-K flip-flop**

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

The J-K flip-flop works very similar to S-R flip-flop. The only difference is that this flip-flop has NO invalid state. The outputs toggle (change to the opposite state) when both J and K inputs are HIGH. The truth table is shown below.

|          | outs | Out |   | Inputs |   |

|----------|------|-----|---|--------|---|

| Comment  | Q'   | Q   | C | К      | J |

| No chang | Q′   | Q   | 1 | 0      | 0 |

| RESET    | 1    | 0   | 1 | 1      | 0 |

| SET      | 0    | 1   | 1 | 0      | 1 |

| Toggle   | Q    | Q,  | 1 | 1      | 1 |

### **Edge-triggered D flip-flop**

The operations of a D flip-flop is much more simpler. It has only one input addition to the clock. It is very useful when a single data bit (0 or 1) is to be stored. If there is a HIGH on the D input when a clock pulse is applied, the flip-flop SETs and stores a 1. If there is a LOW on the D input when a clock pulse is applied, the flip-flop RESETs and stores a 0. The truth table below summarize the operations of the positive edge-triggered D flip-flop. As before, the negative edge-triggered flip-flop works the same except that the falling edge of the clock pulse is the triggering edge.

|          | outs | Out | uts | Inp |

|----------|------|-----|-----|-----|

| Comments | Q'   | Q   | С   | D   |

| RESET    | 1    | 0   | 1   | 0   |

| SET      | 0    | 1   | 1   | 1   |

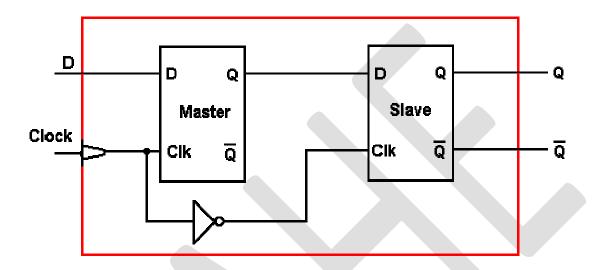

### Pulse-Triggered (Master-Slave) Flip-flops

The term pulse-triggered means that data are entered into the flip-flop on the rising edge of the clock pulse, but the output does not reflect the input state until the falling edge of the clock pulse. As this kind of flip-flops are sensitive to any change of the input levels during the clock pulse is still HIGH, the inputs must be set up prior to the clock pulse's rising edge and must not be changed before the falling edge. Otherwise, ambiguous results will happen.

The three basic types of pulse-triggered flip-flops are S-R, J-K and D. Their logic symbols are shown below. Notice that they do not have the dynamic input indicator at the clock input but have postponed output symbols at the outputs.

The truth tables for the above pulse-triggered flip-flops are all the same as that for the edge-triggered flip-flops, except for the way they are clocked. These flip-flops are also called Master-Slave flip-flops simply because their internal construction are divided into two sections.

Department of ECS Prepared by Dr. A.SanjayGandhi, Assitant Prof, , KAHE Page 35/45

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

The slave section is basically the same as the master section except that it is clocked on the inverted clock pulse and is controlled by the outputs of the master section rather than by the external inputs. The logic diagram for a basic master-slave S-R flip-flop is shown below.

The master/slave flip-flop overcomes the following problems.

- ✓ RIPPLE THROUGH. An input changes level during the clock period, and the change appears at the output.

- ✓ PROPAGATION DELAY. The time between applying a signal to an input, and the resulting change in the output.

These can give problems in logic circuits. The maste/slave flipflop consists of two rising edge triggered D type flip-flops. The clock of the slave is fed via an inverter so that the falling edge of the origonal clock pulse becomes a rising edge. The slave clock pulse is an inverted version of the clock pulse shown in the lower diagram. The flip-flops are triggered at different levels of the clock pulse edge. When data is to be entered, the slave is isolated from the master, so that changes at the input do not appear at the output.Data on D is passed to Q of the master. The master is then isolated from the D input. Data, from the Q of the master, is passed to Q of the slave.

- t1. Slave isolated from Master.

- t2. Master connected to D input.

- t3. Master isolated from D input.

- t4. Master Q connected Slave D.

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT: I (Logic Gates) BATCH-2018-2019

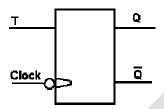

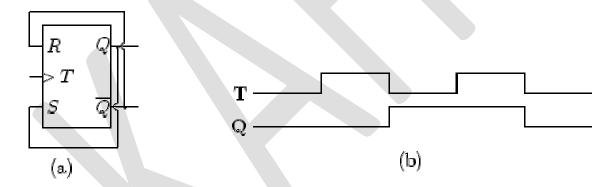

# **Toggle Flip-Flop (T)**

This flip-flop toggles (Q changes state) on the negative going edge of the clock pulse. T acts as an ENABLE / INHIBIT control. Q will only toggle on the negative edge of the clock pulse, when T is high. Below is shown a D type flip-flop connected as a toggle type. On each clock pulse positive going edge, Q will go to the state bar Q was before the clock pulse arrived. Remember that bar Q is the opposite level to Q. Therefore Q will toggle. This type of flip-flop is a simplified version of the JK flip-flop. It is not usually found as an IC chip by itself, but is used in many kinds of circuits, especially counter and dividers. Its only function is that it toggles itself with every clock pulse (on either the leading edge, on the trailing edge) it can be constructed from the RS flip-flop as shown in Figure (a).

This flip flop is normally set, or 'loaded" with the preset and clear inputs. It can be used to obtain an output pulse train with a frequency of half that of the clock pulse train, as seen from the timing diagram, Figure (b). In this example, the T flip flop is triggered on the falling edge of the clock pulse. Several T flip-flops are often connected together in a simple IC to form a 'divide by N" counter, where N is usually 5, 10, 12 or a power of 2.

### **Overall Behavior**

Each flip-flop stores a single bit of data, which is emitted through the Q output on the east side. Normally, the value can be controlled via the inputs to the west side. In particular, the value

Department of ECS Prepared by Dr. A.SanjayGandhi, Assitant Prof., KAHE Page 37/45

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

changes when the **clock** input, marked by a triangle on each flip-flop, rises from 0 to 1; on this rising edge, the value changes according to the corresponding table below.

D Flip-Flop T Flip-Flop J-K Flip-Flop S-R Flip-Flop

| DQ  | TQ           | JKQ               | SRQ    |

|-----|--------------|-------------------|--------|

| 0 0 | 0 Q          | $0~0~\mathcal{Q}$ | 0~0~Q  |

| 1 1 | 1 <i>Q</i> ' | 0 1 0             | 0 1 0  |

|     |              | 1 0 1             | 1 0 1  |

|     |              | 1 1 <i>Q</i> '    | 1 1 ?? |

Another way of describing the different behavior of the flip-flops is as follows:

- **D Flip-Flop:** When the clock rises from 0 to 1, the value remembered by the flip-flop becomes the value of the *D* input (*Data*) at that instant.

- **T Flip-Flop:** When the clock rises from 0 to 1, the value remembered by the flip-flop either toggles or remains the same depending on whether the *T* input (*Toggle*) is 1 or 0.

- **J-K Flip-Flop:** When the clock rises from 0 to 1, the value remembered by the flip-flop toggles if the *J* and *K* inputs are both 1, remains the same if they are both 0, and changes to the *K* input value if *J* and *K* are not equal. (The names *J* and *K* do not stand for anything.)

- **R-S Flip-Flop:** When the clock rises from 0 to 1, the value remembered by the flip-flop remains unchanged if R and S are both 0, becomes 0 if the R input (Reset) is 1, and becomes 1 if the S input (Set) is 1. The behavior in unspecified if both inputs are 1. (In Logisim, the value in the flip-flop remains unchanged.)

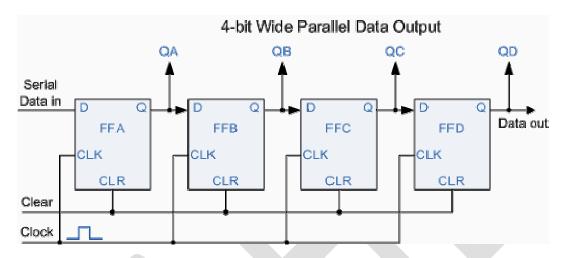

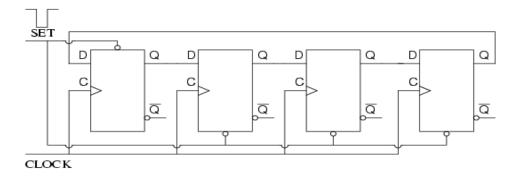

# **Shift Registers**

Shift Registers consists of a number of single bit "D-Type Data Latches" connected together in a chain arrangement so that the output from one data latch becomes the input of the next latch and so on, thereby moving the stored data serially from either the left or the right direction. The number of individual Data Latches used to make up Shift Registers are determined by the number of bits to be stored. The most common used is 8-bits wide. Shift Registers are mainly used to store data and to convert data from either a serial to parallel or parallel to serial format with all the latches being driven by a common clock (Clk) signal making them Synchronous devices. They are generally provided with a Clear or Reset connection so that they can be "SET" or "RESET" as required.

Generally, Shift Registers operate in one of four different modes:

Serial-in to Parallel-out (SIPO)

Department of ECS Prepared by Dr. A.SanjayGandhi, Assitant Prof., KAHE

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

- Serial-in to Serial-out (SISO)

- ➤ Parallel-in to Parallel-out (PIPO)

- ➤ Parallel-in to Serial-out (PISO)

#### Serial-in to Parallel-out.

Fig: 4-bit Serial-in to Parallel-out (SIPO) Shift Register

Lets assume that all the flip-flops (FFA to FFD) have just been RESET (CLEAR input) and that all the outputs QA to QD are at logic level "0" ie, no parallel data output. If a logic "1" is connected to the DATA input pin of FFA then on the first clock pulse the output of FFA and the resulting QA will be set HIGH to logic "1" with all the other outputs remaining LOW at logic "0". Assume now that the DATA input pin of FFA has returned LOW to logic "0". The next clock pulse will change the output of FFA to logic "0" and the output of FFB and QB HIGH to logic "1". The logic "1" has now moved or been "Shifted" one place along the register to the right. When the third clock pulse arrives this logic "1" value moves to the output of FFC (QC) and so on until the arrival of the fifth clock pulse which sets all the outputs QA to QD back again to logic level "0" because the input has remained at a constant logic level "0".

The effect of each clock pulse is to shift the DATA contents of each stage one place to the right, and this is shown in the following table until the complete DATA is stored, which can now be read directly from the outputs of QA to QD. Then the DATA has been converted from a Serial Data signal to a Parallel Data word.

| Clock Pulse No | QA | QB | QC | QD |

|----------------|----|----|----|----|

| 0              | 0  | 0  | 0  | 0  |

| 1              | 1  | 0  | 0  | 0  |

| 2              | 0  | 1  | 0  | 0  |

Department of ECS Prepared by Dr. A.SanjayGandhi, Assitant Prof, , KAHE

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

| 3 | 0 | 0 | 1 | 0 |

|---|---|---|---|---|

| 4 | 0 | 0 | 0 | 1 |

| 5 | 0 | 0 | 0 | 0 |

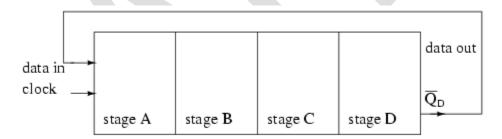

#### Serial-in to Serial-out

This Shift Register is very similar to the one above except where as the data was read directly in a parallel form from the outputs QA to QD, this time the DATA is allowed to flow straight through the register. Since there is only one output the DATA leaves the shift register one bit at a time in a serial pattern and hence the name Serial-in to Serial-Out Shift Register.

Fig: 4-bit Serial-in to Serial-out (SISO) Shift Register

This type of Shift Register also acts as a temporary storage device or as a time delay device, with the amount of time delay being controlled by the number of stages in the register, 4, 8, 16 etc or by varying the application of the clock pulses. Commonly available IC's include the 74HC595 8-bit Serial-in/Serial-out Shift Register with 3-state outputs.

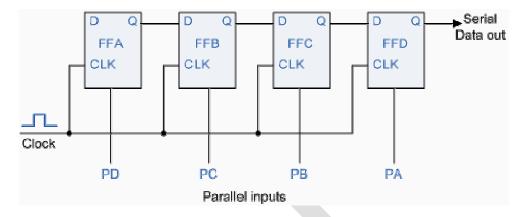

### Parallel-in to Serial-out

Parallel-in to Serial-out Shift Registers act in the opposite way to the Serial-in to Parallel-out one above. The DATA is applied in parallel form to the parallel input pins PA to PD of the register and is then read out sequentially from the register one bit at a time from PA to PD on each clock cycle in a serial format.

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

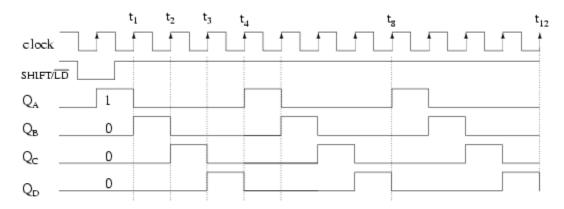

Fig: 4-bit Parallel-in to Serial-out (PISO) Shift Register

As this type of Shift Register converts parallel data, such as an 8-bit data word into serial data it can be used to multiplex many different input lines into a single serial DATA stream which can be sent directly to a computer or transmitted over a communications line. Commonly available IC's include the 74HC165 8-bit Parallel-in/Serial-out Shift Registers.

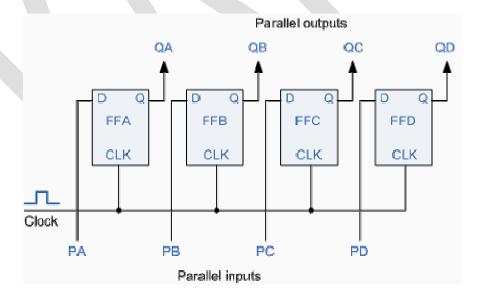

#### Parallel-in to Parallel-out

Parallel-in to Parallel-out Shift Registers also act as a temporary storage device or as a time delay device. The DATA is presented in a parallel format to the parallel input pins PA to PD and then shifts it to the corresponding output pins QA to QD when the registers are clocked.

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

Fig: 4-bit Parallel-in/Parallel-out (PIPO) Shift Register

As with the Serial-in to Serial-out shift register, this type of register also acts as a temporary storage device or as a time delay device, with the amount of time delay being varied by the frequency of the clock pulses.

Today, high speed bi-directional universal type Shift Registers such as the TTL 74LS194, 74LS195 or the CMOS 4035 are available as a 4-bit multi-function devices that can be used in serial-serial, shift left, shift right, serial-parallel, parallel-serial, and as a parallel-parallel Data Registers, hence the name "Universal".

## **COUNTERS**

# Ring counters

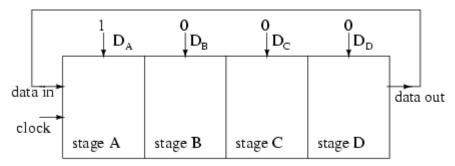

If the output of a shift register is fed back to the input. a ring counter results. The data pattern contained within the shift register will recirculate as long as clock pulses are applied. For example, the data pattern will repeat every four clock pulses in the figure below. However, we must load a data pattern. All 0's or all 1's doesn't count. Is a continuous logic level from such a condition useful?

Ring Counter, shift register output fed back to input

We make provisions for loading data into the parallel-in/ serial-out shift register configured as a ring counter below. Any random pattern may be loaded. The most generally useful pattern is a single 1.

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

Parallel-in, serial-out shift register configured as a ring counter

Loading binary 1000 into the ring counter, above, prior to shifting yields a viewable pattern. The data pattern for a single stage repeats every four clock pulses in our 4-stage example. The waveforms for all four stages look the same, except for the one clock time delay from one stage to the next. See figure below.

Load 1000 into 4-stage ring counter and shift

The circuit above is a divide by 4 counter. Comparing the clock input to any one of the outputs, shows a frequency ratio of 4:1. How may stages would we need for a divide by 10 ring counter? Ten stages would recirculate the 1 every 10 clock pulses.

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

Set one stage, clear three stages

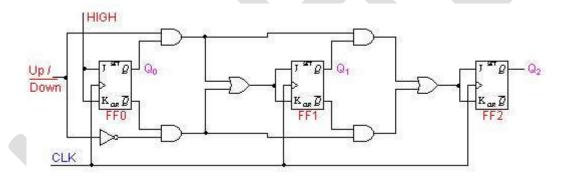

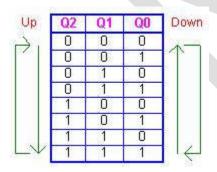

# **Up-Down Counters**

A circuit of a 3-bit synchronous up-down counter and a table of its sequence are shown below. Similar to an asynchronous up-down counter, a synchronous up-down counter also has an up-down control input. It is used to control the direction of the counter through a certain sequence.

An examination of the sequence table shows:

- for both the UP and DOWN sequences, Q0 toggles on each clock pulse.

- for the UP sequence, Q1 changes state on the next clock pulse when Q0=1.

- for the DOWN sequence, Q1 changes state on the next clock pulse when Q0=0.

- for the UP sequence, Q2 changes state on the next clock pulse when Q0=Q1=1.

- for the DOWN sequence, Q2 changes state on the next clock pulse when Q0=Q1=0.

CLASS: I B.Sc., CS, IT, CA& CT COURSECODE: 18CSU102 COURSE NAME: Computer Systems Architecture UNIT:I (Logic Gates) BATCH-2018-2019

# **Possible Question**

|                        |                  | PART              | $\Gamma - \mathbf{A}$ |                |

|------------------------|------------------|-------------------|-----------------------|----------------|

| 1. Flip-Flop is a      | bit register.    |                   |                       |                |

| a. 1                   | b.3              | c.2               | d.4                   |                |

| 2. Combinational circ  | cuits output der | ends the          |                       |                |

| a. present input       |                  |                   | c. past output        | d.future input |

| 3. Boolean Algebra A   | -                | 1 1               | 1                     | 1              |

| a. 0 b. 1              |                  | d. A              | ,                     |                |

| 4. Sequential circuits |                  | s only the        |                       |                |

| a. present input       |                  | -                 | c. past output        | d.future input |

| 5. What is the base m  | -                | -                 |                       |                |

| a. 2 b. 4              | c. 8             | d.16              |                       |                |

| 6. What is the one's o | complement of    | (1011110)2        |                       |                |

| a. 0100001             | b. 0111101       |                   | 010000                | d. 0001110     |

| 7. Convert (255)10 to  | binary numbe     |                   |                       |                |

| a. 111111110           |                  |                   | 01010101              | d. 010101010   |

| 8. Signed number is u  | used to indicate |                   |                       |                |

| a. negative b. p       |                  |                   |                       |                |

| 9. When the CPU de     | •                | _                 |                       |                |

| a. previous state      |                  |                   |                       |                |

| 10. A microprogram     |                  |                   |                       |                |

| a. read                | b. write         | c. read and       |                       | and execute    |

|                        |                  |                   |                       |                |

|                        |                  | PART              | $\Gamma - \mathbf{B}$ |                |

|                        |                  |                   |                       |                |

| 1. Define Flip-Flop.   |                  |                   |                       |                |

| 2. Convert the binary  | number (1011     | $101)_2$ into dec | cimal number.         |                |

| 3. Define combination  |                  |                   |                       |                |

### PART-C

- 1. Discuss in detail Boolean properties with an example.

- 2. Explain in detail 4:1 multiplexer with neat diagram.

- 3. Discuss in detail shift registers with an example.

- 4. Explain in detail 8:1 multiplexer with neat diagram.

4. Convert the binary number (101110101000010101)<sub>2</sub> into octel number.

# Karpagam Academy of Higher Education COIMBATORE - 641021

Name of the Faculty : **K. Subramanian**

Department : Electronics and Communication Systems

Subject & Subject Code : Computer Systems Architecture & 17CSU102/17CTU

Class : I B.Sc. (CT, CS-B)

Year and Semester : 2017 – 2018 and I semester

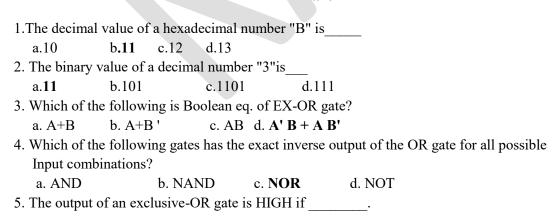

| QUESTION                                             | OPT 1 | OPT 2 | OPT 3  |

|------------------------------------------------------|-------|-------|--------|

| UNIT I                                               |       |       |        |

| The radix of a decimal number is                     | 2     | 8     | 10     |

| The radix of an octal number is                      | 2     | 8     | 10     |

| The base of a binary number is                       | 2     | 8     | 10     |

| The base of a hexa decimal number is                 | 2     | 8     | 10     |

| Thr single digit value in digital system is known as | Bit   | Byte  | Nibble |

| A 4-bit value is known as in a digital systems       | Bit   | Byte  | Nibble |

| A 8-bit value is known as in a digital systems       | Bit   | Byte  | Nibble |

| A 16-bit value is known as in a digital systems      | Bit   | Byte  | Nibble |

| The binary value of hexadecimal number "A"is         | 1010  | 1111  | 1110   |

| The decimal value of a binary number 0101 is         | 8     | 7     | 9      |

| The octal value of a binary number 0111 is           | 4     | 5     | 6      |

| The hexadecimal value of a decimal number 15 is      | 1010  | 1110  | 1011   |

| The decimal value of a hexadecimal number "B" is     | 10    | 11    | 12     |

|                                                  |        | 1       |        |

|--------------------------------------------------|--------|---------|--------|

| The binary value of a decimal number "3"is       | 11     | 101     | 1101   |

|                                                  | 11     | 101     | 1101   |

| The octal value of a decimal number 444          | 534    | 356     | 636    |

|                                                  |        | 330     | 030    |

| The hexadecimal value of a binary number 1110 is | _      | D       | E      |

|                                                  | A      |         | E      |

| The decimal value of a hexadecimal number "D" is | 11     | 12      | 13     |

| The decimal value of a binary numbe 1001         | 9      | 10      | 8      |

|                                                  | 9      | 10      | 0      |

| The decimal value of an octal number 237         | 160    | 159     | 158    |

|                                                  | 100    | 139     | 136    |

| The hexadecimal value of a decimal               | AF     | <br> 4B | 84     |

| nymber115 is                                     | Ar     | 4D      | 04     |

| The octal value of a hexadecimal number 47       | 66     | 215     | 107    |

|                                                  | 00     | 213     | 107    |

| The hexadecimal value of an octal number 32 is   | 5A     | 3A      | 4A     |

| The decimal value of a binary number             |        |         |        |

| 101111 is                                        | 47     | 74      | 64     |

| The octal value of a binary number 1001010       |        |         |        |

| is                                               | 111    | 112     | 113    |

| The decimal value of a binary number 10110       |        |         |        |

| is                                               | 22     | 24      | 23     |

| The binary value of an octal number 27           |        |         |        |

| is                                               | 100110 | 110101  | 10111  |

| The decimal value of a hexadecimal number        |        |         |        |

| E9 is                                            | 233    | 234     | 255    |

| The hexadecimal value of binary number           |        |         |        |

| 1101110 is                                       | 4E     | 3D      | 6E     |

|                                                  |        |         |        |

| The 1's complement value of 11011 is             | 1101   | 11011   | 00100  |

|                                                  |        |         |        |

| The 1's complement value of 101101 is            | o10010 | 001110  | 111010 |

|                                                  |        |         |        |

| The 2's complement value of 11011 is             | 11010  | 11101   | 10101  |

|                                                  |        |         |        |

| The 2's complement value of ooo1o is             | 11101  | 11110   | 10101  |

|                                                            |                         | Ī                                |                                |

|------------------------------------------------------------|-------------------------|----------------------------------|--------------------------------|

| The 1's complement value of 1010 is                        | 1010                    | 1100                             | 101                            |

| Expansion of BCD is                                        | Binary Coder<br>Decoder | Complement Decimal               | Binary Coded<br>Decimal        |

| 8421 code is a type of code                                | Excess 3                | BCD                              | Gray                           |

| What is the weight of binary digit 1001 using 8421 code    | 6                       | 9                                | 13                             |

| Convert the decimal number 170 to BCD                      | 1101 0111 0000          | 1010 0101 0000                   | 0001 0111<br>0000              |

| The expansion of ASCII is                                  | Cod for information     | standard code<br>for information | symbol code<br>for Information |